# Integration Platform for Tunable Carbon Nanotube Electromechanical Resonators

A dissertation submitted to

ETH Zurich

for the degree of

**Doctor of Sciences**

presented by

Shih-Wei Lee

MSc ME, NTHU

born October 27, 1980

citizen of Taiwan, Republic of China

accepted on the recommendation of Prof. Dr. Christofer Hierold, examiner Prof. Dr. Nico de Rooij, co-examiner If you are a superman, you don't need to swing like a spiderman. What you need to do is fly freely in the air. Be your superman.

My life reminder

### Abstract

Carbon nanotubes (CNTs) possess several outstanding material properties, such as high stiffness, light weight, and one-dimensional structures. These are key factors for high resonant frequency of a vibration structure. Hence, CNTs are promising nano-materials for high frequency resonators. Moreover, the already high resonant frequency of a suspended CNT can be further increased by applying strain. Micro-actuation by a MEMS actuator can reduce the slack of the suspended CNT and increase strain upon the CNT, which enables a broad tunable frequency range from MHz to GHz. In this study, a scalable CNT-MEMS integration platform was developed, and the first tunable CNT resonator with an embedded MEMS actuation system was demonstrated.

To integrate a low-defect suspended CNT into a pre-defined MEMS actuator, a fabrication process has been developed. Using top-down micro-machining, a temporary supporting structure is fabricated so as to avoid physical rupture of suspended CNTs during wet processing. In addition, an Al<sub>2</sub>O<sub>3</sub> layer is deposited by atomic layer deposition (ALD) to protect as-grown CNTs from resist contamination during post-growth processing. The post-growth wet processing enables the metallization on top of as-grown CNTs by lift-off. The patterned metals provide improved electrical contacts and robust doubly-clamped configuration. Based on the developed integration process, the influence of processing conditions on CNT performance and the long-term stability of device resistance were investigated.

To adjust the strain on the integrated CNT, a micro-actuation system was designed. The system was driven by an electro-thermal bent-beam actuator. To avoid electrical and thermal interferences between the actuator and CNT device, an insulation mechanical configuration, called adapter, was designed. This adapter is compact, and it consists of only two discrete silicon structures. More importantly, it can be fabricated using the developed integration process. This adapter can electro-thermally insulate the CNT from the actuator, while the CNT is strained by the actuator. Hence, the investigation the CNT electrical response to strain is possible.

The entire integrated CNT-MEMS device, including. a suspended CNT, an adapter, and a thermal actuator, can be fabricated using the developed integration process. The functionality of the fabricated CNT-MEMS device was first verified by quasi-static

electromechanical loading tests. The electrical current variations of the strained CNTs were measured during the tensile tests. The reproducible and reversible strain-induced current modulation of the tested CNTs confirms the device functionality. In the final dynamic characterization, the resonant frequency of the suspended CNT was tuned by driving the actuator. The frequency modulation mechanism was attributed to the reduction of the slack of the CNT. This demonstrates a tunable CNT resonator and confirms the capability of the integration platform.

## Zusammenfassung

Kohlenstoffnanoröhren (CNTs) besitzen viele herausragende Materialeigenschaften, wie z.B. hohe Steifigkeit, geringes Gewicht und eine eindimensionale Struktur. Diese sind Schlüsselfaktoren für hohe Resonanzfreqenzen einer schwingenden Struktur. Daher sind CNTs vielversprechende Nanomaterialien für Hochfrequenzresonatoren. Ausserdem kann die Resonanzfrequenz einer freihängenden CNT durch Dehnung noch weiter erhöht werden. Mikroaktuation durch einen MEMS-Aktuator kann den Durchhang der freihängenden CNT verringern und die mechanische Spannung erhöhen, wodurch ein breit einstellbarer Frequenzbereich von MHz bis GHz ermöglicht wird. In dieser Studie wurde eine skalierbare CNT-MEMS Integrationsplattform entwickelt und der erste einstellbare CNT-Resonator mit integriertem MEMS-Aktuationssystem demonstriert.

Ein Integrationsprozess wurde entwickelt, um eine frei hängende CNT niedriger Defektdichte in einen MEMS-Aktuator zu integrieren. Unter Verwendung von Top-down-Mikrofabrikation wird eine temporär stützende Struktur hergestellt, die ein Reissen der freihängenden Struktur während der Nassprozessierung verhindert. Zusätzlich wird eine Al2O3-Schicht durch Atomlagenabscheidung aufgebracht, um die gewachsenen CNTs während der Prozessierung nach dem Wachstum vor Kontamination mit Photolack zu schützen. Die Nassprozessierung nach dem Wachstum ermöglicht die Metallisierung auf CNTs durch ein Lift-off-Verfahren. Die oben aufgebrachte Metallisierung bietet verbesserte elektrische Kontakte und eine robuste, beidseitig geklemmte Konfiguration. Unter entwickelten Integrationsprozesses wurden Verwendung des der Einfluss von Prozessschritten auf die Betriebseigenschaften der CNTs und die Langzeitstabilität des Bauteilwiderstands untersucht.

Um die Dehnung der integrierten CNT einstzustellen, wurde ein Mikroaktuationssystem entworfen. Das System wird durch einen auf gebogenen Balken basierenden elektrothermischen Aktuator angetrieben. Um elektrische und thermische Störeinflüsse zwischen dem Akutator und dem CNT Bauteil zu vermeiden, wurde ein isolierender mechanischer Aufbau, im Folgenden "Adapter" genannt, entworfen. Dieser Adapter ist kompakt und besteht aus lediglich zwei separaten Siliziumstrukturen. Insbesondere kann er mit dem entwickelten Integrationsprozess hergestellt werden. Der Adapter kann die CNT elektrothermisch vom Aktuator isolieren, während die CNT durch den Aktuator gedehnt wird. Dies ermöglicht die Untersuchung der elektrischen Antwort der CNT auf Dehnung. Das gesamte integrierte CNT-MEMS-Bauteil, das eine freistehende CNT, einen Adapter und einen thermischen Aktuator beinhaltet, kann mit dem entwickelten Integrationsprozess hergestellt werden. Die Funktionalität des gesamten CNT-MEMS-Bauteils wurde zuerst durch quasistatische elektromechanische Zugtests überprüft. Die Änderungen des elektrischen Stroms in den gedehnten CNTs wurden während des Zugtests gemessen. Die reproduzierbare und reversible durch Dehnung verursachte Strommodulation der getesteten CNTs bestätigt die Funktionalität der Bauteile. Bei der abschliessenden dynamischen Charakterisierung wurde die Resonanzfrequenz der freihängenden CNT durch den Aktuator eingestellt. Der Frequenzmodulationsmechanismus wurde zurückgeführt auf die Reduktion des Durchhangs der CNT. Somit wurde ein einstellbarer CNT-Resonator demonstriert und die vollständige Entwicklung der Integrationsplattform nachgewiesen.

### Acknowledgement

I would like to thank Prof. Christofer Hierold for the great opportunity of working on this project. Under Prof. Hierold's supervision, I learned not only scientific knowledge but also serious research attitudes. I am grateful to Prof. Nico de Rooij for co-supervising my doctoral study. I am grateful for Prof. Wei-Leun Fang for his encouragement to study abroad. I would like to express my thanks to Eeva Köpilä for her great support in the administration and her great care for my life in Zurich from the beginning till now. My thanks go to Dr. Matthias Muoth and Dr. Cosmin Roman for their strong academic and mental supports. But for their support, I would not have accomplished this work. It has been a great time to discuss and work with them. Dr. Stuart Truax is acknowledged for making the dream of a tunable CNT resonator come true. I would like to thank Dr. Thomas Helbling and Dr. Lukas Durrer for guiding me to processing in the FIRST cleanroom. The nasty process problems would have not been resolved without the invaluable advises from Dr. Haifeng Sun, Dr. Yuping Zeng, Dr. Kaiyu Shou, Dr. Ronald Grundbacher, Dr. Stéphane Kühne, and Yunjia Li. I am grateful for Sandro Bellini and Donat Scheiwiller for their firstclass support in the FIRST and FIRST-CLA cleanrooms. I would like to acknowledge the assistance in processing as well as in experiments by Xiao Di, Maria Politou, Yu Liu, and Meijun Liu. The achievement of the project would not have been possible without the contributions of the project partners, Rokhaya Gueye, Christian Kauth, and Dr. Ji Cao. I am grateful for the helpful discussions and hints from the CNT group members, Valentin Döring, Kiran Chikkadi, Wei Liu, Tobias Süss, Dr. Miroslav Haluska, Dr. Emine Cagin, Dr. Olga Kurapova. The great working atmosphere in MNS group is something hardly found somewhere else. I did had a great time in working hours and leisure time with Dr. Marcel Suter, Dr. Moritz Mattmann, Dr. Silvan Schimid, Dr. Florian Umbrecht, Dr. Clementine Boutry, Dr. Etienne Schwyter, Nina Wojtas, and Christian Peters. I am appreciated for the great help to revise the dissertation by Prof. Christofer Hierold, Dr. Emine Cagin, Dr. Matthias Muoth, Dr. Cosmin Roman, Dr. Stuart Truax, and Valentin Döring. I would like to acknowledge Joanne Walker for proofreading the dissertation.

This work has been performed ten thousand kilometers away from home. I would like to thank my family, 李林阿花, 李金德, 曾粉妹, 李嘉蕙, 楊明勳, 楊謹謙, for being patient and enduring my absence in the past six year. Last but not the least; I want to say thank you

to my beloved wife, Hsi-Wen Tung (童璽文). She is always supporting me throughout the hard time of process development. She grants me the ability to fly freely in my life.

# List of symbols and SI units

| Symbol                 | SI unit            | Description                                                           |  |  |  |

|------------------------|--------------------|-----------------------------------------------------------------------|--|--|--|

| AF                     |                    | Amplification factor of a bent beam                                   |  |  |  |

| $A_{ib}$               | [m <sup>2</sup> ]  | Cross-section area of an inclined beam                                |  |  |  |

| A <sub>cnt</sub>       | [m <sup>2</sup> ]  | Cross-section area of a CNT                                           |  |  |  |

| E <sub>cnt</sub>       | [Pa]               | Young's modulus of CNT                                                |  |  |  |

| $E_{Si}$               | [Pa]               | Young's modulus of Si                                                 |  |  |  |

| $F_{Buckle,sb}$        | [N]                | Buckling force of a suspension beam                                   |  |  |  |

| F <sub>Buckle,ib</sub> | [N]                | Buckling force of an inclined beam                                    |  |  |  |

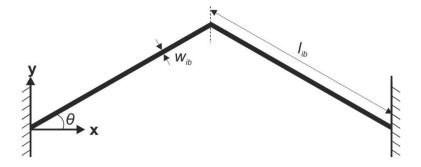

| F <sub>ext</sub>       | [N]                | External force loading on a bent-bent actuator                        |  |  |  |

| Faxial                 | [N]                | Axial force in a CNT                                                  |  |  |  |

| $f_{Faxial}$           | [Hz]               | Resonant frequency of a CNT strained by an axial force, $F_{axial}$   |  |  |  |

| $I_d$                  | [A]                | Drain current of a CNTFET                                             |  |  |  |

| Ia                     | [A]                | Electrical current passing through an actuator                        |  |  |  |

| Icnt                   | [A]                | Electrical current passing through a CNT                              |  |  |  |

| Isb                    | [m <sup>4</sup> ]  | Area moment of inertia of a suspension beam                           |  |  |  |

| k                      | $[m^2 \cdot kg/s]$ | Planck constant (= $6.626 \times 10^{-34}$ )                          |  |  |  |

| l <sub>sb</sub>        | [m]                | Length of a suspension beam                                           |  |  |  |

| $l_{ib}$               | [m]                | Length of an inclined beam                                            |  |  |  |

| L <sub>cnt</sub>       | [m]                | Length of a CNT                                                       |  |  |  |

| I <sub>m,cnt</sub>     | [m <sup>4</sup> ]  | Area moment of inertia of a cylindrical CNT                           |  |  |  |

| n                      |                    | Number of bent beam pairs in a thermal actuator                       |  |  |  |

| R <sub>m</sub>         | [Ω]                | Measured device resistance of a CNTFET                                |  |  |  |

| R <sub>c</sub>         | [Ω]                | Electrical contact resistance of a CNTFET                             |  |  |  |

| R <sub>cnt</sub>       | [Ω]                | CNTFET channel resistance                                             |  |  |  |

| R <sub>0</sub>         | [Ω]                | A curve fitting resistance of the maximum resistance versus strain    |  |  |  |

| <b>R</b> <sub>1</sub>  | [Ω]                | A curve fitting resistance of the maximum resistance versus strain    |  |  |  |

| $R_x^M$                | [N]                | Reaction force in x-direction at the end of an inclined beam          |  |  |  |

| $R_x^{M,\Delta T}$     | [N]                | Reaction force of an incline beam caused by thermal expansion         |  |  |  |

| $R_x^{M,\sigma_{res}}$ | [N]                | Reaction force of an incline beam caused by residual stress           |  |  |  |

| $R_x^{M,F_{ext}}$      | [N]                | Reaction force of an incline beam caused by an external force loading |  |  |  |

| S                      |                    | Slack of CNT                                                          |  |  |  |

| Symbol           | SI unit              | Description                                                   |  |

|------------------|----------------------|---------------------------------------------------------------|--|

| Т                | [K]                  | Temperature                                                   |  |

| t                | [m]                  | Thickness                                                     |  |

| $u_{y,f}$        | [m]                  | Free displacement (without force output) of a bent beam       |  |

| $u_y^M$          | [m]                  | Displacement at point M in y direction                        |  |

| $V_a$            | [V]                  | Actuation voltage                                             |  |

| $V_{gd}^{ac}$    | [V]                  | AC gate voltage                                               |  |

| $V_{gd}^{dc}$    | [V]                  | DC gate voltage                                               |  |

| $V_{sd}^{ac}$    | [V]                  | AC source-drain voltage                                       |  |

| $V_{gd}^{dc}$    | [V]                  | DC gate voltage                                               |  |

| α <sub>si</sub>  | [1/K]                | Thermal expansion coefficient of Si                           |  |

| β                |                      | A curve fitting value of the maximum resistance versus strain |  |

| 3                |                      | Strain                                                        |  |

| E <sub>cnt</sub> |                      | CNT strain                                                    |  |

| $\sigma_e$       | [Ω-cm]               | Electrical resistivity                                        |  |

| $\sigma_{res}$   | [Pa]                 | Residual stress                                               |  |

| θ                | [Degree]             | Inclined angle of an inclined beam                            |  |

| $\Delta T$       | [K]                  | Average temperature increase                                  |  |

| $\rho_{cnt}$     | [kg/m <sup>3</sup> ] | Mass density of CNT                                           |  |

# List of abbreviations

| Abbreviation | Full phrase                             |  |

|--------------|-----------------------------------------|--|

| AFM          | Atomic force microscopy                 |  |

| ALD          | Atomic layer deposition                 |  |

| BHF          | Buffered hydrofluoric acid              |  |

| CNT          | Carbon nanotube                         |  |

| CNTFET       | Carbon nanotube field effect transistor |  |

| cCVD         | Catalyzed chemical vapor deposition     |  |

| MEMS         | Micro electro-mechanical system         |  |

| NMP          | N-methylpyrrolidone (resist remover)    |  |

| Poly-Si      | Polycrystalline silicon                 |  |

| RIE          | Reactive ion etching                    |  |

| SWNT         | Single-walled carbon nanotube           |  |

| SiNW         | Silicon nanowire                        |  |

| sc-Si        | Single-crystalline silicon              |  |

| SOI          | Silicon on insulator                    |  |

| SEM          | Scanning electron microscopy            |  |

| TEM          | Transmission electron microcopy         |  |

| TSV          | Through silicon via                     |  |

| VHF          | Vapor hydrofluoric acid                 |  |

# Contents

| Abstract                                                                                                                                                                                                                                                                                                                                                                                              | 2                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Zusammenfassung                                                                                                                                                                                                                                                                                                                                                                                       | 4                                    |

| Acknowledgement                                                                                                                                                                                                                                                                                                                                                                                       | 6                                    |

| List of symbols and SI units                                                                                                                                                                                                                                                                                                                                                                          | 8                                    |

| List of abbreviations1                                                                                                                                                                                                                                                                                                                                                                                | 0                                    |

| Contents1                                                                                                                                                                                                                                                                                                                                                                                             | 1                                    |

| Chapter 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                | 1                                    |

| 1.1. Motivation                                                                                                                                                                                                                                                                                                                                                                                       | 1                                    |

| 1.2. Objectives                                                                                                                                                                                                                                                                                                                                                                                       | 3                                    |

| 1.3. Contents of chapters                                                                                                                                                                                                                                                                                                                                                                             | 4                                    |

| Chapter 2 Current developments                                                                                                                                                                                                                                                                                                                                                                        | 9                                    |

| 2.1. Material property investigation                                                                                                                                                                                                                                                                                                                                                                  | 9                                    |

| 2.2. On-chip actuation                                                                                                                                                                                                                                                                                                                                                                                | 0                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                       |                                      |

| 2.3. Integration of suspended CNTs on Si micro-structures                                                                                                                                                                                                                                                                                                                                             | 0                                    |

| 2.3. Integration of suspended CNTs on Si micro-structures                                                                                                                                                                                                                                                                                                                                             |                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                       | 2                                    |

| Chapter 3 Process development for integrating suspended CNTs into Si micro-structures.1                                                                                                                                                                                                                                                                                                               | 2<br>2                               |

| Chapter 3 Process development for integrating suspended CNTs into Si micro-structures.1<br>3.1. Approach                                                                                                                                                                                                                                                                                              | 2<br>2<br>4                          |

| Chapter 3 Process development for integrating suspended CNTs into Si micro-structures.1<br>3.1. Approach                                                                                                                                                                                                                                                                                              | 2<br>2<br>4<br>6                     |

| Chapter 3 Process development for integrating suspended CNTs into Si micro-structures. 1 3.1. Approach                                                                                                                                                                                                                                                                                                | 2<br>2<br>4<br>7                     |

| Chapter 3 Process development for integrating suspended CNTs into Si micro-structures. 1 3.1. Approach                                                                                                                                                                                                                                                                                                | 2<br>2<br>4<br>7<br>7                |

| Chapter 3 Process development for integrating suspended CNTs into Si micro-structures. 1 3.1. Approach                                                                                                                                                                                                                                                                                                | 2<br>4<br>6<br>7<br>8                |

| Chapter 3 Process development for integrating suspended CNTs into Si micro-structures.1         3.1. Approach                                                                                                                                                                                                                                                                                         | 2<br>4<br>6<br>7<br>8<br>9           |

| Chapter 3 Process development for integrating suspended CNTs into Si micro-structures.1         3.1. Approach                                                                                                                                                                                                                                                                                         | 2<br>2<br>4<br>6<br>7<br>8<br>9<br>9 |

| Chapter 3 Process development for integrating suspended CNTs into Si micro-structures. 1         3.1. Approach.       1         3.2. Integration process flow.       1         3.3. Design       1         3.4. Fabrication results       1         3.4.1. Polishing       1         3.4.2. Catalyst patterning       1         3.4.3. Metallization       1         3.4.4. Liquid HF release       1 | 2<br>4<br>6<br>7<br>8<br>9<br>1      |

| 3.6. Process development                                         | 23 |

|------------------------------------------------------------------|----|

| 3.6.1. Removing top oxide by mechanical polishing                | 23 |

| 3.6.2. Patterning catalysts                                      | 25 |

| 3.6.3. ALD Al <sub>2</sub> O <sub>3</sub> assisted lithography   | 28 |

| 3.6.4. CNT selection                                             | 33 |

| 3.6.5. Alignment of photomasks                                   | 35 |

| 3.7. Influence of liquid HF etching on metal contacts            | 37 |

| 3.8. Investigation of metal contact for long-term stability      |    |

| 3.8.1. 150 nm Au alone                                           |    |

| 3.8.2. 0.5 nm/ 1 nm/ 2 nm Cr and 150 nm Au                       | 41 |

| 3.9. Discussions                                                 | 44 |

| 3.9.1. Features of the integration process                       | 44 |

| 3.9.2. Gate modulation                                           | 45 |

| 3.9.3. Liquid HF influence on CNTs                               | 49 |

| 3.9.4. Adhesion of Au-Si                                         | 51 |

| 3.9.5. Long-term stability of CNTFETs in ambient air             | 51 |

| 3.10. Summary                                                    | 52 |

| Chapter 4 Embedded micro-actuation system                        | 54 |

| 4.1. Design of an embedded micro-actuation system                | 54 |

| 4.1.1. Characterization of the Si device layer                   | 54 |

| 4.1.2. Insulation between a suspended CNT and a thermal actuator | 56 |

| 4.1.3. Actuation system                                          | 59 |

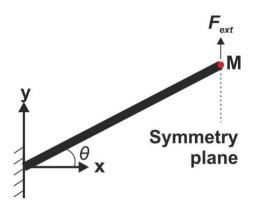

| 4.2. Fabrication results                                         | 64 |

| 4.3. Characterization of the fabricated actuation system         | 67 |

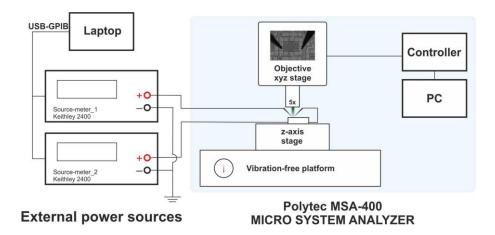

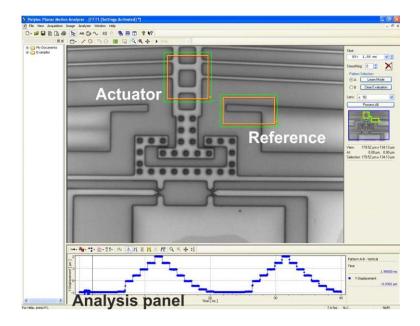

| 4.3.1. Displacement of the actuation system                      | 67 |

| 4.3.2. Monitoring the leakage current through the adapter        | 70 |

| 4.4. Discussion                                                  | 73 |

| 4.4.1. Electrical insulation of native oxides                             | 73      |

|---------------------------------------------------------------------------|---------|

| 4.4.2. Low thermal conductance of point contacts                          | 73      |

| 4.4.3. Operation in ambient conditions                                    | 75      |

| 4.5. Summary                                                              | 76      |

| Chapter 5 Demonstrations of CNT strain tuning by the embedded actuation s | ystem78 |

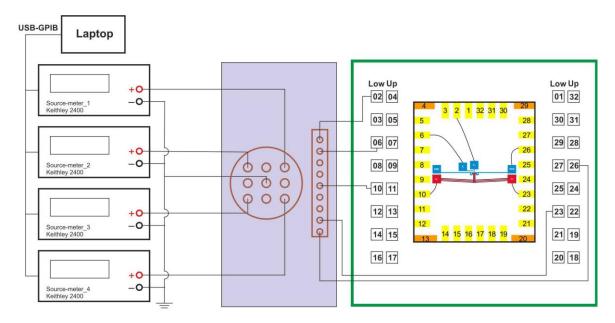

| 5.1. In situ electro-mechanical loading tests                             | 78      |

| 5.1.1. Sample preparation                                                 | 78      |

| 5.1.2. Experimental setup                                                 | 80      |

| 5.1.3. Tensile test                                                       | 80      |

| 5.1.4. Analysis                                                           | 85      |

| 5.2. Tunable CNT resonator                                                | 89      |

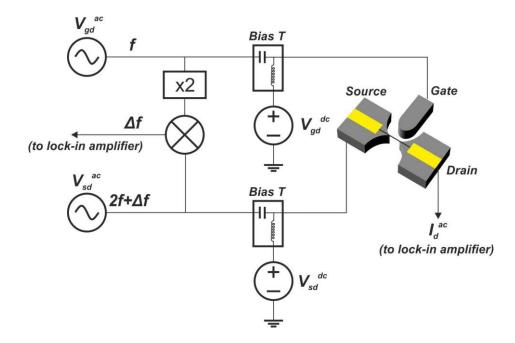

| 5.2.1. Measurement technique                                              | 89      |

| 5.2.2. Refined design for high frequency measurements                     | 90      |

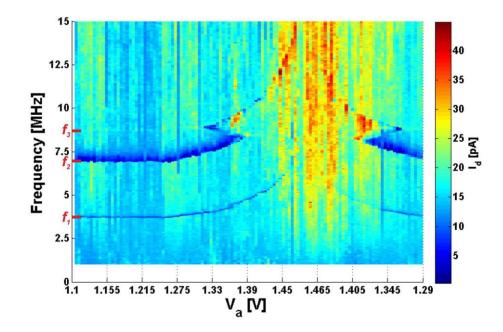

| 5.2.3. Measurement setup and measurement results                          | 92      |

| 5.2.4. Analysis                                                           | 94      |

| 5.3. Summary                                                              | 97      |

| Chapter 6 Conclusions and outlook                                         |         |

| 6.1. Conclusions                                                          | 98      |

| 6.2. Outlook                                                              | 99      |

| Appendix                                                                  | 101     |

| Appendix-I : Liquid HF and vapor HF                                       | 101     |

| Appendix-II : Device stability of non-suspended CNT devices               | 103     |

| Appendix-III : Index of CNTFETs                                           | 108     |

| Appendix-IV : Simulation of temperature distribution                      | 109     |

| Appendix-V : Propagation of uncertainties                                 | 112     |

| Bibliography                                                              | 114     |

| Publications                                                              | 122     |

| Curriculum vitae |

|------------------|

|------------------|

### **Chapter 1 Introduction**

The advantages of miniaturization of electronics and transducers are smaller dimensions and lower power consumption. Micro-electro-mechanical systems (MEMS) is an example of the miniaturization trend of transducers. Micro-scaled sensors and actuators can be fabricated by top-down surface and bulk micromachining. While the device dimensions are further shrunk down to nano-scale, new synthesis methods of nano-structures provide alternative techniques to fabricate miniaturized devices. Carbon nanotubes (CNTs), explored in 1991 by Ijima [1], is an example of a nano-structure that is integrated into a device via a bottom-up approach. Carbon nanotubes exhibit outstanding material properties, and have drawn tremendous research attention. For example, the high on/off current ratio of CNT field effect transistors (CNTFET) makes it a promising electronic component for logic applications [2]. Additionally, the use of CNTs has been demonstrated in different applications [3], such as transducers and gas sensors.

#### 1.1. Motivation

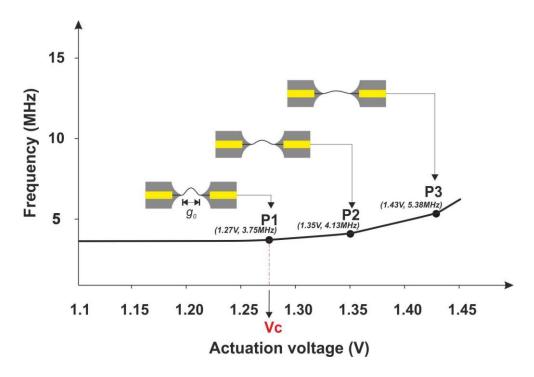

Among various types of applications, sensitive mass balance based on an electromechanical CNT resonator is of great interest [4]. As a vibrating structure, the high mechanical stiffness [5], light weight [6], and one-dimensional structure of a CNT raises the resonant frequency up to the GHz range [7]. In addition, the resonant frequency increases dramatically with a small axial force compared to the already high resonant frequency achieved by a non-strained CNT [8]. This is due to the transition from a beam vibration to a string vibration [9], and the extended elastic range of the CNTs. ( $<\sim$ 5%) [10]. For example, the resonance frequency of a non-strained 2 µm long CNT is 10 MHz, and it can reach 1 GHz if a strain of 1.74% is applied. Due to the high gauge factor, the resonance can be measured by monitoring the piezoresistive current, which leads to higher signal to noise ratio drain current peaks at resonance compared to sensing by capacitive current [11]. These material properties have made CNTs a promising candidate for high frequency tunable resonators.

#### Comparison of material properties

Another competitive nano-structure, silicon nano-wires (SiNW), also shows a great potential in high resonant frequency applications. A brief comparison of selected material

properties of CNT and SiNW is shown in Table 1-1. The Young's modulus of SiNW is size-dependent at nanometer scale. The gauge factor is dependent on the channel state. In the accumulation mode, the gauge factor is similar to that of bulk silicon; while in the depletion mode, the gauge factor is much higher by a factor of tens [12]. This increase in gauge factor is attributed to a strain-induced charge trapping change on the oxide-passivated surface, so-called giant piezoresistance effect [12, 13]. In addition to the material properties compared in Table 1-1, another advantage of CNT is the inert surface. The adsorption of oxygen can temporarily change the electronic properties of CNTs [14]. However, no additional oxide layer forms on the surfaces of CNTs. In the contrast, the surface of Si will acquire a thin native oxide layer ( $t_{ox}$ = 1~2 nm) in ambient air. This additional native oxide introduces tensile stress in SiNW [15] and subsequently influences the resonant frequency [16]. In summary, compared with SiNWs, CNTs have better properties for high frequency mechanical resonators.

|                 | CNT                        | SiNW                                           |

|-----------------|----------------------------|------------------------------------------------|

| Voung's modulus | 1 TPa [5, 17]              | 169 Gpa ( <i>t<sub>si</sub></i> = 300 nm) [18] |

| Young's modulus |                            | 53 GPa ( <i>t<sub>si</sub></i> = 12 nm) [18]   |

| Mass density    | 1340 Kg/m <sup>3</sup> [6] | 2300 Kg/m <sup>3</sup>                         |

| Fracture strain | 5.3% [10]                  | 6% ( <i>t<sub>si</sub></i> = 100~200 nm) [20]  |

| Fracture stram  | 13% [19]                   | 30% ( $t_{si}$ = 5~20 nm) [21]                 |

| Course factor   | 1000 [22]                  | 67 [12]                                        |

| Gauge factor    | 2900 [23]                  | 1806 [12]                                      |

Table 1-1 Comparison of the material properties of CNT and SiNW

#### • Integration of on-chip actuation

A common resonant frequency tuning method of a CNT resonator is to introduce an electrostatic force by a gate electrode [24]. The suspended CNT deforms laterally, resulting in resonant frequency modulation. In this configuration, there is no movable structure on the chip, except for the suspended CNT. Hence, slack is determined once the fabrication process is completed. Slack refers to the length of a CNT which is in excess of the straight line distance between its two clamping sites. If slack is involved in the vibration, it

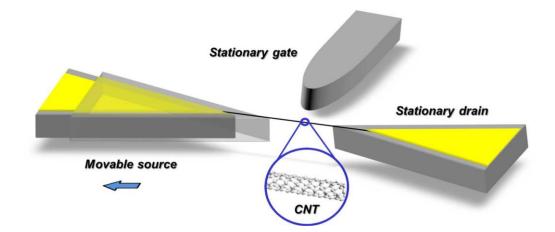

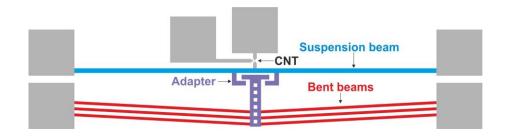

Figure 1-1 Schematic sketch of an integrated CNT-MEMS device.

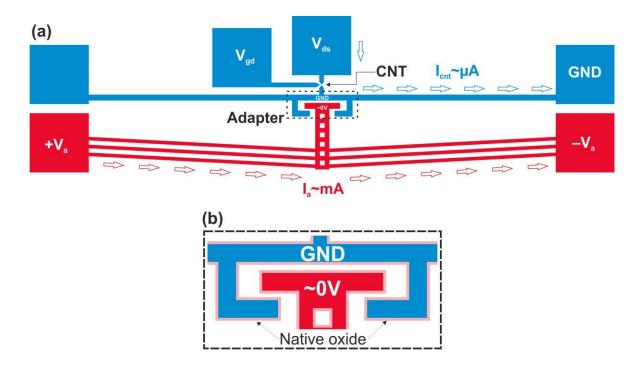

introduces additional out-of-excitation-plane modes [25], and the analysis becomes more complicated. This situation can be remedied by on-chip actuation. A precision MEMS actuator can reduce the slack of a suspended CNT, and a slack-free CNT resonator can be achieved. Moreover, the embedded actuator can adjust the axial strain of the suspended CNT. The actuation force of a MEMS actuator ( $\sim\mu$ N) is much larger than the axial strain induced by the electrostatic force ( $\sim$ 40 pN if gate distance= 1 µm and gate voltage= 1 V). This can achieve a larger tunable range of the CNT resonant frequency.

#### 1.2. Objectives

The research goal of this thesis was the development of a process flow for the integration of suspended CNTs and MEMS actuators. The final process is expected to fabricate high quality integrated CNT-MEMS devices, which can fulfill the following requirements:

- low-defect, clean suspended CNTs

- reliable electrical contacts of the integrated CNTs

- robust mechanical clamping of the suspended CNTs

- simultaneous and independent operation of the CNT and MEMS components

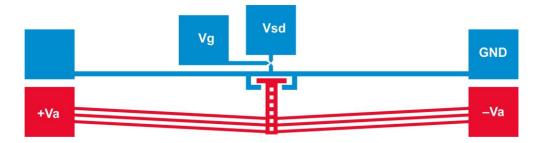

A conceptual device is shown in Figure 1-1. A CNT is suspended between a stationary drain electrode and a movable source electrode (driven by an actuator). The suspended CNT is clamped by a top metal layer. This metal layer provides improved electrical contacts and mechanical clamping. A side-gate electrode is employed to bias the CNTFET and excite the suspended CNT into vibration at the same time.

#### **1.3.** Contents of chapters

The major part of this thesis is the development of the integration process. The contents of each chapter are listed below:

Chapter 2: The state-of-the-art fabrication processes for suspended CNTs are briefly reviewed.

Chapter 3: The development of the CNT-MEMS integration process flow is described in detail. The process flow was developed on silicon-on-insulator (SOI) chips. The integration process of SOI and CNTs is abbreviated to SOIC. The development began with the integration of suspended CNTFETs into predefined stationary Si micro-structures (SOIC2 and SOIC3 shown in Table 1-2). The two key features of SOIC, a supporting oxide bridge and a protective Al<sub>2</sub>O<sub>3</sub> layer, were developed to enable post-growth wet processing and to eliminate contamination of resist during lithography. A CNT selection method was explored to improve orientation control of integrated CNTs. It can improve the device yield by 6 times. In this chapter, the development of the selected process steps is discussed. Using the fabricated devices, the influence of liquid HF etching on the metal contacts and the long-term device stability were investigated.

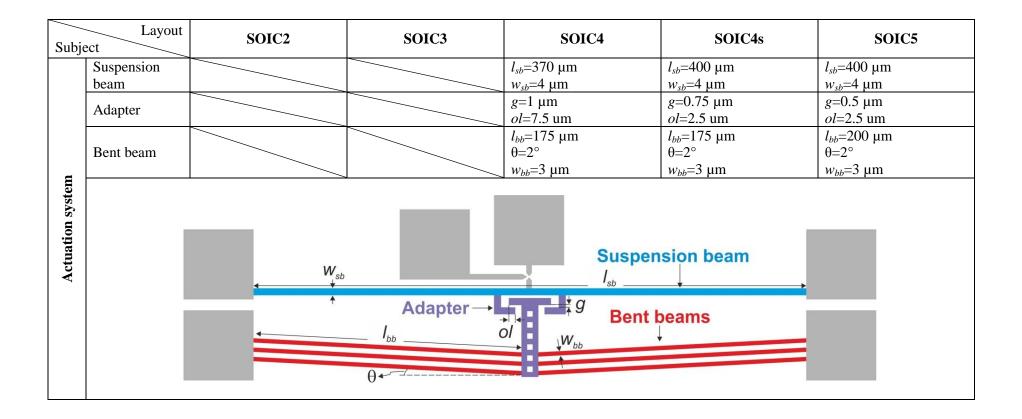

Chapter 4: The design parameters of MEMS electro-thermal actuators are discussed. In addition, a compact and versatile mechanical structure was introduced to make the integrated CNT and MEMS actuator to be simultaneously and independently operational.

Chapter 5: Using the integrated CNT-MEMS devices, electro-mechanical loading tests were performed. The preliminary results verified the functionality of the CNT-MEMS device. Moreover, a tunable CNT resonator was demonstrated with the embedded MEMS actuation system.

Chapter 6: The achievements of this thesis are summarized. The developed integration process is compared with state-of-the-art integration processes.

An overview of the development of the integration process and the structure designs is listed in Table 1-2. Note that the first design layout, SOIC1, was used to evaluate different potential integration approaches, and no working CNT devices were fabricated. Hence, SOIC1 is not included in this table.

| Subj      | Layout                                    | SOIC2                                                                            | SOIC3                                                                      | SOIC4                                                  | SOIC4s                                                                                     | SOIC5                                                  |  |

|-----------|-------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------|--|

| SOI wafer | Device layer                              | $t_{device} = 5 \ \mu m$<br>ρ=0.005-0.05 Ω-cm                                    | $t_{device} = 5 \ \mu m$<br>$\rho = 0.005 - 0.05 \ \Omega - cm$            | $t_{device} = 5 \ \mu m$<br>$\rho < 0.01 \ \Omega$ -cm | $t_{device} = 5 \ \mu m$<br>$\rho < 0.01 \ \Omega$ -cm                                     | $t_{device} = 5 \ \mu m$<br>$\rho < 0.01 \ \Omega$ -cm |  |

| 3M        | BOX layer                                 | t <sub>BOX</sub> =2 μm                                                           | t <sub>BOX</sub> =2 μm                                                     | t <sub>BOX</sub> =1 µm                                 | t <sub>BOX</sub> =1 μm                                                                     | t <sub>BOX</sub> =1 μm                                 |  |

| SOI       | Handle layer                              | $T_{handle}$ =400 μm<br>ρ=0.005-0.05 Ω-cm                                        | T <sub>handle</sub> =400 μm<br>ρ=0.005-0.05 Ω-cm                           | T <sub>handle</sub> =300 μm<br>ρ>2500 Ω-cm             | $\begin{array}{l} T_{handle} = 300 \ \mu m \\ \rho > 2500 \ \Omega \text{-cm} \end{array}$ | $T_{handle}=300 \ \mu m$ $\rho>2500 \ \Omega-cm$       |  |

|           | Lithography-1<br>Si structures            | UV                                                                               | DUV                                                                        | DUV                                                    | DUV                                                                                        | DUV                                                    |  |

|           | DRIE                                      | The Bosch process                                                                | The Bosch process                                                          | The Bosch process                                      | The Bosch process                                                                          | s The Bosch process                                    |  |

|           | Oxide by wet<br>thermal<br>oxidation      | $t_{SiO2}$ =1.7 µm                                                               | t <sub>SiO2</sub> =645 nm                                                  | t <sub>sio2</sub> =500 nm                              | t <sub>SiO2</sub> =500 nm                                                                  | t <sub>SiO2</sub> =500 nm                              |  |

|           |                                           | Diamond particles                                                                | Silica particles                                                           | Silica particles                                       | Silica particles                                                                           | Silica particles                                       |  |

|           | Polishing particles                       | [Investigation] Polishing<br>particles in Sec. 3.6.1with<br>C#SOIC2-RTC1 / C#SOI | n samples                                                                  |                                                        |                                                                                            |                                                        |  |

| S         | Lithography-2<br>catalysts                | UV                                                                               | UV                                                                         | UV                                                     | UV                                                                                         | UV                                                     |  |

| ces       | i .                                       | Acetone                                                                          | Acetone                                                                    | Acetone & NMP                                          | Acetone & NMP                                                                              | Acetone & NMP                                          |  |

| Process   | Catalyst lift-off                         |                                                                                  | [Investigation] Catalyst<br>NMP cleaning in Sec 3.6<br>C#Ox1-C1 / C#Ox1-C2 |                                                        |                                                                                            |                                                        |  |

|           | CNT mounth                                | Heat up in air                                                                   | Heat up in air                                                             | Heat up in air                                         | Heat up in air                                                                             | Heat up in air                                         |  |

|           | CNT growth                                | 15 min growth                                                                    | 15 min growth                                                              | 15 min growth                                          | 30 min growth                                                                              | 30 min growth                                          |  |

|           |                                           |                                                                                  |                                                                            | ALD Al <sub>2</sub> O <sub>3</sub>                     | ALD Al <sub>2</sub> O <sub>3</sub>                                                         | ALD Al <sub>2</sub> O <sub>3</sub>                     |  |

|           | Protective layer<br>during<br>lithography | C#SiN-C1                                                                         |                                                                            |                                                        |                                                                                            |                                                        |  |

Table 1-2 Development of the integration process and design layout

| Sub     | Layout                                    | SOIC2                                                                                                | SOIC3                 | SOIC4                            | SOIC4s                                                                                                                                                                   | SOIC5       |

|---------|-------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|         | Protective layer<br>during<br>lithography | [Investigation] The thick<br>protection during oxygen<br>3.6.4 with samples<br>C#Ox2-C1 / C#Ox2-C2 / | plasma ashing in Sec. |                                  |                                                                                                                                                                          |             |

|         | CNT selection                             |                                                                                                      |                       |                                  | [Investigation] Selective<br>oxygen plasma ashing. In<br>C#SOIC5-O2-C1                                                                                                   |             |

|         | Lithography-3 metal                       | UV                                                                                                   | DUV                   | DUV                              | DUV                                                                                                                                                                      | DUV         |

| ess     |                                           | 5 nm/200 nm                                                                                          | 2 nm/200 nm           | 2 nm/150 nm                      | 2 nm/150 nm                                                                                                                                                              | 1 nm/150 nm |

| Process | Cr/Au thickness                           |                                                                                                      |                       |                                  | [Investigation] Device re-<br>the thickness of adhesion<br>samples<br>C#SOIC4s-150Au-1<br>C#SOIC4s-150Au-2<br>C#SOIC5-0.5Cr150Au<br>C#SOIC5-1Cr150Au<br>C#SOIC5-2Cr150Au |             |

|         |                                           | Liquid HF                                                                                            | Liquid HF             | Liquid HF/Vapor HF <sup>*1</sup> | Liquid HF/Vapor HF <sup>*2</sup>                                                                                                                                         | Liquid HF   |

|         | Release                                   | [Investigation] The influ<br>CNT device resistances S<br>C#SOIC3-R3C2 / C#SOI                        | ec. 3.7 with samples  |                                  |                                                                                                                                                                          |             |

\*1 C#SOIC4-R5C1 was released by vapor HF.

\*2 C#SOIC4s-RVHFC1 was released by vapor HF.

| Subje  | Layout                                                                                                 | SOIC2                 | SOIC3                                                                                | SOIC4                                                             | SOIC4s                                                                                 | SOIC5                                                                                                         |

|--------|--------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

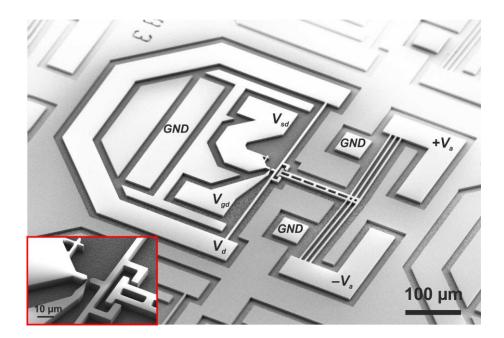

|        | Device<br>components                                                                                   | • Source, drain, gate | • Source, drain (, gate)                                                             | <ul> <li>Source, drain, gate</li> <li>Actuation system</li> </ul> | <ul> <li>Source, drain, gate</li> <li>Actuation system</li> <li>RF GSG pads</li> </ul> | <ul> <li>Modified shapes of<br/>source, drain, gate</li> <li>Actuation system</li> <li>RF GSG pads</li> </ul> |

| Design | Device<br>overview<br>(scale bar<br>100 µm)<br>Si<br>Catalyst<br>Metal                                 |                       | 2T type<br>4T type                                                                   |                                                                   |                                                                                        |                                                                                                               |

| Dec    | Close-up of<br>the electrode<br>layout for<br>CNTFET<br>(scale bar<br>3 µm)<br>Si<br>Catalyst<br>Metal | Side gate             | 2T type<br>4T type<br>Bridge width=<br>0.5/ 0.75 μm<br>Gate distance=<br>0.5/0.75 μm | Bridge width=0.5 μm<br>Gate distance=0.5 μm                       | Bridge width=0.5 μm<br>Gate distance=0.5 μm                                            | Bridge width=0.5 μm<br>Gate distance=0.5 μm                                                                   |

### **Chapter 2 Current developments**

The fabrication techniques of suspended CNTs are reviewed in this chapter and mirror the historical developments in this field. The initial research focus was the investigation of fundamental CNT material properties, such as Young's modulus and mechanical strength. With sufficient understanding of the CNT properties, the research focus gradually moved to applications, for example high frequency resonators and strain gauges. The following literature review of fabrication techniques will focus on the evolution of fabrication processes for suspended CNTs only.

#### **2.1.** Material property investigation

In the beginning of the research on suspended CNTs, the main focus was the extraction of Young's modulus and tensile strength. With the assistance of high resolution transmission electron microscopy (TEM), the diameters of CNTs were measured. Thermal vibration and forced vibration of freestanding CNTs were recorded during in-situ measurements. Treating a CNT as a rod or a cantilever, the Young's modulus of the CNT could be derived [5, 26] from its vibration frequency under classical continuum elasticity assumptions. Additionally, the static deformation of a CNT resulting from an external electrostatic force was measured in TEM, and the Young's modulus of the CNT was extracted [26]. In addition to in-situ measurements with TEM, atomic force microscopy (AFM) was commonly employed in measuring the bending and stretching stiffness of suspended CNTs [10, 17]. The Young's modulus derived from the experiments mentioned above is typically around  $E_{cnt}$ = 1 TPa. In the measurements, suspended or freestanding CNTs were prepared globally on chips, rather than in specific locations. The subsequent experiments were performed on selected well-suspended CNTs.

In order to measure the piezoresistive response of CNTs, electrical contacts to the CNTs are required. In [27], CNTs were grown by catalyzed chemical deposition (cCVD) from patterned catalyst islands on a SiO<sub>2</sub>/Si substrate. Metal leads were patterned by electron beam lithography to contact these as-grown CNTs [28]. A trench was etched in the SiO<sub>2</sub> layer to make a partially suspended CNT [29]. Using an AFM to bend the suspended segment of a CNT, the electromechanical characteristics of the CNT were revealed. However, AFM indentation is limited to laterally bending a suspended CNT. Polycrystalline silicon (poly-Si) cantilevers were fabricated to apply axial strain on suspended CNTs [30].

With the suspended poly-Si cantilever, the out-of-plane AFM indentation was converted into in-plane axial strain [22, 31]. Suspended CNTs were integrated into suspended Si cantilevers for the first time by Franklin [30].

#### 2.2. On-chip actuation

In addition to AFM indentation, on-chip actuation was also employed in straining CNTs. With the implement of on-chip actuation, applications related to straining CNTs can be achieved on a single chip. One type of the on-chip actuation is attained by the electrostatic force between a suspended CNT and a back-gate electrode. This type of device typically consists of one suspended CNT and three stationary electrodes. The fabrication is similar to the previous fabrication process of a suspended CNT with metal contacts for AFM indentation [29]. This approach is commonly utilized in CNT resonators [24, 32-34].

Another type of on-chip actuation is accomplished by movement of a MEMS actuator, such as an electrostatic comb-drive actuator and an electro-thermal bent-beam actuator [35-39]. Due to the difficulties of fabricating a suspended CNT on a MEMS actuator, assembly of a suspended CNT onto a pre-fabricated MEMS actuator is still the main approach for integration.

#### 2.3. Integration of suspended CNTs on Si micro-structures

An integration process involving a suspended CNT and a MEMS actuator is more challenging compared to the fabrication of suspended CNTs on flat SiO<sub>2</sub>/Si substrates. The difficulties mainly result from the fragility of the suspended CNTs, process-induced contaminations, and the ineffective orientation control of as-grown CNTs. Micron-long suspended CNTs can be damaged by viscous forces and capillary forces during wet processing. Additionally, the surfaces of CNTs tend to be contaminated by process chemicals, especially photographic resists. These two issues both occur in post-growth process steps. To avoid rupture and contamination, CNT growth is typically performed at the end of the entire process. However, only refractory metals, such as molybdenum (Mo) [30] and titanium nitride (TiN) [40], can endure the elevated growth temperature (~850 °C) in the cCVD growth process [41]. Additionally, the as-grown suspended CNTs are held in position by the van der Waal's force between CNTs and metals. If a CNT is small in diameter and the clamped length is short, the clamping force might not be sufficient to

clamp the ends of the CNT firmly while it is subjected to a strain, and sliding will occur [42].

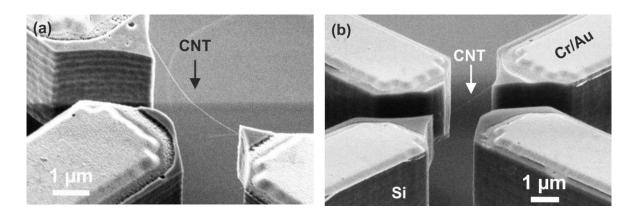

All the structures, including micro-electrodes, trenches and metal leads, need to be fabricated prior to CNT growth to avoid the risky rupture and processing contamination in the post-growth processing. To properly integrate as-grown CNTs into these predefined structures, it is important to control the location and orientation of as-grown CNTs. However, the cCVD growth method only allows for location control but not direction control. To actively align growth direction, a controlled gas flow [43, 44] and an electrical field [45, 46] were introduced during the cCVD procedure. Different from these active control methods, another approach, called directed growth, is commonly used in aligning suspended CNTs to predefined structures. It was initially demonstrated on a substrate with a predefined array of Si pillars [47, 48]. Catalysts were patterned on top of the Si pillars, and CNT growth would initiate from these pillars. The as-grown CNTs were likely to bridge to the neighboring Si pillars, and hence, the directions of suspended CNTs could be defined by the patterns of the Si pillar array. This method was later applied on a suspended Si cantilever [30]. Based on this approach, a sharp Si tip was introduced to improve the direction control of suspended CNTs on micro-structures [49]. Taking advantage of this approach, suspended CNTs can be aligned to the pre-fabricated micro-structures or actuators [40, 50]. However, the area on the side wall of the neighboring structure is relatively larger than the top surface, so as-grown CNTs are more likely to bridge to the side wall, rather than the top surface. This makes it difficult to electrically contact CNTs with the metal leads on top of the micro-structures. Tilted metal evaporation together with an onchip shadow mask is helpful to establish the electrical contact, even if a suspended CNT is attached to the side wall of a micro-structure [50].

In conclusion, it is still challenging to efficiently integrate clean suspended CNTs into predefined micro-structures with reliable electrical contacts and mechanical clamping. In the next chapter, an improved process for integrating suspended CNTs into MEMS structures is revealed.

# Chapter 3 Process development for integrating suspended CNTs into Si micro-structures

Silicon-on-insulator (SOI) chips are chosen as substrates for the integration process. The melting temperature of single crystal Si is as high as 1415 °C [51]. Hence, Si can endure the CNT growth temperature (~850 °C). Moreover, the reliable mechanical property of Si [52] as well as the advantageous in-plane actuation of SOI chips is beneficial for straining suspended CNTs. Two types of SOI chips were employed in the integration process. The process development began with the SOI chips, consisting of a 5 µm thick device layer, a 2 µm thick buried oxide layer, and a 400 µm thick handle layer. Considering further integration with backside through-silicon-vias (TSVs) and high operational frequency of CNT resonators, the process development was continued with the second type of SOI chips with a reduced buried oxide layer (1 µm) and a thinner handle layer (300 µm). The second type of SOI chips have a heavily-doped Si device layer ( $\rho_{device} < 0.01 \Omega$ -cm) to lower the driving voltage of an electro-thermal actuator and a resistive handle layer ( $\rho_{handle} > 2500 \Omega$ -cm) to reduce the high frequency signal coupling through the substrate.

#### 3.1. Approach

The integration process aimed to fabricate high quality suspended CNTs on MEMS actuators. Additionally, the process needed to be compatible with the backside TSV processing. The requirements of the integration process included:

- Clean, low-defect suspended CNTs

- Low electrical contact resistances of CNTs

- Robust mechanical clamping of the suspended CNTs

- Photomask-based lithographic process

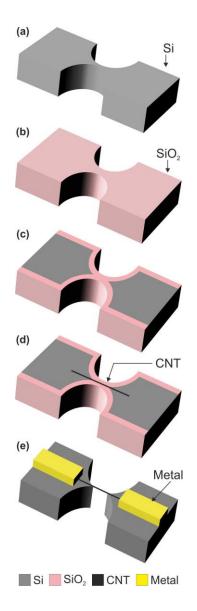

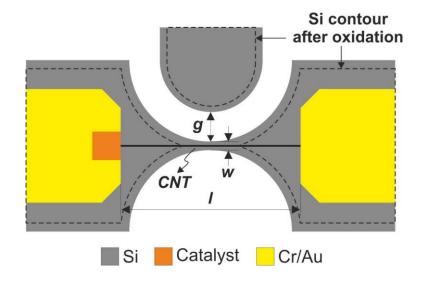

Figure 3-1 Sketch of the conceptual process flow for CNT integration into MEMS with a temporary support. A Si bridge was fabricated (a) and following oxidation converted the narrowest segment of the bridge into  $SiO_2$  (b). After removing the top oxide (c), CNTs were grown on the bridge (d), and metallization was subsequently performed. Finally, the oxide bridge was etched by liquid HF, and the CNT became suspended (e).

The combination of direct CNT growth and top metallization by lift-off can fulfill all the requirements listed above. However, it is nearly impossible to perform wet processing on long and suspended CNTs without damaging them. A temporary supporting structure can resolve this problem by providing a CNT with physical support during post-growth wet processing. The concept of this approach is shown in Figure 3-1. A Si bridge was patterned (Figure 3-1a). The narrowest part of the bridge was fully converted into SiO<sub>2</sub> by thermal oxidation (Figure 3-1b). In order to avoid the successively built-up structures, like CNTs

and metals, being detached in the final release step, the top oxide layer needed to be removed (Figure 3-1c). The plane surface of the oxide bridge was able to provide physical support for the as-grown CNT (Figure 3-1d). Hence, post-growth wet processing was enabled, and metal leads were patterned by resist-based wet lift-off process. After metallization, the oxide bridge was etched by liquid hydrofluoric acid (HF) in the final release step (Figure 3-1e), and the CNT and MEMS structures became suspended.

#### **3.2. Integration process flow**

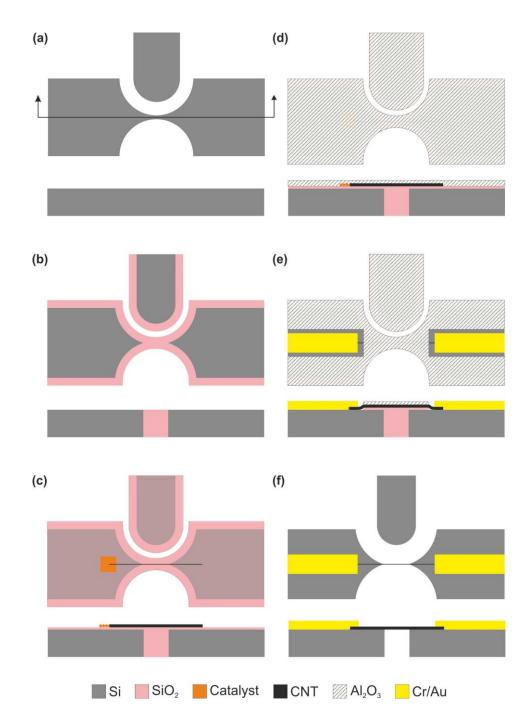

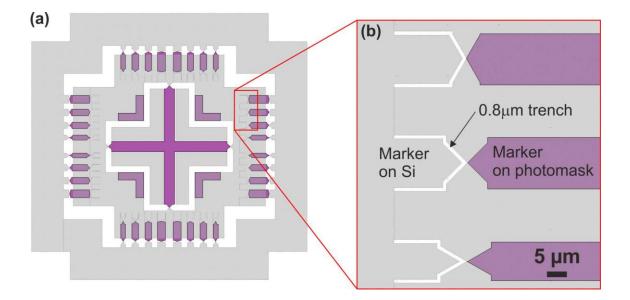

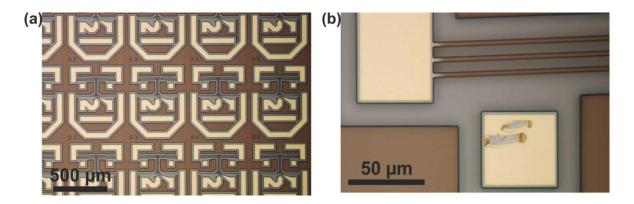

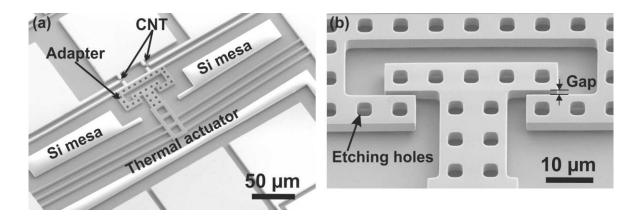

The patterns of all the Si structures were defined onto a 0.5-µm thick PMMA/MMA resist layer by deep UV lithography (DUV, ABM DUV mask aligner with a 220 nm filter). The minimum feature size of the design patterns on the photomask was 0.5 µm. Using the resist layer as an etching mask, the Si device layer was etched using the Bosch process (STS ICP) (Figure 3-2a). After stripping the resist, the chip was globally oxidized by wet thermal oxidation. A 500 nm thick SiO<sub>2</sub> layer was produced on Si surfaces, and therefore, the narrower part of the Si bridge was fully converted into SiO<sub>2</sub>. To prevent the successively built-up structures, such as CNTs and metals, from detaching in the last release step, the oxide layer on top of the Si device layer needed to be removed. Mechanical polishing (Logitech PM5 autolap) removed the top oxide and achieved a plane surface on the oxide bridge. The suspension used for polishing was Logitech SF1, which contained silica particles (~65 nm in diameter) (Figure 3-2b).

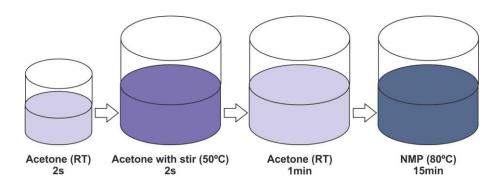

A barrier layer was required to prevent the formation of silicide from the iron catalysts at the elevated CNT growth temperature [53]. A short wet thermal oxidation step was performed to produce a thin SiO<sub>2</sub> layer ( $t_{SiO2}=25$  nm) as the required barrier layer. To define a CNT growth site, a catalyst window (3 µm by 3 µm) was patterned onto a photoresist layer (Shipley S1818,  $t_{S1818}=1.5$  µm) at one end of these two Si electrodes by UV lithography (Karl Süss MA6 mask aligner). The catalysts used in this process were ferritin-wrapped iron particles. These iron particles were adsorbed on the chip surface from an aqueous catalyst solution [41]. After the adsorption, the chip was rinsed by de-ionized water to remove the residual catalyst solution. Following this a lift-off was performed briefly in three consecutive acetone baths. The chip was further cleaned by a resist remover, N-methylpyrrolidone (NMP). Catalysts only remained within the growth site. CNTs were grown from these catalysts by catalyzed chemical vapor deposition at 850 °C [41]. Statistically, some of the CNTs reach the other side of the bridge (Figure 3-2c). To protect

Figure 3-2 Integration process flow (top view and cross section of the device layer on an SOI chip). (a) DUV lithography & silicon etching by the Bosch process; (b) thermal oxidation & removal of top oxide by polishing for the temporary supporting bridge; (c) thermal oxidation, catalyst patterning & CNT growth; (d) global deposition of a thin protective  $Al_2O_3$  layer by ALD; (e) etching of the  $Al_2O_3$  at contact windows by BHF & metallization; (f) removal of SiO<sub>2</sub> and  $Al_2O_3$  by concentrated liquid HF & drying in a critical point dryer.

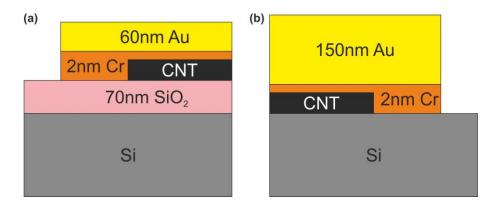

the as-grown CNTs from being contaminated by the sticky resist in the following lithography for metal patterning, an Al<sub>2</sub>O<sub>3</sub> layer (~40 nm) was deposited on the entire chip by low temperature atomic layer deposition (ALD) at 150 °C (Figure 3-2d). To define electrical contact on the aligned CNT, two lithography options were demonstrated. One was DUV lithography with three positive-tone resist layers on top of each other, i.e. two layers of PMMA/MMA and one layer of PMMA (t<sub>total</sub>~1.8 µm). The other was UV lithography with negative-tone photoresist (~4 µm), AZ nLOF 2070. Since the CNT was still fully covered by the protective Al<sub>2</sub>O<sub>3</sub> layer, it was possible to perform an optional cleaning step by oxygen plasma ashing to remove the resist residues on the contact areas. To make the Al<sub>2</sub>O<sub>3</sub>-covered CNTs accessible to the subsequently-deposited metals, the chip was dipped in a 6% buffered hydrofluoric acid (BHF) for 1.5 min, while the patterned resist layer served as an etching mask. After the BHF etching, the chip was baked on a hot plate at 100 °C for 90 s. A stack of metals, 2 nm chromium (Cr) and 200 nm gold (Au) or 1 nm Cr and 150 nm, was deposited by an electron-beam evaporator (Plassys II MEB550SL) at a deposition rate of 0.1 nm/s. The metal lift-off was carried out in NMP at 80 °C for three hours (Figure 3-2e). The sacrificial SiO<sub>2</sub> layer and the protective  $Al_2O_3$  layer were etched by 48% liquid HF for 3 min to leave the CNT suspended. The SOI chip was dried in a super critical point dryer (CPD, Tousimis Automegasamdri 915B) (Figure 3-2f).

#### 3.3. Design

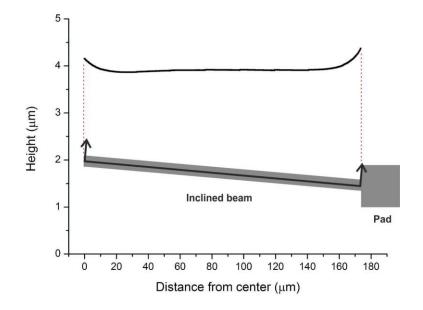

There are three key design parameters of the device layout. These parameters are the side gate distance (g), Si bridge width (w), and metal pitch (l), as indicated in Figure 3-3. In

Figure 3-3 Three key parameters of the layout design.

order to improve gate modulation of the integrated CNTFET, the side gate distance should be as small as possible. Here, the gap was designed as  $g=0.5 \ \mu\text{m}$ . Since the Si bridge needed to be fully oxidized, increasing the bridge width prolongs the oxidation duration. Moreover, a wider bridge tends to support more CNTs, and hence, there would be more CNTs in one device. Consequently, the bridge width of  $w=0.5 \ \mu\text{m}$  was chosen. The pitch between two metal leads sets the requirement of the minimum CNT length. CNTs which are longer than the pitch can be contacted by metals. Considering the Si structure and process tolerance, the minimum pitch was set as  $l = 4.5 \ \mu\text{m}$ .

#### **3.4.** Fabrication results

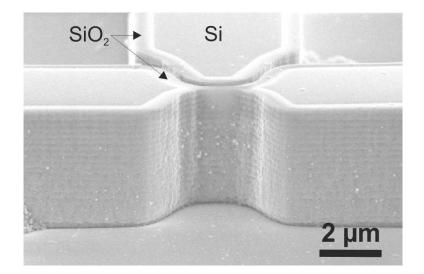

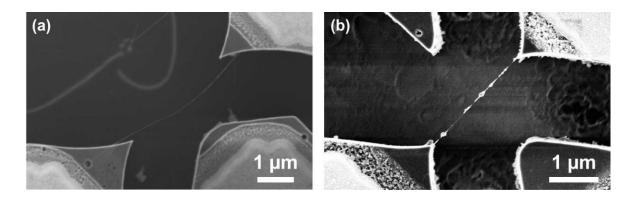

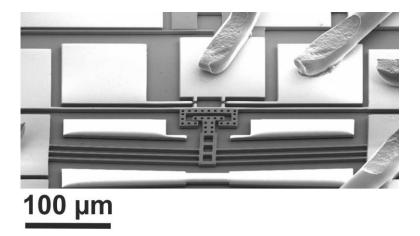

#### 3.4.1. Polishing

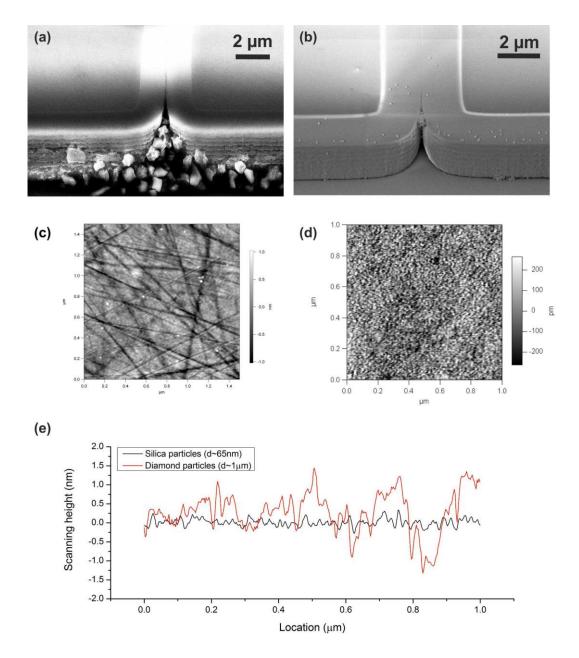

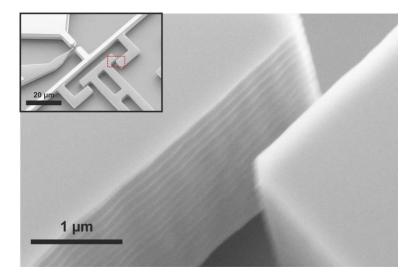

Figure 3-4 shows a scanning electron microscopy (SEM) image of a tilt view of three Si electrodes and the supporting oxide bridge after removing the top oxide by polishing (corresponding to the process step in Figure 3-2b). The mid-segment of the bridge was fully oxidized, and two opposite Si electrodes became visible after the 500 nm thick top oxide was removed. No abrupt step is seen in the topography of the polished bridge. This is important in avoiding kinks in the as-grown CNTs supported by the bridge. The topography of the polished oxide bridge was measured by a white light interferometer to be a shallow concave, where the center was 0.1  $\mu$ m lower than the two ends. The small particles seen on the side walls of the Si electrodes in Figure 3-4 are likely residual silica particles. They are

Figure 3-4 SEM image of a tilt view of three polished Si electrodes and an oxide bridge. The middle of the oxide bridge was measured to be slightly lower than the two opposite Si electrodes by  $0.1 \mu m$ . (C#SOIC4)

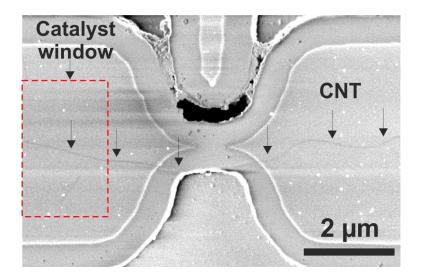

Figure 3-5 SEM image of a CNT grown from the defined catalyst window (dashed line enclosed area) to the opposite Si electrode. (C#SOIC4s)

etched by liquid HF in the final release. The mechanical polishing can produce smooth surface in addition to the topography. The root mean square roughness of the polished Si surface was as smooth as 0.1 nm, measured by atomic force microscopy (AFM).

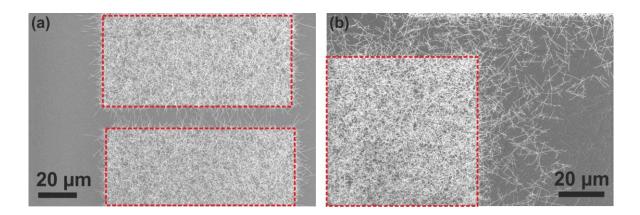

#### 3.4.2. Catalyst patterning

To define the CNT growth site, typically one growth window is patterned at the front end of one Si electrode for each device, as shown in Figure 3-2c. The synthesis of CNTs is initialized from the catalysts within the growth site. Without any external electrical field or gas flow during growth, CNTs are growing freely in all directions. In an ideal situation, one CNT bridges to the opposite Si electrode, as shown in Figure 3-5. Adsorption in a catalyst solution of higher concentration allows more CNTs to be grown along the oxide bridge to the opposite Si electrode. However, the possibility of gate leakage currents caused by CNTs of undesired orientations is also increased and CNT bundles form more often. As a result, defining the best concentration is challenging. During the process development, a target was set as the concentration which could result in 12 as-grown CNTs within one growth site (3 µm by 3 µm). If the CNT growth is random in all directions, one of these 12 as-grown CNTs could be within the tolerable direction  $(\pm 15^{\circ})$  per device. The tolerance angle was calculated based on the layout of the catalyst site and the metal leads. This is a useful guideline to tune the catalyst concentration. However, the best yield achieved was 1% and thus an efficient method of cutting incorrectly-orientated CNTs was explored to improve the situation, which is discussed in section 3.6.4.

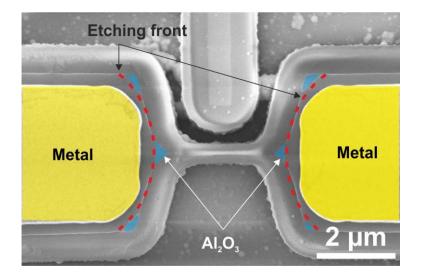

Figure 3-6 Top view of a device after metallization. The dashed line indicates the etch front on the  $Al_2O_3$  layer. The etched  $Al_2O_3$  areas were larger than the metal leads because of the inclined profile of the resist and the over-etching by BHF. Note that no CNT is seen in this figure. Yellow color of metals and blue color of  $Al_2O_3$  are added to enhance the visibility. (C#SOIC5)

#### 3.4.3. Metallization

Before metal evaporation, the protective  $Al_2O_3$  layer on the metal contact areas needed to be removed. No additional lithography was required for this step. The resist layer patterned for metallization served as an etching mask, the contact windows on the  $Al_2O_3$  layer were opened by BHF etching. In this BHF etching step, the  $Al_2O_3$  layer must be completely removed so that the CNTs can be electrically contacted by metals. To ensure the  $Al_2O_3$ layer was completely removed on the contact windows of hundreds of devices on a 1.8 cm by 1.8 cm chip, improved wetting by 20% isopropanol (IPA) [54] and over-etching were performed. Figure 3-6 shows an SEM image after metallization. As indicated by the dashed line, the etched  $Al_2O_3$  layer was broader than the metal leads due to the inclined profile of the resists (for lift-off process) and the over-etching during opening contact windows on the  $Al_2O_3$  layer by BHF.

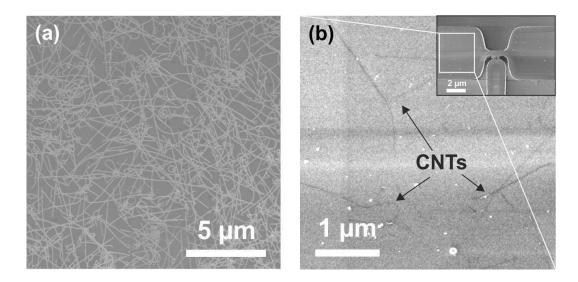

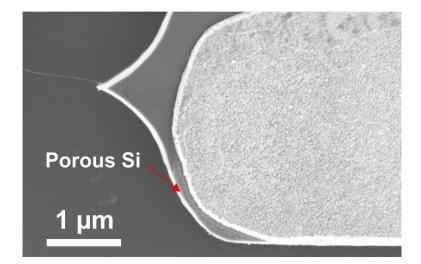

#### 3.4.4. Liquid HF release

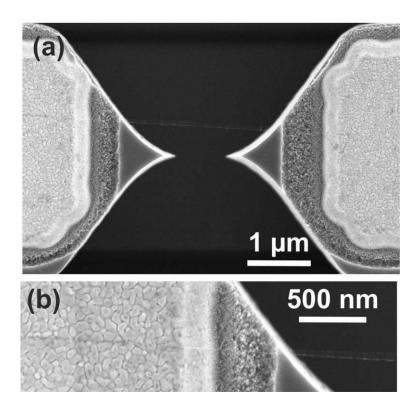

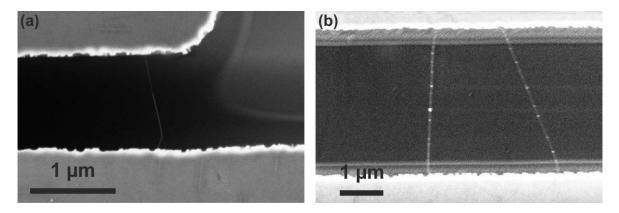

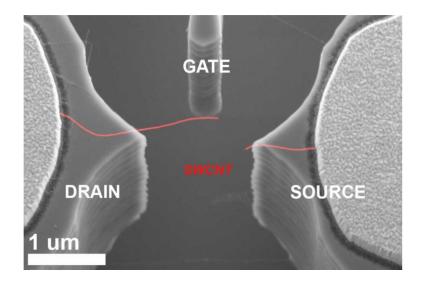

If a CNT is properly clamped at both ends, it can remain in the same position during liquid HF release and will become suspended after release. A released CNT is shown in Figure 3-7a [55]. The two ends of the suspended CNT were clamped by the metal leads on the Si electrodes. A clamped-clamped configuration is indicated by the CNT trace extending into the metal lead (Figure 3-7b [55]). The robust clamping can provide sufficient clamping

Figure 3-7 (a) A suspended CNT across a gap between two Si electrodes [55]; (b) close-up of the clamping site on the left Si electrode shown in (a) [55]. A doubly-clamped configuration is indicated by the CNT trace extending into the contact region. The porous structures seen around the metal leads are likely to be porous silicon structures, resulting from the galvanic effect during liquid HF etching (D#13\_C#SOIC3-R2C1). ©2011, IEEE

Figure 3-8 Two different gate configuration; (a) a suspended CNT with single Si side-gate; (b) a suspended CNT with double Si side-gates (a:  $D#20-5A_C#SOIC3-R3C2/$  b:  $D#23-4c_C#SOIC3-R3C5$ ).

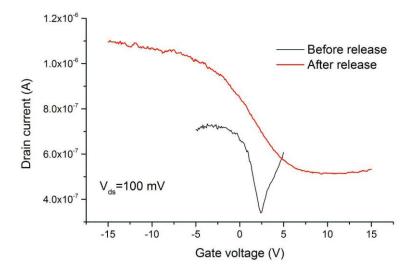

force to hold the CNT in position during the release and drying procedures. Moreover, the robust mechanical clamping can prevent the CNT from sliding while it is strained by a MEMS actuator during operation (see section 5.1). The porous structures surrounding the metal leads seen in Figure 3-7 are likely porous Si. The porous Si structures resulted by a so-called galvanic effect [56], occurring in liquid HF etching when both Au and heavily-doped Si are present. Using the integration process, a suspended CNT can be equipped with single or double side-gates, as shown in Figure 3-8.

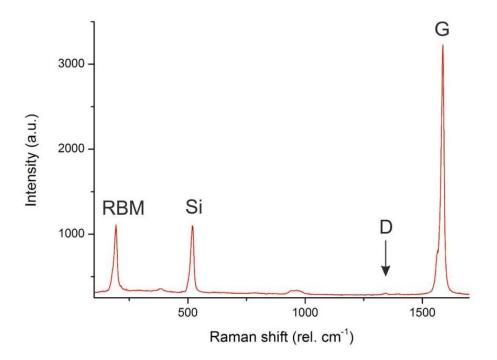

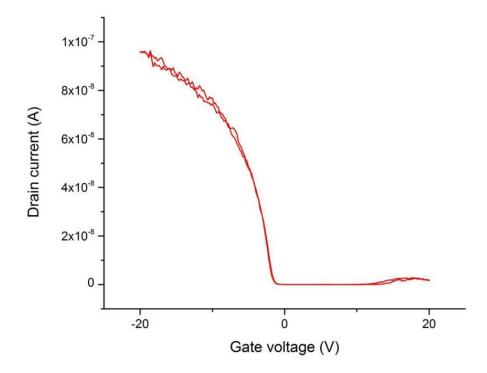

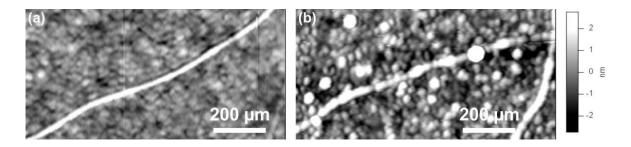

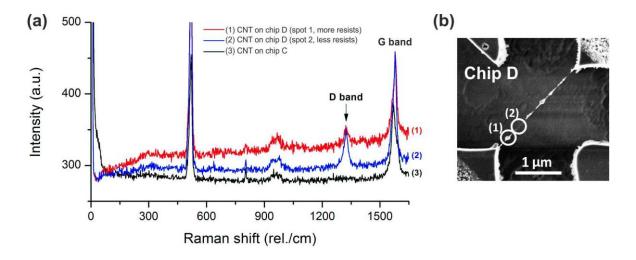

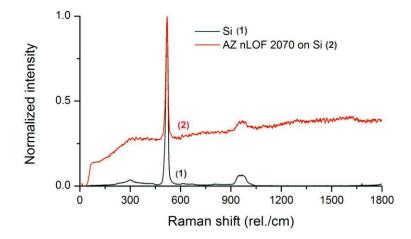

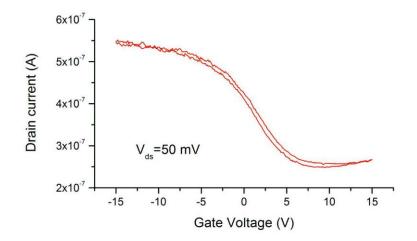

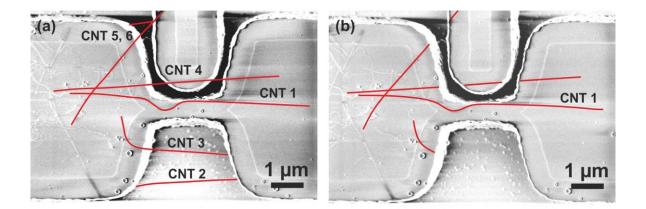

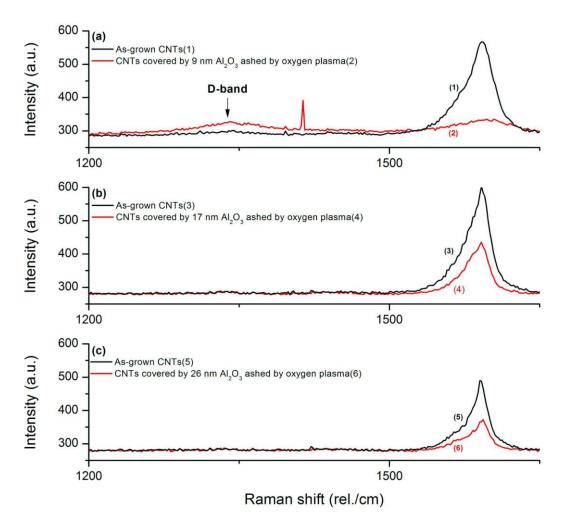

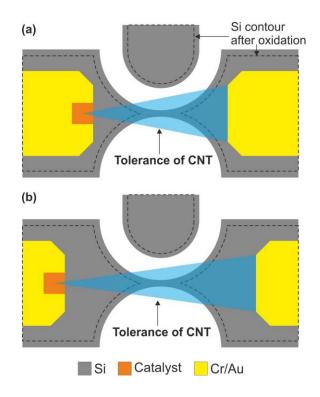

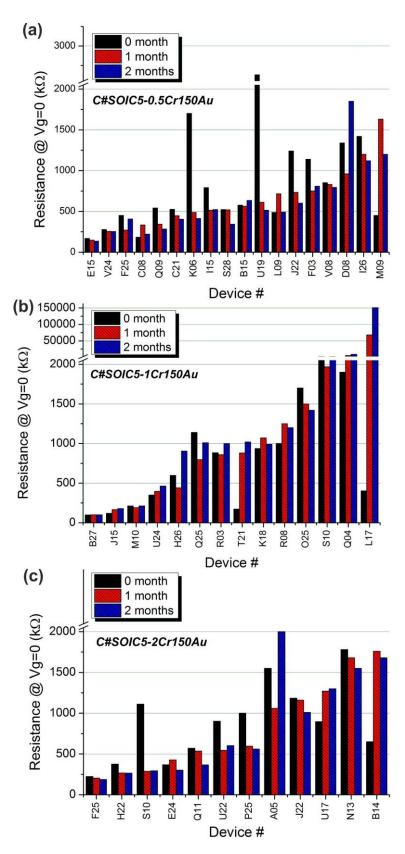

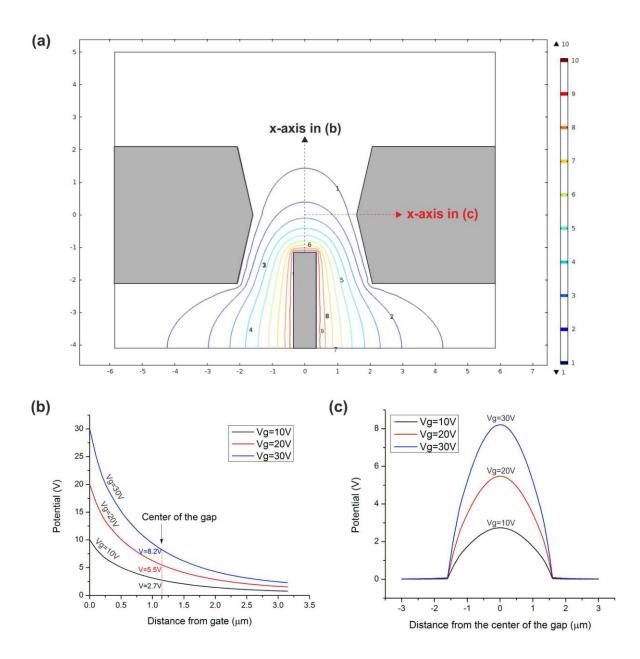

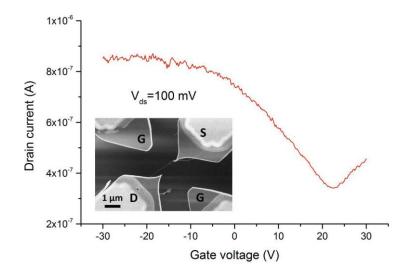

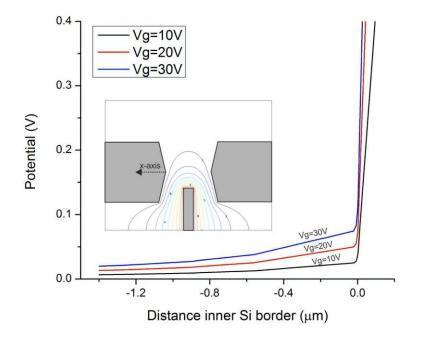

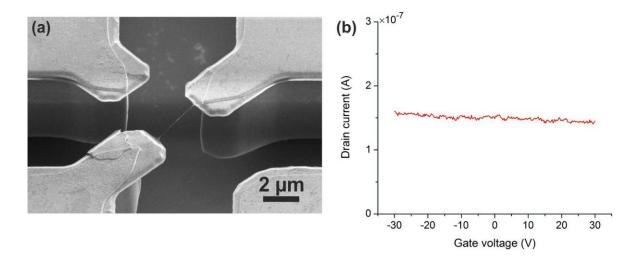

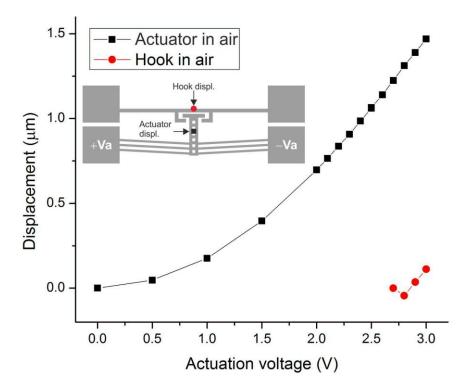

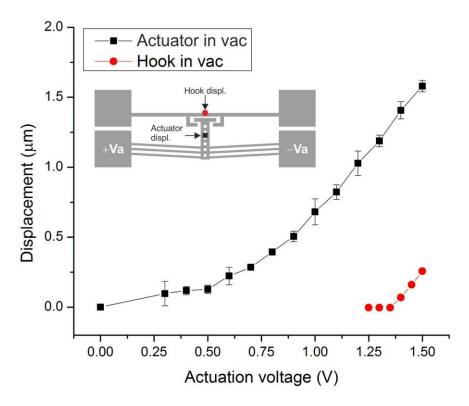

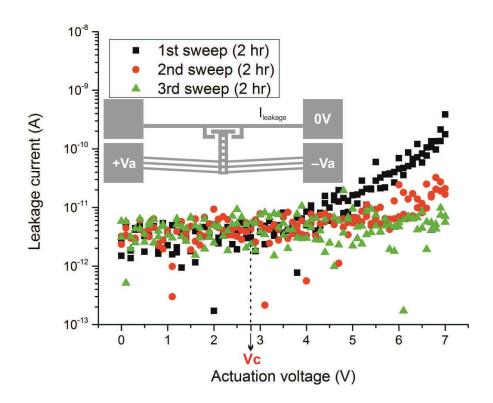

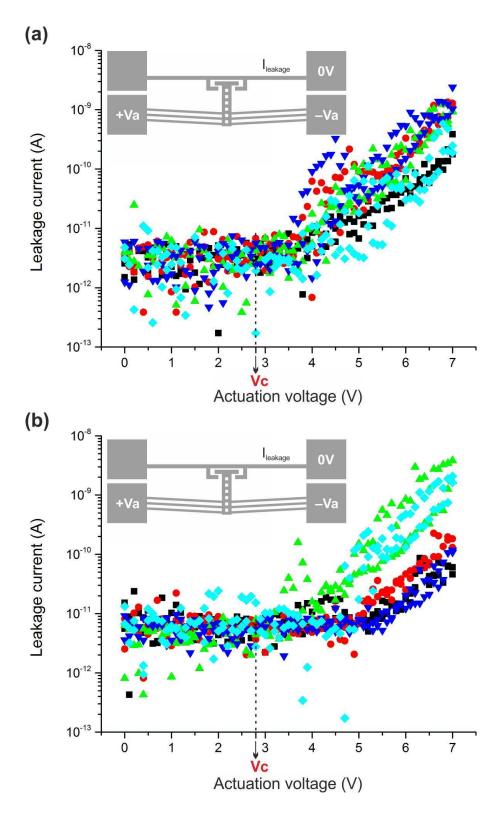

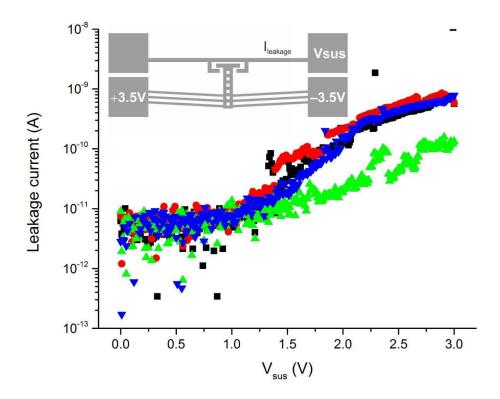

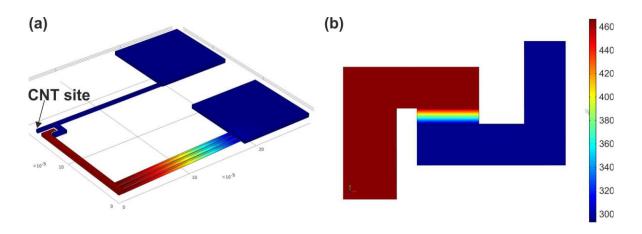

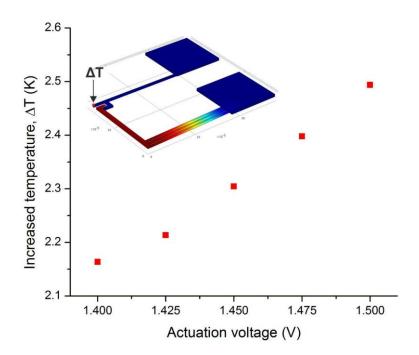

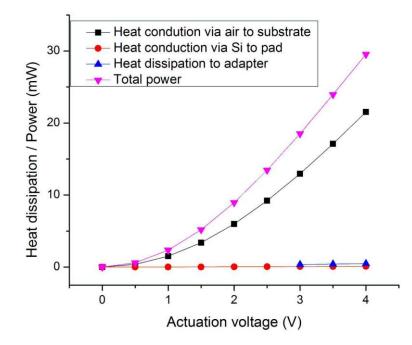

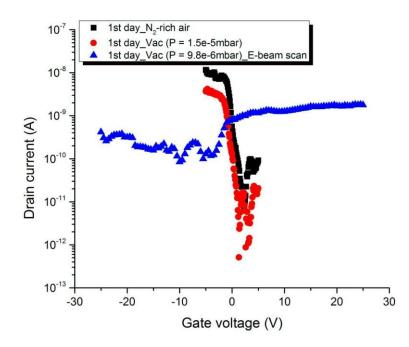

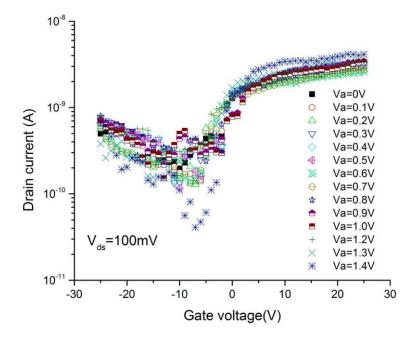

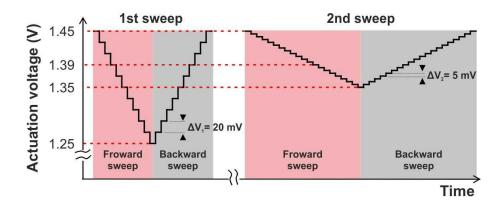

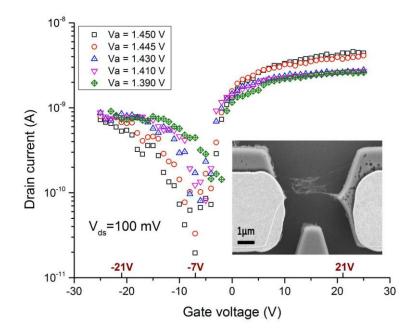

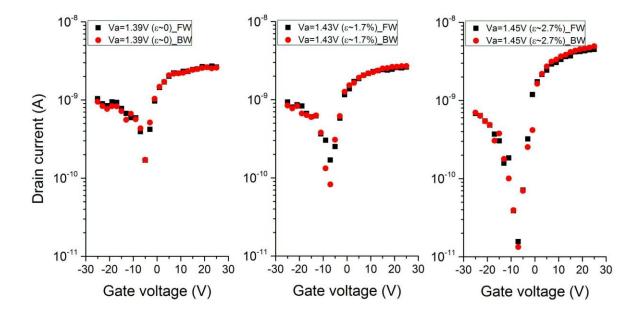

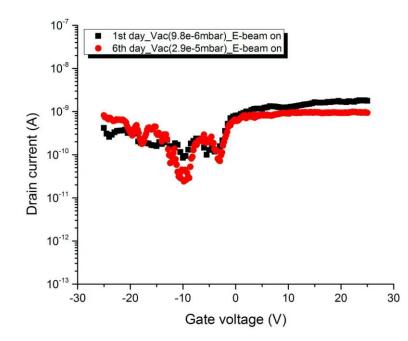

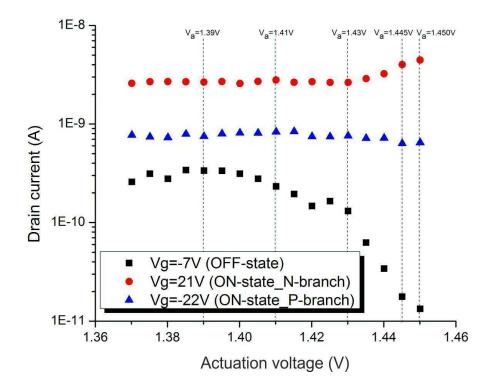

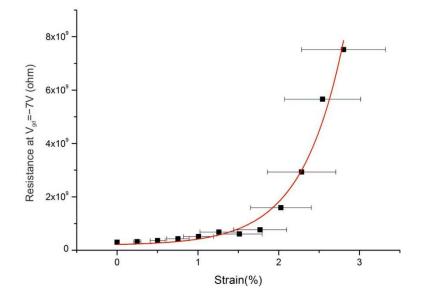

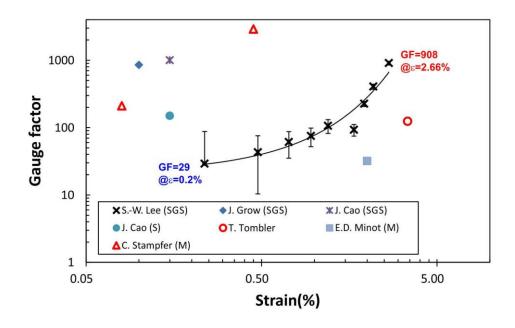

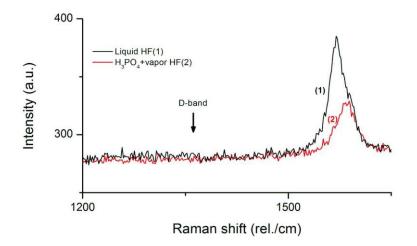

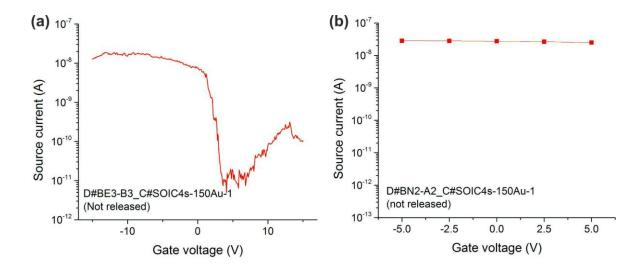

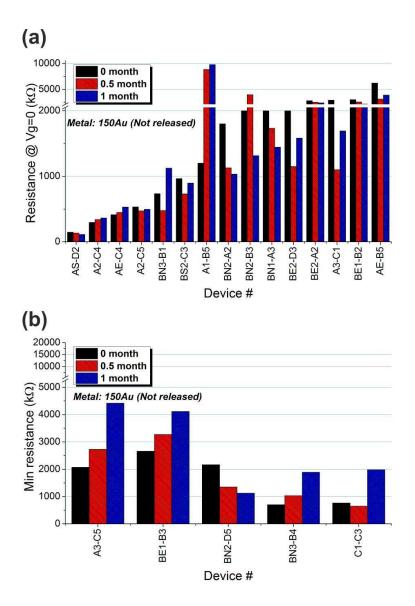

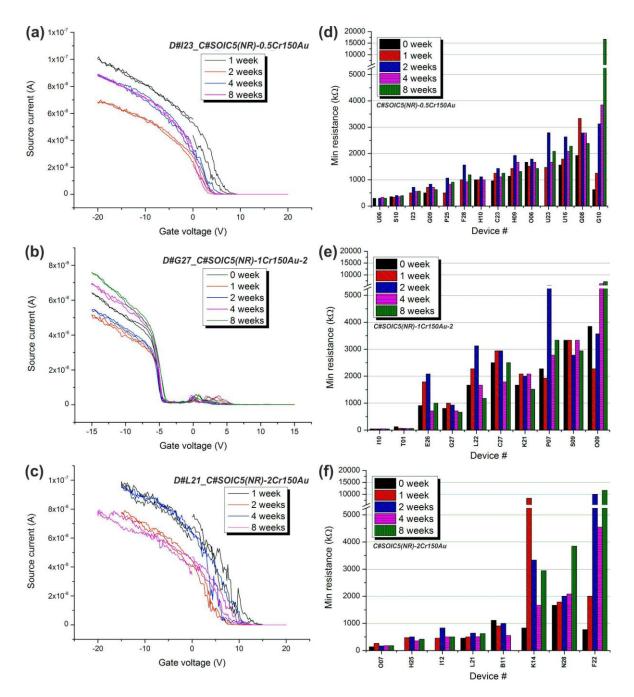

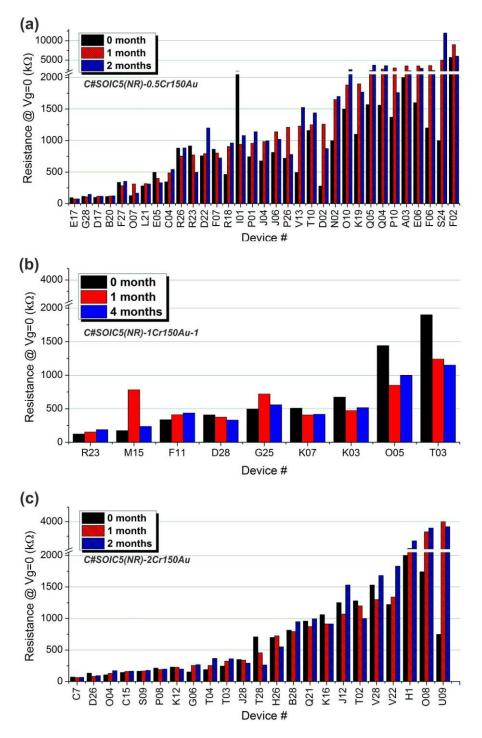

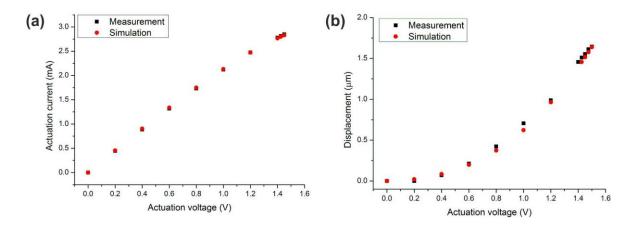

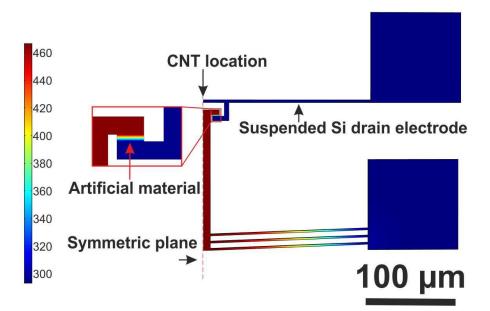

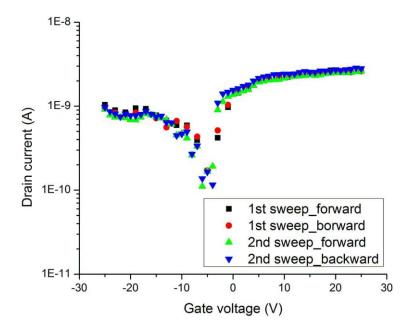

#### 3.5. Characterization