# A fully-functional Cache Control Coprocessor for Enzian

**Master Thesis**

Author(s): Hässig, Manuel

Publication date: 2024

Permanent link: https://doi.org/10.3929/ethz-b-000708595

Rights / license: In Copyright - Non-Commercial Use Permitted

## Master's Thesis Nr. 487

Systems Group, Department of Computer Science, ETH Zurich

A fully-functional Cache Control Coprocessor for Enzian

by Manuel Hässig

Supervised by

Ben Fiedler Prof. Dr. Timothy Roscoe

October 2023-May 2024

## DINFK

#### Abstract

The Enzian research computer offers a unique platform for testing novel cache coherence protocols in hardware with its 48-core ThunderX CPU and FPGA connected over a coherent interconnect with the Enzian Coherent Interface (ECI). The C3 system is a toolkit for experimenting with novel features of cache coherence protocols on Enzian. It consists of a Cache Control Coprocessor (C3) on an isolated CPU core to fetch instructions from the C3 envoy on the FPGA to execute. Applications on the FPGA can issue C3 instructions to the C3 envoy which will then be executed by the C3 on the CPU. This namely enables injecting an FPGA-homed cache line into the CPU L2 cache and expressing prefetching patterns for CPU memory by the FPGA when it has knowledge of the CPU's execution, e.g. when the FPGA transfers data which needs to be handled by the CPU. Further, the C3 enables the FPGA to interrupt CPU cores using C3 instructions which result in software generated interrupts when executed by the C3. The C3 system is designed to be extensible such that it can be used to implement other features not implemented by the native cache coherence protocol to allow prototyping novel coherence features in hardware. The interface of C3 on the FPGA is designed to be similar to the interface of ECI to imitate a cache coherence protocol. The C3 is implemented as an out-of-tree Linux kernel module and provides notifications as an interface to CPU applications to let them know when an FPGA applications sent notification instructions the let them know that data has arrived for the application to consume.

#### Acknowledgements

First of all, I would like to thank my advisor Ben Fiedler for his support and guidance and many fruitful discussions which improved this thesis considerably. I would also like to thank Prof. Timothy Roscoe for the opportunity to work on this interesting but nonetheless challenging subject. Further, I would like to thank Pencheng Xu for being a more or less willing rubber duck and a very competent help in all things FPGA; Jasmin Schult for sharing her wealth of knowledge on the hidden secrets of the ThunderX caches and making sure that I do not sprint the marathon distance; Roman Meier for all his IT-support and thoughtful reviews; David Cock for the clarity provided by his insights; Adam Turowski for his support with puzzling FPGA problems; and Nicolas Tischler for his help with figuring out how to allocate more SGIs. I would also like to thank the Systems Groups as whole for being such a collaborative environment and for facilitating many interesting lunchtime discussions.

Lastly, I would like to thank Ibuprofen for getting me through the last three days before my deadline in spite of fevers and headaches.

## Contents

| Acronyms 5         |                                   |                          |                                                              |                          |  |  |  |

|--------------------|-----------------------------------|--------------------------|--------------------------------------------------------------|--------------------------|--|--|--|

| 1                  | <b>Intro</b><br>1.1<br>1.2<br>1.3 |                          | <b>n</b><br>d Work                                           | <b>7</b><br>9<br>9<br>11 |  |  |  |

| 2                  | 2 Background                      |                          |                                                              |                          |  |  |  |

|                    | 2.1                               | CPU C<br>2.1.1<br>2.1.2  | Caches                                                       | $13 \\ 15 \\ 15$         |  |  |  |

|                    | 2.2                               | $2.2.1 \\ 2.2.2$         | ThunderX                                                     | 16<br>17<br>20           |  |  |  |

|                    | 2.3                               | 2.2.3<br>Enzian<br>2.3.1 | Enzian Coherent Interface                                    | 21<br>21<br>22           |  |  |  |

| 3 System Design    |                                   |                          |                                                              |                          |  |  |  |

|                    | 3.1                               |                          | Requirements                                                 | 24                       |  |  |  |

|                    | 3.2                               | 0                        | sign                                                         | 24                       |  |  |  |

|                    |                                   | 3.2.1                    | Control Path                                                 | 25                       |  |  |  |

|                    |                                   | 3.2.2                    | Data Path                                                    | 28                       |  |  |  |

| 3.3 Key Mechanisms |                                   | Key M                    | lechanisms                                                   | 29                       |  |  |  |

|                    |                                   | 3.3.1                    | Direct Cache Injection                                       | 29                       |  |  |  |

|                    |                                   | 3.3.2                    | Cache Allocation                                             | 39                       |  |  |  |

|                    |                                   | 3.3.3                    | Core Isolation                                               | 40                       |  |  |  |

|                    | 3.4                               |                          | tructions                                                    | 42                       |  |  |  |

|                    |                                   | 3.4.1                    | Encoding                                                     | 42                       |  |  |  |

|                    |                                   | 3.4.2                    | Instruction Descriptions                                     | 44                       |  |  |  |

|                    | 3.5                               | • •                      | ation Interface                                              | 49                       |  |  |  |

|                    |                                   | 3.5.1                    | Application Registration                                     | 49                       |  |  |  |

|                    |                                   | 3.5.2                    | Notifications                                                | 50                       |  |  |  |

|                    | 3.6                               | 0                        | ronization                                                   | 54                       |  |  |  |

|                    |                                   | 3.6.1                    | Provided Guarantees                                          | 54<br>54                 |  |  |  |

|                    |                                   | 3.6.2                    | Synchronization Contract between CPU and FPGA applications . | 54                       |  |  |  |

|                                                                      | 3.7 | Summary                                                      | 55 |  |  |  |

|----------------------------------------------------------------------|-----|--------------------------------------------------------------|----|--|--|--|

| 4                                                                    | Imp | nplementation 5                                              |    |  |  |  |

|                                                                      | 4.1 | Infrastructure                                               | 57 |  |  |  |

|                                                                      |     | 4.1.1 Getting as suitable Linux Kernel                       | 57 |  |  |  |

|                                                                      |     | 4.1.2 Enzian FPGA Driver                                     | 59 |  |  |  |

|                                                                      |     | 4.1.3 Enzian ThunderX Driver                                 | 59 |  |  |  |

|                                                                      |     | 4.1.4 Enzian Memory Explorer                                 | 63 |  |  |  |

|                                                                      | 4.2 | Cache Control Coprocessor                                    | 65 |  |  |  |

|                                                                      |     | 4.2.1 Setup & Core Isolation                                 | 65 |  |  |  |

|                                                                      |     | 4.2.2 C3 Loop                                                | 66 |  |  |  |

|                                                                      |     | 4.2.3 Notifications & Interface to User                      | 67 |  |  |  |

|                                                                      | 4.3 | C3 FPGA Envoy                                                | 70 |  |  |  |

|                                                                      | 4.4 | FPGA Test Applications                                       | 71 |  |  |  |

|                                                                      |     | 4.4.1 No Instruction Test                                    | 71 |  |  |  |

|                                                                      |     | 4.4.2 Fixed Instruction Test                                 | 71 |  |  |  |

|                                                                      |     | 4.4.3 Dynamic Instruction Test                               | 72 |  |  |  |

|                                                                      |     | 4.4.4 Copy Word Test                                         | 73 |  |  |  |

|                                                                      |     | 4.4.5 DCS Copy Word Test                                     | 75 |  |  |  |

| 5                                                                    | Eva | Evaluation                                                   |    |  |  |  |

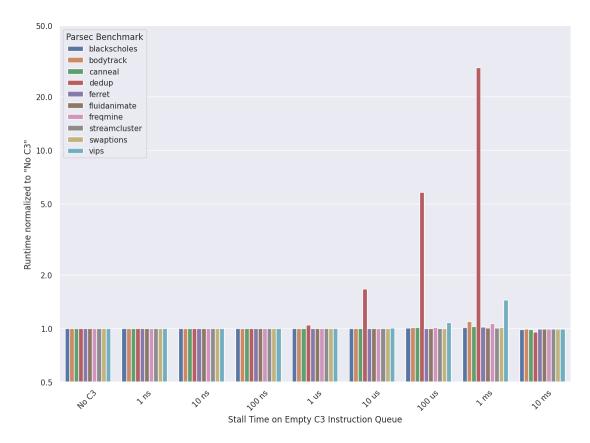

| 5.1 The Influence of Stalling Instruction Fetches on the Rest of the |     |                                                              | 80 |  |  |  |

|                                                                      | 5.2 | Future Tests                                                 | 83 |  |  |  |

| 6                                                                    | Con | Conclusion                                                   |    |  |  |  |

|                                                                      | 6.1 | Discussion                                                   | 85 |  |  |  |

|                                                                      |     | 6.1.1 Is C3 a convincing Cache Coherence Protocol Extension? | 85 |  |  |  |

|                                                                      |     | 6.1.2 Viability as a Platform for Experimentation            | 86 |  |  |  |

|                                                                      | 6.2 | Future Work                                                  | 87 |  |  |  |

|                                                                      | 6.3 | Summary                                                      | 88 |  |  |  |

| Α                                                                    | Enz | ian Memory Explorer Help Page                                | 97 |  |  |  |

### Acronyms

- **ATF** ARM Trusted Firmware 60, 62

- **AXI** Advanced eXtensible Interface 22, 70–72, 75, 76, 78

- **BRAM** block random access memory 28, 75, 76, 78

- **C3** Cache Control Coprocessor 8–12, 24–29, 34, 35, 38–58, 62, 65–74, 76, 78, 80–89

- **CCPI** Cavium Coherent Processor Interconnect 17, 18, 21

- **CMI** Coherent Memory Interconnect 17

- **DC** directory controller 7, 21–23, 61

- **DCS** directory controller slice 22, 28, 29, 33, 34, 46, 74–79, 83, 85, 86

- **DDIO** Data Direct I/O 8, 10

- **DMA** direct memory access 10, 24

- **DRAM** dynamic random access memory 18, 19, 21, 22, 28, 30, 34, 35, 41, 43, 58, 59, 63, 65, 76

- ECI Enzian Coherent Interconnect 7–10, 17, 20–26, 28, 63, 70, 72, 78, 85, 86, 88

- **FIFO** first-in, first-out 26, 27, 70, 78

- **FPGA** field programmable gate array 7–11, 16, 17, 20–22, 24–29, 33–38, 40–49, 52–56, 59, 61, 63, 65, 70–74, 76, 80, 83, 85–89

- **GIC** generic interrupt controller 25, 48, 62

- **GPIO** general purpose input/output 25

- HDL hardware description language 76

- **I/O** input/output 8, 10, 11, 18–20, 25, 26, 39–42, 59, 63, 70, 72, 87

- **ILA** integrated logic analyzer 70, 78

- **IOB** I/O-bridge 17, 19, 47

**IP** intellectual property 70, 76

**IPC** interprocess communication 41

**IPI** inter-processor interrupt 62

**IRQ** interrupt request 40, 62, 63, 65

**ISA** instruction set architecture 29, 33, 42

LCI local clean invalidate 22, 75, 76, 78

LCIA local clean invalidate acknowledgement 22, 75, 78

**LLC** last level cache 8, 10, 17

**MUX** multiplexer 27

NIC network interface card 8, 10, 11, 25, 55, 87

**NOP** no operation 19, 32, 34, 44, 66, 67, 71

${\sf NUMA}$  non-uniform memory access 16, 59

RCU Read, Copy, Update 40, 58

**REPL** read-evaluate-print-loop 63, 64

**RPC** remote procedure call 8

**SGI** software generated interrupt 8, 27, 41, 47–49, 53, 55, 62, 63, 65, 66, 69, 89 **SMP** simultaneous multiprocessing 40, 62

**TLB** translation lookaside buffer 18, 30, 31, 34–38, 41, 61

**UL** unlock 22, 75, 85

${\sf UMP}$  user-level message passing 10, 27, 41, 51–53

**UND** UMP-like Notification Delivery 51–53, 55, 68

**URPC** user-level RPC 10, 51

**VC** virtual channel 22, 23, 78, 85, 86

**VM** virtual machine 11

**WNS** worst negative slack 78

## **1** Introduction

Workloads on CPUs had enjoyed "free" speedups from the exponential increase of transistor count predicted by Moore's law [46] and the increase of processor frequencies and reduction of transistor with the same power consumption from Dennard scaling [18]. Consequently, chip manufacturers were able to deliver better performance by only optimizing CPUs. As Moore's law and Dennard scaling have ended [21] the overheads of general purpose CPUs [16] become less tolerable and the remaining way to get better performance is via domain specific hardware [28]. This drives an increasing heterogeneity in hardware [60]. However, memory dominates these accelerators [15]. In a sense, they move the memory transfer from inside the CPU to the interconnect between all processing elements. Unsurprisingly, these interconnects become the bottleneck for performance of accelerated systems [67, 27, 42].

The pressure for performance and features lead to the development of the more general proposals OpenCAPI [57], GenZ [30], and CCIX [9], which have merged into CXL [11], as well as the GPU specific NVIDIA NVLink [24], and AMD Infinity Fabric [7] and RISC-V TileLink [55]. All of these new interconnects offer coherent memory access in some shape or form. The ongoing specialization seems to also have moved coherent memory as an essential guarantee for multiprocessing out of the CPU.

In order to enable relevant systems research on heterogeneous systems in light of this paradigm shift the Systems Group developed the *Enzian research computer* [10]. Enzian is a two-socket asymmetric NUMA system with a 48-core ThunderX ARMv8 CPU on one socket and a Xilinx UltraScale+ field programmable gate array (FPGA) on the other. The two are connected with a coherent interconnect running Enzian Coherent Interconnect (ECI) [52], which implements the CPUs native cache coherence protocol. Additionally, CCKit [51] provides an implementation of a directory controller (DC) on the FPGA such that it participates as a home agent, making it a symmetric cache coherence protocol to applications on the FPGA.

This makes Enzian an ideal platform for evaluating future cache coherence protocols on real hardware as it provides introspection down to the transport protocol of coherence messages. However, while being representative of the current state of the art in coherent interconnects ECI does not have all features which might be desirable in a coherence protocol, such as pushing a cache line from the FPGA in to the CPU L2 cache. The goal of this work is thus to provide a comprehensive toolkit to enable additional features of a coherence protocol on Enzian.

Managing caches effectively is essential for getting good performance on modern computer systems. If we want to write a fast matrix-matrix-multiplication for instance, we need to take into account the dimensions, associativity, and replacement policy of each level of the CPUs cache hierarchy and block our data accordingly. Despite this need, caches on CPUs are intentionally transparent to software. As caches effectively hide most memory latency, leveraging them to the fullest for transferring data to and from accelerators could yield significant benefits.

Caches work best, when we know which memory will be accessed next and *prefetch* that memory into the cache ahead of the access so we can evade the not so compulsory miss. Applying this idea to the data transfer from accelerators, we notice that when transferring data back to the CPU the accelerator knows that the CPU will access the memory it transfers in the near future. Therefore, it would ideally transfer the data directly into the CPU's cache in a form of *push-prefetching* or direct cache injection. Because data movement is among the most expensive and energy-consuming tasks in a data center [14] and the latency sensitivity of short-lived workloads like serverless functions and remote procedure calls (RPCs), these workloads should benefit from push-prefetching as a feature in a coherence protocol. Further, some input/output (I/O) bound workloads using accelerated devices like a smart network interface card (NIC) profit from the reduced latency due to direct cache access, as demonstrated previously using Intel's Data Direct I/O (DDIO) technology [22]. Thus, the main additional feature we provide is direct cache access for the FPGA on Enzian.

We introduce the Cache Control Coprocessor (C3) which gets around the issue that ECI can only pull cache lines from a different node and not push them to another node. Thus, we need to send a message from the FPGA to the CPU to pull a cache line into its last level cache (LLC). For this, we create an instruction queue on the FPGA and have the CPU poll that queue continuously. In order to minimize latency, we isolate a CPU core to only poll the instruction queue and execute the instructions.

Now that we have a side channel for the FPGA to make the CPU execute things on its behalf, we can also implement other useful things. For instance, the FPGA can direct the CPU to issue a software generated interrupt (SGI). This is useful on Enzian as, at the time of writing, the workings of the interrupt lines between the FPGA and the CPU have not been deciphered yet. Hence, until these interrupt lines between the two nodes are brought up, C3 can be used as a workaround.

In this work, we design C3 as a flexible system other work can use to easily add features to Enzian not possible to implement properly or as a way to prototype new mechanisms. To that end C3 is extensible by design and makes few assumptions about applications using it. We apply the Enzianeering credo "if in doubt, overengineer" [10]. For the core

features direct cache access and interrupts, we investigate how these are accomplished best on Enzian. After implementing C3, we use simple applications to characterize the latency and throughput of direct cache access and draw conclusions as to how the system is best used in applications. Based on these conclusions, we devise a handful of different usages of our system for different application needs and show possible improvements.

#### 1.1 Goals

Our main goal in this work is to create a reusable system component to enable new operations in communication from the FPGA to the CPU on Enzian in the form of the C3 system. The overarching goal is to be able to prototype coherent interconnects with a superset of the features of ECI on Enzian and enable experimentation with those novel features.

Initially, C3 should support push-prefetching of cache lines from the FPGA to the CPU L2 cache, some form of notification that data has been transferred, and the ability to interrupt CPU cores from the FPGA. In order to make push-prefetching over C3 useful, we aim to make the implementation of C3 have as low latency as possible.

To facilitate easy usage in the future, we provide guidelines and examples for applications.

#### 1.2 Related Work

Coherence interconnect prototyping In recent years many new coherent interconnects have been introduced with CXL [11], NVIDIA NVLink [24], and AMD InfinityFabric [7], illustrating the considerable interest in coherent inter-chip data movement. However, these technologies are neither built for experimentation, extensibility, or introspection. While they are useful points in the design space, they do not allow exploring the design space of coherent interconnects. Much closer to that goal comes BlackParrot [49] with its BedRock cache coherence system [63]. BlackParrot can be implemented as a soft core on an FPGA based on the source code available on GitHub, which allows for experimentation, extensibility, and introspection. Even when taped out, the BedRock protocol in BlackParrot can be reconfigured with a firmware update as it is microprogrammed. For instance, it can be configured to use different subsets of the MOESIF states as protocol states of the coherence protocol. RISC-V TileLink [55] is also an open standard for a coherent interconnect which could lend itself to being extended due to its relative simplicity. If implemented on an FPGA, one could then also get introspection. The Enzian research computer [10] with its implementation of ECI on the FPGA is designed for introspection to the lowest levels. However, the coherence protocol is constrained to that of the CPU, which is why this work is needed for Enzian to be extensible.

Hiding memory latency using cache prefetching is an old idea now commonly implemented in chips as hardware prefetchers and generally available on CPUs [36, 45, 8]. However, hiding latency by having a core push cache lines into another cores cache with pushprefetching or cache injection [35, 44] is much less common. Both ideas are similar in nature, but cache injection is producer-driven and fails if data is fetched to early evicting the applications working set, while prefetching is consumer-driven and fails if data is transferred too late [38]. Different approaches for push-prefetching in CPUs as surveyed by Byna et al. [8] include run-ahead execution, helper-thread-based prefetching, memoryside prefetching using near memory computation [66], and server-based prefetching. The Stanford DASH multiprocessor [37] featured the *deliver* and *update-write* operations for applications that cannot issue a prefetch early enough and thus need push-prefetching. *Update-write* sends data to all cores that have the updated cache line cached and *deliver* sends data to a specified set of cores.

Push-prefetching seems to be more prevalent for accelerated computing where knowledge of future data transfers from one to the other node are leveraged, which is the realm where C3 will be used. In this context, the goal of using push-prefetching is to achieve lower data transfer latencies than using direct memory access (DMA) by avoiding reading data from main memory. For instance in proactively pushing data from the CPU to the GPU, so the GPU will mostly hit when it starts processing data [68]. There has also been considerable work on direct cache access for NICs [31, 33, 58]. The study by Farshin et al. [22] based on Intel's DDIO technology on Xeon server CPUs [32] shows that not all applications benefit equally from direct cache access and it has to be tuned specifically to each application. In particular, they showed experimentally that contention in the LLC between code/data and I/O is a problem and therefore the two need to be separated, which has been shown previously in simulation by Tang et al. [59]. Wang et al. [62] reverse-engineered and modelled DDIO in detail and found that the increasing complexity of the memory subsystem and I/O stacks make leveraging direct cache access to the fullest difficult. Further, they found that the increasing complexity of coherence protocols and the overhead of on-chip networks blur the distinction between a cache hit and a cache miss leading to diminishing returns. C3 aims to get around this penalty by using existing mechanisms in ThunderX.

Polling memory for achieving low-latency I/O in the same way as C3 is polling the FPGA for instructions is a well-known technique. However, many times the benefit comes from bypassing the kernel. Barrelfish [3] uses polling shared memory for user-level message passing (UMP), its user-level RPC (URPC) [5] based cross-core communication mechanism which achieves a latency in the order of hundreds of cycles for communication

across different NUMA systems. For Barrelfish, polling for a long time is unreasonable as it would block progress for the rest of the core, so it blocks after some time. However, systems for accelerating I/O to the CPU dedicate an entire core to polling. The Virtualization Polling Engine [41] uses dedicated polling threads on dedicated CPU cores to access devices and provide virtual access points over cache-coherent memory to virtual machines (VMs) instead of using interrupts, which significantly reduces the virtualization overhead. In networking DPDK [50] uses poll mode drivers to bypass the kernel network stacks to reduce latency. DPDK is used by Azure with its SmartNICs [23]. Andromeda [17] achieves its lowest TCP roundtrip latency using dedicated busy-polling CPUs, but achieves higher throughput at slightly lower latency using Intel's QuickData DMA Engines, which enable larger data copies. Shenango [48] dedicates a core to kernel-bypassing I/O with NICs which exposes packet queues to applications that are reallocated to cores on very short time frames in order to increase CPU efficiency. As an alternative to userspace polling on dedicated cores, Basu et al. propose compiler interrupts [2]. A compiler interrupt is a call to an interrupt handler inserted into a binary at compile time based on a configured interrupt interval. As a case-study, they replaced Shenango's dedicated I/O core with compiler interrupts and showed that they could increase CPU efficiency with comparable throughput and latency.

In most offloading scenarios, the CPU instructs the accelerator what it should execute and the accelerator tells the CPU when it is done. C3 inverts this relationship and has the FPGA issue instructions to execute on the CPU. This is not unique as Elis et al. [20] recently proposed a similar notification mechanism between GPUs and CPUs to achieve higher parallelism between the two. However, this is mainly focussed on synchronization. Closer to C3 are GPU-to-CPU callbacks [56] where the CPU polls pinned memory where the GPU writes a callback. A callback can be a system call, a memory transfer or some CPU compute. There are synchronous callbacks, where the issuing GPU thread spins until the request completes, and asynchronous callbacks where synchronization needs to happen some time after the request.

#### 1.3 Following Along

Throughout this thesis, if you, dear reader, have access to an Enzian you can follow along and execute the experiments. Whenever this is the case you will find a box with the information needed to run the experiment. While the readme in each project should be self-explanatory, we will go through some general setup steps here.

First, all projects in this thesis need a newer Linux kernel than provided in the Enzian golden images. Everything was built using an image on a custom debug configuration based on Linux 6.7.1, but any 6.x kernel should work. You can obtain a copy of the image with the custom debug kernel using the following command on enzian-gateway:

emg copy-image mhaessig-6.7.1-enzian-debug \$IMAGE\_NAME

For general information on how to boot an Enzian, please refer to the Enzian Quickstart Guide. For the experiments, we boot an Enzian with core 47 isolated, which is where the C3 will be placed. Use the following command on enzian-gateway to boot an Enzian with core 47 isolated and the debug build of Linux 6.7.1:

```

emg acquire -n $IMAGE_NAME -k mhaessig/vmlinuz-6.7.1-enzian-debug \

-i mhaessig/initrd.img-6.7.1-enzian-debug \

-a "isolcpus=nohz,domain,managed_irq,47 nohz_full=47 rcu_nocbs=47 \

rcu_nocb_poll" zuestoll$NR

```

Most experiments will need some specific bitstream programmed on the FPGA. Every experiment will specify the bitstream needed. All FPGA projects can be found in the Gitlab group for this thesis.

Once you have yourself a running Enzian, you need to build the C3 Kernel Modules. This "monorepo" contains all needed kernel modules, libraries and scripts. Build all its contents with make. All scripts you run to start an experiment must be run in the root directory of this repository.

With all this preparation, you should be ready for your first experiment.

```

Following along: Experiment 1.1: Welcome

```

Required bitstream: None Script: experiments/welcome.sh What you will see: A welcoming text and some information about the core you are running on.

## 2 Background

This chapter will cover a range of topics used later in this thesis. The content covered in each topic is limited to what is relevant for this work.

#### 2.1 CPU Caches

As the performance improvements of CPUs outpaced the memory subsystem, designers were forced to come up with a solution to the higher relative cost of memory access. The solution was to introduce a smaller but faster memory close to the CPU that stores blocks of memory the CPU accessed recently. This solution worked to increase the speed of memory accesses as the approach exploits the temporal and spatial locality inherent in programs, i.e. in loops accessing an array.

The simplest form of a cache is a *direct-mapped* cache which is basically an array of n blocks, called *sets*, of m bytes, which is the *line size*. To access the cache one takes the *index* of  $\log_2(n)$  bits starting at bit  $\log_2(m)$  of the address into the cache. If valid data is present in the specified cache set, the cache has to check if it is the same line as requested. It does this by comparing the *cache tag* stored in the cache and the most significant  $64 - \log_2(n) - \log_2(m)$  bits of the address. If the tags match, the cache access is a *hit*. Otherwise, it is a *miss* and the cache replaces the line by evicting the cached line and fetching the requested line from main memory. To facilitate this functionality each cache line must store the tag, a valid bit, and the actual data. The hardware to check if the access into the cache is a hit in a direct-mapped cache is a comparator to compare the tag cached at the address-provided index with the tag of the address and an AND-gate to check if the valid bit is set if the tags match. This makes access incredibly easy and fast, but this simplicity comes at a cost. Direct-mapped caches encounter many *conflict misses*, where a cache line is evicted from the cache because a different cache line for the same set is requested.

When evicting a cache line, the cache has to decide which line to evict. This is also straightforward in a direct-mapped cache as there is only one option. Then the hardware must make sure that the contents of the cache line are written back to memory if the line is *dirty*, i.e. it has been modified since it was fetched. However, there are two ways of ensuring that changes in the cache are reflected in memory. A *write-through* cache writes changes to memory immediately, while a *write-back* cache waits until the line is evicted to write the changes to memory. The trade-off between these two policies is that the former makes writes to the cache as slow as writing to memory but simplifies eviction, whereas the latter makes writes to the cache much faster but increases the miss penalty when a line has to be evicted.

In order to further exploit temporal locality and increase the size of a continuous working set, designers introduced *set-associative* caches where each set has a number of *ways* so multiple cache lines per set can be cached. For example a 2-way set-associative cache can store two cache lines of the same set before the request for a third cache line has to evict one of the two lines. On the opposite side on the set-associativity spectrum of a direct-mapped cache is a *fully-associative cache* which has one set and n ways, so an arbitrary memory location might be cached in any of the cache lines. The multitude of ways, however, makes the access much more complicated as the address-tag has to be compared with all tags in the cache set. This requires more hardware and more time and neatly demonstrates the trade-off for the set-associativity of a cache between hit rate and access time.

With multiple cache lines per set, the cache must pick a line to evict when all ways in a set are filled and a conflict miss occurs using a *replacement policy*. There are a host of different policies with varying levels of complexity. For instance, random replacement is quite simple as it needs no additional state stored in the cache line. There are simple queue-based policies with FIFO and LIFO. The least-recently-used policy and related policies evict the oldest line in the cache and needs to track the age of cache lines, which needs at least  $\log_2$  bits for the number of ways for each cache line and logic to update the age bits. The family of frequency based policies uses the least-frequently used heuristic that needs to track the number of accesses per line and compare them on replacement.

The performance of replacement policies is analyzed by comparing them with the optimal replacement algorithm with perfect foresight, the clairvoyant Bélády's algorithm [4]. This policy replaces the line which will not be accessed again for the longest time in the future.

Since caches performance can be significantly improved by having foresight into what accesses will be made in the future, most caches implement some sort of *prefetching*. Some CPUs have hardware prefetchers that make predictions on future accesses and proactively fetch lines into the cache. CPUs also feature prefetching instructions which allow the programmer to inform the cache that some cache line will be needed in the future. However, in most architectures these prefetching instructions are implemented as performance hints and the CPU may ignore them entirely. For a comprehensive survey of prefetching techniques for CPU caches, see Mittal [45]. Further, Lee, Kim, and Vuduc [36] provide an analysis when prefetching is beneficial.

#### 2.1.1 Cache Hierarchies

With time memories grew ever larger and with them the working sets of programs. Therefore, caches also had to grow. While a cache with low associativity will scale without too much increase in access latency, highly associative caches will not due to their need to compare cache tags in order to determine whether an access indeed hit. Faced with this dilemma, engineers determined that there will not be one cache to rule them all and introduced multilevel cache hierarchies. The first level (L1) cache closest to the CPU is rather small with access latencies in the order of three cycles. They often feature higher associativities to increase hit rates, which is acceptable due to their small size. The next higher level (L2) is bigger with access latencies in the order of tens of cycles. While there could theoretically be many more levels of caching, most cache hierarchies feature no more than three levels.

In von Neumann architectures, data and instructions are stored in one unified memory. Therefore, caches store both data and instructions. However, access patterns for the two are quite different. Instructions have quite good spatial locality as in code sections without jumps the next instruction is just executed (jumps can also relatively easily be prefetched using various lookahead techniques). Code with loops also has excellent temporal locality. Further, code size is bounded as it relates to the complexity of a program [19] These characteristics make code much easier to cache than code. For this reason designers introduced separate instruction and data caches in the lowest level of the cache hierarchy.

With more than one cache between the CPU and the backing memory not every cache line that is present in the L1 cache has to be present in the higher levels as well. This is a so-called *exclusive* cache. *Inclusive* caches, on the other hand, back all lines in the L1 cache with a line in the higher cache levels. While eviction is cheaper with inclusive caches as a line may still have room in a higher level, writing to a cache line in L1 can be faster in exclusive caches as they do not have to be propagated to the higher levels right away. Many caches implement a mixture between these two policies.

#### 2.1.2 Cache Coherence

With the advent of multiprocessors the lower levels of the cache hierarchy were dedicated to a single core and thus replicated for every core and higher levels were shared between cores and connected using an interconnect. Now, every core may have different copies of the same cache line and read different values. To prevent such a scenario all cache controllers and memory controllers in the system cooperate using a *cache coherence protocol*. In short, a coherence protocol maintains two invariants [47]: for any memory location there exists exactly one core that may write to said location or there are a number of cores reading said location at any given time; and after a write to some memory location, the value of that location will remain the same until another write occurs.

The cache controllers maintain a state machine for each cache line to uphold these invariants. Consider the MOESI variant of such a state machine. In the Modified state a core has modified the cache line and must thus be the only core holding a valid copy of the cache line. If a core holds a cache line in the Owned state, other cores may hold the line in shared state, but the owning core may invalidate their copies by writing to the cache line and transitioning to modified state. A cache line in Exclusive state is guaranteed to be the only valid and clean copy of that cache line in the system. The core holding it may read and write to the cache line as it pleases. A cache line in Shared state is a read only copy of some cache line owned by some other core. A cache line in Invalid state may be neither read from or written to.

To move between those states, the cache coherence protocol specifies a set of transactions which are initiated by coherence requests, e.g. a request to get a particular cache line in shared state. In snooping coherence protocols, all cache controllers observe coherence requests initiating transactions in the same order (per cache line) and then collectively take the correct action [47]. For this coherence request are broadcast to all cache controllers which causes a lot of traffic on the coherence interconnect. Directory based coherence protocols, however, keep track of the state of all cache lines in a global directory. This way, a coherence request needs to be sent only to the directory which decides on the coherence transaction [47]. This reduces the traffic on the bus dramatically, especially for large numbers of cores and thus cache controllers.

The concept of a coherence protocol can be extended to multi-node non-uniform memory access (NUMA) systems. However, this introduces a much more expensive inter-node interconnect into the system. In a *symmetric* distributed directory coherence protocol all nodes are equal partners and maintain a directory for the cache lines located in the memory of their own node, i.e. cache lines *homed* on the particular node. This is a common situation for multi-socket CPU systems [51]. For coherent heterogeneous systems however, not all non-CPU compute can maintain a directory for cache lines homed on its node. Thus, the CPU maintains a global directory across all nodes, making this an *asymmetric* directory coherence protocol. In such a system, the cache controllers of the node without a directory must send all coherence request across the coherence interconnect to the CPU on the other node.

#### 2.2 Enzian

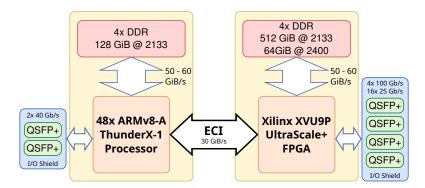

Enzian is an open CPU/FPGA platform for systems software research developed by the Systems group at ETH Zürich [10]. It consists of the powerful ARM CPU ThunderX-1 [43] on node 0 and a Xilinx XCVU9P UltraScale+ FPGA [65] on node 1 (see figure 2.1).

Figure 2.1: Enzian block diagram

The CPU and FPGA are both connected to their own set of DRAM. The main memory on both nodes is coherently connected by a high bandwidth interconnect running the Enzian Coherent Interconnect (ECI) protocol [52] which is based on the ThunderX Cavium Coherent Processor Interconnect (CCPI) protocol. This lets the FPGA participate in the cache coherence protocol of the CPU, which is one of the defining features of Enzian. Further, both nodes have ample network bandwidth — especially the FPGA.

#### 2.2.1 ThunderX

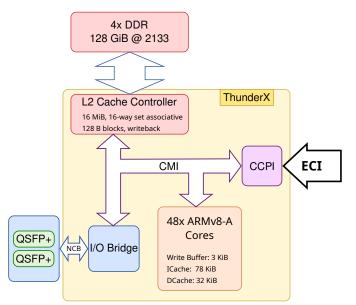

The Cavium ThunderX-1 (see figure 2.2) is a 48-core server grade CPU which implements the ARMv8-A architecture and is clocked at 2.0 GHz [43]. It is itself a system on a chip (SoC) with a number of coprocessors for applications ranging from compression to finite automata. Each core features a 32 KiB, 32-way set-associative write-through L1 data (L1d) cache and a 78 KiB L1 instruction (L1i) cache. The ThunderX has a shared on chip L2 cache, which is also the LLC. The L1d cache and the L2 cache are both physically indexed and physically tagged while the L1i cache is virtually indexed and physically tagged. The cores, the L2 cache, the I/O-bridges (IOBs), and the CCPI are all connected coherently through the Coherent Memory Interconnect (CMI). It ensures coherent memory for all connected components by implementing a set of CMI transactions (see [43]) that uphold the coherence protocol. Some of these transactions are only initiated by prefetch instructions or the ThunderX specific Cavium cache management instructions (CvmCache) [43].

Each ThunderX core features 24 write buffers which perform aggressive write-combining to accumulate writes such that in the best case they can always write a full cache line into the L2 cache. The write buffers may stall the instruction pipeline if the no write buffer entries are available or when barrier instructions execute. The write buffers are flushed, among other events, when a barrier instruction that "must order prior stores to subsequent instructions executes" [43], the write buffer entry times out, or a load instruction to the same cache line as is being accumulated in that write buffer misses in the L1d cache. Making sure that the write buffers are flushed to make writes visible to the rest of the CPU is critical for the correctness of some code.

Figure 2.2: ThunderX block diagram

The ThunderX implements ARMv8 49-bit virtual addresses which are translated into 48-bit physical addresses using a two stage translation process over intermediate physical addresses. The physical address space is partitioned into dynamic random access memory (DRAM) and I/O address spaces. Only the DRAM address space is cached if caches are enabled. Bit 47 in the physical address distinguishes between the two: if address bit 47 is 1, then the address is in I/O space and in DRAM space otherwise. The DRAM and I/O spaces are further partitioned in to subspaces for each CCPI node (see [43] figure 4-1). Each CCPI node has a DRAM address space of 1 TiB.

Each ThunderX core features a hierarchy of three translation lookaside buffers (TLBs) to cache address translations. The 32-entry, fully-associative  $\mu$ TLB caches collapsed address mappings of both stages and is the TLB equivalent of an L1 cache. The MTLB is a larger, fully-associative, 256-entry TLB caching both stage 1 and stage 2 translations. It is the equivalent of an L2 cache. The last TLB in the hierarchy is the 128-entry, fully-associative page walker cache which caches translations for all page table levels except the last. Thus, it is a way to shorten page table walks for the page table walker. All TLBs on the ThunderX can be read out entry for entry using a corresponding CvmCache instruction. Further, the PREFu CvmCache instruction allows prefetching mappings into the  $\mu$ TLB.

Two ThunderX CPUs can be connected to a symmetric directory based cache coherent NUMA system thanks to the CCPI. It implements a reliable link layer protocol and three logical layer protocols. The CCPI logical coherent-memory protocol is a write-back, write-invalidate, home-based sparse-directory protocol that implements a MOESI

coherence protocol [52] for DRAM space. This protocol allows for out-of-order message transmission over the interconnect to minimize transmission latency and maximize usage of the interconnect. The other two logical protocols are used for I/O communication.

#### L2 Cache

The ThunderX L2 cache is 16 MiB large with 128 byte cache lines. It is 16-way setassociative write-back cache with 8192 sets. It can contain both cache lines from the home node and blocks from the remote node.

The replacement policy is implemented with a USED bit per cache way in each set. Generally, cache lines with an unset USED bit are considered for replacement. The USED bit is set to 1 when the L2 cache controller references a cache line. The L2 controller clears all USED bits but the bit in the last referenced block in all available ways in a set if all those USED bits where 1. If during a replacement operation all USED bits in all available ways of a set are 1, the first available cache line will be replaced [43].

L2 cache ways can be partitioned such that certain devices do not pollute the L2 cache. Way partitioning only affects cache replacement as it removes cache ways from consideration when performing replacement originating from specified cores or IOBs.

On the ThunderX individual L2 cache lines can be locked and are thus not replaced until they are unlocked. Cache lines can be locked using the CvmCache instruction fetch and lock which does what it says on the tin if there is an available way. Otherwise, it is a no operation (NOP). Cache lines can be unlocked with any explicit invalidation of the cache line, be it through an invalidation due to the coherence protocol or explicit invalidation using a CvmCache instruction.

CvmCache instructions implement address and index based variants to invalidate L2 cache lines. These instructions come in the Invalidate, Writeback, and Writeback and Invalidate flavors. Address based instructions identify cache blocks by physical address and index based instructions identify blocks by index and way. The latter are useful when flushing large portions of the L2 cache [43]. However, it is important to ensure that the cache index is calculated using the correct algorithm, i.e. mostly aliased.

The ARM architecture also features cache maintenance instructions (dc instructions) [39]. However, on the ThunderX all cache maintenance instructions except dc zva have no effect except that the core write buffer is flushed.

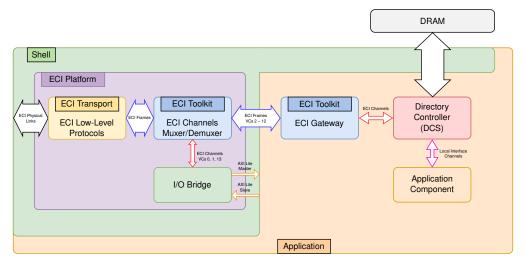

Figure 2.3: Block diagram of the Enzian Shell with a directory controller

#### 2.2.2 FPGA and Shell

The Xilinx XVU9P UltraScale+ FPGA installed on node 1 in Enzian must be configured properly with an initial bitstream before it is able to communicate with the CPU on node 0. To that end Enzian uses an FPGA shell as shown in figure 2.3 akin to Coyote [34]. The Enzian shell<sup>1</sup> provides the basic ECI functionality such as link handling and ECI I/O message handling. Thus, the boot process of CPU must be paused using the Board Development Kit<sup>2</sup> until FPGA is configured properly. This is because the CPU attempts to bring up the ECI links during in the first steps of the boot process which will fail if the FPGA is not able to supply proper protocol replies [10].

Building an FPGA application for Enzian using the shell is a somewhat involved process. First, we need to build the shell with a stub application. The shell is configured such that it is placed in the static part of the FPGA the stub application is placed in the dynamically reconfigurable part. Then we can synthesize the application we actually want to build and link the synthesized shell with the synthesized application. This linked synthesized checkpoint can then be routed, placed and written to a bitstream, which can be programmed onto the FPGA.

<sup>&</sup>lt;sup>1</sup>While there is no default shell at the time of writing, the static-shell seems to have established itself as the de-facto default.

<sup>&</sup>lt;sup>2</sup>It is highly recommended to first get the CPU out of reset and then stopping the boot process using the BDK. The CPU sometimes exhibits problems when it is brought out of reset as there seems to be some reset timing issue between it and the FPGA. This exhibits as an exception during the boot process. To have a higher chance of not encountering an exception on the second boot attempt, the CPU should not be powered off, but rather be reset from the BMC console and its boot process again stopped using the BDK. After reprogramming the FPGA then, most of these boot exceptions go away (given the bitstream is fine).

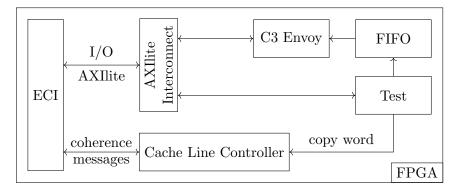

The stub application<sup>3</sup> is interesting in its own right. It is pretty much the simplest application with which the CPU can communicate over ECI. As the "main feature", the stub provides two coherent cache lines in the DRAM address space. Whenever the CPU writes to the first cache line, the written value is copied to the second cache line and can subsequently be read there. This is the *cache line copy* often referred to later in this work. Both of these cache lines are controlled using a relatively simple single cache line controller. It implements the ECI transactions for reading and writing and exposes an interface to FPGA applications to perform coherent reads and writes to this cache line. For a full implementation of a directory, however, one needs to add the DC to an application.

#### 2.2.3 Enzian Coherent Interface

#### 2.3 Enzian Coherent Interconnect

The Enzian Coherent Interconnect (ECI) is an implementation of a cache coherence protocol in two-socket hybrid FPGA-CPU architectures. It is designed such that it implements the native ThunderX CCPI protocol and for implementation on an FPGA [52].

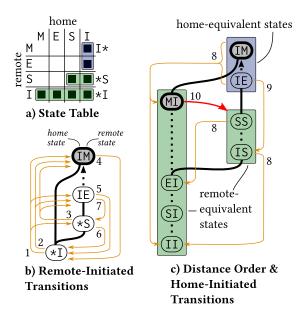

ECI, unlike CCPI, does not implement a full MOESI protocol. Instead, it implements an enhanced MESI protocol because it includes a transition (labeled 10 in figure 2.4 c) where the FPGA holds a dirty cache line in modified state and the CPU requests an upgrade of its copy of the cache line (currently in the invalid state) to shared, which is not included in plain MESI. But the inclusion of this transition in the protocol improves performance considerably as it avoids unnecessary writes to main memory and instead forwards the cache line [52].

ECI is an entirely pull based protocol. Meaning that a home node may not transfer data to a remote node without the latter first requesting said data. Therefore, the FPGA is not able to write data into the CPU's cache on its own initiative. Looking at all possible state transitions in ECI, there is no transition from a state where only one node has valid data to another state where either both nodes will have the same data or only the other node will have the same data. Moving data to another node is only possible via state transitions through the invalid state (see figure 2.4 c).

With coherence messages exposed to FPGA applications, these are able to participate in the coherence protocol and act like cache controllers making and serving coherence requests. This allows for some customization withing the bounds of the native cache coherence protocol and for manipulation of cache lines usually not possible with normal cache controllers.

<sup>&</sup>lt;sup>3</sup>Link to repository: https://gitlab.inf.ethz.ch/project-openenzian/fpga-stack/dynamic-stub

Figure 2.4: ECI protocol states and transitions as drawn by Ramdas et al. [52]

#### 2.3.1 Directory Controller

The Enzian directory controller (DC) uses the coherence messages exposed by ECI to implement a symmetric directory coherence platform on Enzian [51]. The DC exposes 38 bits of coherent but uncached (on the FPGA) DRAM address space. It uses two parallel directory controller slices (DCSs), an odd directory controller slice (DCS) for handling ECI messages from odd numbered virtual channels (VCs) and managing even indexed cache lines and vice-versa. A DCS exposes an Advanced eXtensible Interface (AXI) interface to perform the reads and writes from and to some memory. The AXI interface is addressed using cache line indices shifted to the right by one bit, because this bit is the same for all indices of a slice. Further, a DCS exposes local VCs for local coherence requests.

Among the local coherence requests are the local clean invalidate (LCI) and unlock (UL) requests. The LCI request starts a coherence transaction which causes a writeback and subsequent invalidation of a specified cache line. Further, this locks the cache line such that the CPU cannot access it until it is unlocked. Once the LCI local coherence transaction is complete the DCS send a local clean invalidate acknowledgement (LCIA) message to acknowledge the completion. The UL coherence request simply unlocks the specified cache line. It does not have an acknowledgement and is assumed to complete immediately.

To use the DC in an application, we can include it as a submodule and add its sources in the project creation TCL script. We can then use the provided interfaces for coherent memory accesses after connecting the ECI VCs.

## 3 System Design

In this chapter we design the C3 system based on a select set of requirements. We design incrementally, taking fundamental design decisions which inform the further design. Based on a high-level design we investigate a few key mechanisms to inform the detailed design or the implementation or use of the system.

#### 3.1 Design Requirements

The overarching goal of C3 is to provide additional features for ECI as a base for experimentation with future cache coherence protocols. To enable experimentation, we want C3 to be *modular* for easy use and *extensible* as we might not have foreseen all the needs of future research. Further, C3 should have as small of an impact on the rest of the system as possible.

However, we assume that applications on the CPU and their offloaded counterpart on the FPGA are co-designed and somehow have shared knowledge of some values. Further, we assume that the user controls the entire system. Therefore, C3 will not handle conflicting address spaces or identifiers between components.

Initially, C3 should implement the *injection of cache lines* from the FPGA to the CPU L2 cache, *interrupts of CPU cores from the FPGA* and *cache allocation*. In order to provide a good basis for research, cache injection should ideally be faster than DMA. Therefore, we require that C3 exhibits low latency so cache injection over C3 might have a benefit over plain old DMA.

#### 3.2 C3 Design

The main challenge for C3 is that the operations the FPGA should be able to perform require actions on the CPU. Cache injection from the FPGA is not possible due to ECI only allowing nodes to pull data which therefor requires the CPU to request data when the FPGA pushes data. Interrupting CPU cores from the FPGA is currently mainly not possible on Enzian due to the interrupt lines in the serial link between the two sockets not being reverse engineered yet, which is out of scope for this thesis<sup>1</sup>. Therefore, we need a communication channel between the FPGA and the CPU where the FPGA instructs the CPU to execute something. Further, this implies that we need a component on the FPGA to gather instructions and send them to the CPU and a component on the CPU to execute instructions.

In general, workloads on the FPGA are using it as an accelerator for some application managed from the CPU. The CPU might dispatch work to the FPGA and subsequently receive results or the FPGA might be doing some offloading on the I/O-path (e.g. a smart NIC) and the CPU will receive data without asking for it. With its initial feature set, C3 is only involved when the CPU is receiving data.

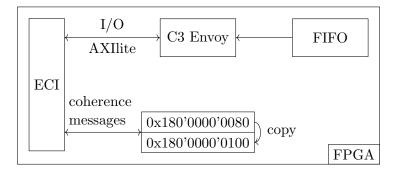

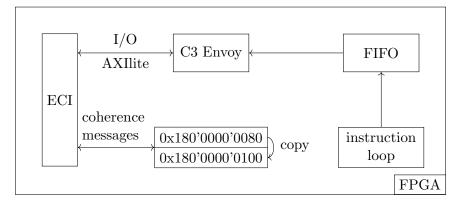

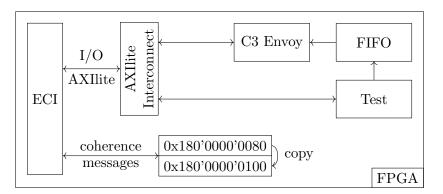

In order to get a prictoral overview over the design discussed in the following section, refer to figure ??.

#### 3.2.1 Control Path

Since we want to provide features additional to ECI the interface should not be too different. The interface to ECI is a ready/valid interface to submit packets on virtual channels. ECI needs to transfer packets that oftentimes contain data as it manages the transfer of data between nodes. The C3 does not directly transfer data, but only 64-bit instructions from the FPGA to the CPU, which may initiate a data transfer on the CPU. Thus, the interface for an application on the FPGA is a ready/valid interface to submit an instruction.

**Design Decision 1.** Applications on the FPGA use 64-bit instructions to delegate tasks to the CPU.

To transfer the instructions from the FPGA to the CPU we expose a register location in the I/O address space of the FPGA which the CPU can read to get an instruction. This leads to the question when the CPU should read from that instruction register. One option is for the FPGA to interrupt the CPU when a new instruction is ready. This is impractical as the only interrupts we can issue from the FPGA before this work are general purpose input/output (GPIO) interrupts and if two instructions arrive shortly after one another, the processing of the first instruction might be interrupted by the first. Another option is for the CPU to continuously poll for new instructions and execute them immediately upon receiving them, which naturally serializes the execution of C3 instructions on the CPU. Further, polled I/O is a known tool for reducing latency on data transfers [3] as data can be used immediately when it becomes available.

<sup>&</sup>lt;sup>1</sup>Integrating the FPGA with the ThunderX's generic interrupt controller (GIC) is investigated by Nicolas Tischler at the time of writing.

However, polling continuously can severely detract from the performance of the entire systems as it consumes lots of CPU time spinning and it can also stress the memory bus with lots of read transactions. Since the ThunderX CPU on Enzian has 48 cores, we dedicate one of those cores to be the dedicated *Cache Control Coprocessor* to limit the adverse effects of polling to that core. Dedicating cores to polling I/O is also a well-known technique used by for instance by Andromeda [17], Shenango [48], and the DPDK [50]. To reduce the memory bus traffic from polling, the FPGA can stall the read while no instruction is available for at most the ECI timeout. Another advantage of isolating a core for the C3 is that it will be the only load on the core and thus have the L1 caches to itself. This should allow for less delay between subsequent fetches and thus lower latencies when multiple instructions are ready on the FPGA.

**Design Decision 2.** The Cache Control Coprocessor is implemented on an isolated CPU core to enable continuous polling for C3 instructions with reduced impact on the rest of the system and to enable a very tight fetch loop.

Because the C3 reads instructions from the FPGA at its own pace, we need some buffering between the application and the instruction read register. The C3 envoy provides the ready valid interface for applications to submit C3 instructions and the register for the C3 to read the submitted instructions. It provides buffering for instructions by implementing a first-in, first-out (FIFO) instruction queue, where the head of the queue is removed and returned when the C3 fetches an instruction. Further, it stalls the C3's read if the instruction queue is empty, as described above. If an instruction arrives during the stall, it returns that instruction immediately. However, if no instruction arrives before a set timeout, it returns a value signifying that no instructions in a very tight fetch loop which would generate loads read transactions and bus traffic. The aim of the read stalling is to reduce this traffic when it is not needed.

**Design Decision 3.** C3 instructions submitted by FPGA application are buffered by the C3 envoy which exposes a register location for the C3 to fetch the instructions from the queue. The C3 envoy stalls reads from the C3 when the instruction queue is empty to reduce bus traffic.

Note that the control path as described thus far decouples the submission of an instruction by a FPGA application from the instruction's execution on the C3. In other words, the application on the FPGA does not know at which point in time a C3 instruction it has issued is done executing. This makes it impossible for the application on the FPGA to notify its counterpart on the CPU that data is ready with "traditional" methods like ring buffers as this will race with the execution of a data transfer instruction. ECI is similar that the application cannot be sure when the transaction completes, but it knows when it issued the transaction. However, there is still a chance that packets might be reordered on the bus. With C3, there are two straight forward ways to get around this. The first possibility is for the C3 envoy to signal the application when a particular instruction has completed, i.e. the CPU requested the next instruction after executing said instruction. This can be achieved by having the FPGA application execute in lock-step with the CPU or the submitted instructions get IDs which will be acknowledged by the C3 envoy after the C3 has executed them, which leads to some bookkeeping in the FPGA application to keep track of already executed instructions. The application can then ensure that "traditional" notification methods will be consistent. The second possibility is to make the notifications that data is ready for the CPU application to consume a C3 instruction themselves. Because instructions are submitted to a FIFO queue the C3 will execute them in order and one after another, so the data transfer and the accompanying notification are serialized and will not race anymore. For this work, we choose the second option due to its relative simplicity of piggybacking on the serialized execution.

Since we are executing notification instructions on the C3, we need to perform some cross core action to notify the application running on some different core. There are several ways to accomplish this: we could issue an SGI to the core running the application, we could implement some operating system primitives like read() or poll() which return when a new notification arrived, or we could implement some UMP-like transfer from the C3 to the application core.

**Design Decision 4.** The only explicit synchronization in the C3 system is the serialized execution of C3 instructions and notification instructions for FPGA applications to notify CPU applications. Since most applications need more synchronization, the design for C3-aware applications must include a synchronization contract between the CPU and FPGA applications.

Up to this point, we have only talked about a single application on the CPU and a single application on the FPGA working cooperatively. The design above can easily be adapted to multiple applications on both nodes. The C3 envoy only needs a multiplexer (MUX) on its ready/valid interface to accommodate multiple applications on the FPGA. The C3 itself needs a bit more work due to notification instructions. It needs to be able to map notifications to an app on the CPU. We enable this by having applications register with the C3 using an application id. The offloaded part of the application on the FPGA then needs to use this application id in its notification instructions. This setup theoretically allows for mapping many FPGA applications to one CPU application, but we disallow mapping one application id to multiple CPU applications. Sharing transferred data must be organized on the application level.

**Design Decision 5.** To enable multiple applications to use the C3, all CPU applications must register with the C3 using an application ID.

The C3 the CPU applications reside in different virtual address spaces and the FPGA does not have any address translation. However, the application on the FPGA must specify where the C3 needs to fetch data or which data is ready when notifying an CPU application. While it would be possible in principle to specify virtual addresses, it is much simpler and less error-prone to only deal in physical addresses. Since C3 instructions will mostly fetch from FPGA-homed memory, dealing in physical addresses is easier programs on the CPU will map the FPGA address space using mmap(2) and then compute addresses based on offsets from the base address. Further, it is also possible to identity map chunks of FPGA address space or even the entire address space, if needed.

To express more complex prefetching patterns, e.g. prefetch data needed for processing transferred data, the FPGA application needs to specify a CPU-homed address. In this case, the FPGA application needs to be informed of the locations of interest somehow (e.g. co-design with fixed locations, registers) and therefore it does not matter what kind of addresses it specifies as long as the CPU application knows how to interpret them correctly.

**Design Decision 6.** In general, addresses specified in C3 instructions are physical addresses. Deviations from this rule must be designed explicitly and require coordination between the CPU and FPGA application.

#### 3.2.2 Data Path

One goal of the C3 is to offer data transfer from the FPGA to the CPU via direct cache injection. The only way to move data into the ThunderX's L2 cache is to have the ThunderX request it through a prefetch or a normal load as ECI only allows data to be pulled by a node. For the C3 to be able to fetch a cache line, the application on the FPGA needs to make it available over the interconnect. Uniquely on Enzian, this can be achieved by listening to cache coherence requests over ECI and respond to read requests on the cache line the application wanted to fetch directly with a response packet containing the data. The other way is to coherently write the data to be transferred to FPGA memory in the DRAM address space using the DCS. Interacting with ECI directly has the advantage that the application can issue a fetch C3 instruction as soon as the data is ready without having to write to memory beforehand. On the other hand it is much harder to implement correctly as we would have to deal with arbitrary coherence requests instead of interacting with the DCS to coherently write to memory. Further, we can reduce the latency of writing to memory by not writing to DRAM but using a smaller and much faster block random access memory (BRAM) dedicated solely to transferring data. Using crossbars, we can still use the rest of the address space for DRAM.

**Design Decision 7.** C3-aware applications use coherent writes to FPGA-homed memory to provide data that should be fetched by the C3.

In order to increase throughput and reduce the amount of instructions an application has to issue to transfer multiple cache lines, we want to be able to fetch multiple consecutive cache lines with one simple instruction. The largest transfer we want to allow, however, is 1 MiB, which corresponds to one way of the ThunderX's L2 cache. This is to limit the impact of C3 on the other users of the shared cache. With 1 MiB of data to transfer our approach of interacting directly with ECI will also need a sizable buffer, so we might as well write coherently to some scratch memory and be relieved of tracking cache line states. Thus and due to its relative simplicity, we choose the latter approach of coherently writing data to memory using the DCS before a data transfer.

**Design Decision 8.** To reduce the number of instructions needed and increase througput C3 instructions operating on cache lines should be ranged such that the same operation on multiple consecutive cache lines can be executed using a single instruction. The range in C3 instructions is limited to 1 MiB.

Once the C3 receives an instruction to fetch cache lines it can load the data from the scratch memory in the FPGA's address space as indicated in the instruction. We will investigate what the best method is for transferring a cache line into the ThunderX L2 cache in section 3.3.1.

An application can use data once it gets a notification from the C3 that some range of cache lines is now ready to be consumed. At this point the application can normally access memory at the specified location.

#### 3.3 Key Mechanisms

In this section, we investigate some key mechanisms in detail to inform the detailed design of C3.

#### 3.3.1 Direct Cache Injection

The C3 needs some way to transfer cache lines from the FPGA into its L2 cache. Performing a load on a word in a FPGA-homed cache line from the CPU will always fetch the line into the CPUs L2 cache. But this will also pollute the L1d cache of the core performing the load. Since we want the fetch loop of the C3 to be as quick as possible, we want to avoid polluting its L1 caches and thus avoid conflict misses.

To avoid polluting the L1 caches, we can use some form of prefetching into the L2 cache. The ARMv8 instruction set architecture (ISA) offers the prfm p{ld,st}l2{keep,strm} instructions. Further, the ThunderX offers a CvmCache system instruction L2 Fetch & Lock.

#### Prefetching on the ThunderX

In the ARMv8 microarchitecture prefetch instructions are considered performance hints and may be ignored by the processor [39]. On the ThunderX, testing by Jasmin Schult during her master thesis [54] suggests that prefetching will only occur if the prefetch would not incur a page fault. However, it is not clear exactly if this "page fault" is a TLB miss or some other fault in the address translation system.

To find out when exactly a ThunderX will indeed issue a prefetch, we have to get a closer look at the contents of its TLB just before a prefetch is issued. Luckily, the ThunderX provides system instructions for reading the contents of its TLBs [43] which we can utilize using the infrastructure described in section 4.1. We use the Enzian memory explorer described in section 4.1.4 to script different experiments to determine the prefetching behavior of the ThunderX.

To investigate prefetching on the CPU, we need to control a cache line in the L2 cache and write it back to DRAM so we can actually prefetch it. This does not sound too hard as we could simply write to some cache line and write it back. But doing so would only modify the cache line in the L1d cache of the core that wrote it and not immediately write through to L2 cache. The ThunderX implements an aggressive write-buffer that combines writes until a full cache line can be written to the L2 cache [43]. Before the write-buffer is flushed other cores can already access the modified cache line as the point of coherence on the ThunderX is in the L1d cache of every core. For our purpose of testing however, we want to ensure that all prefetches come from main memory and not from a write-buffer. On the ThunderX the write-buffer is flushed before a full cache line has been gathered when dmb or dsb barriers enforce ordering of stores, a load or prefetch instruction to the same cache line misses in the L1d cache, but hits in the write-buffer (i.e. another core accesses the modified subcacheline), and on architectural events such as a write-buffer entry timeout, more than a threshold of write-buffer entries are filled or a GlobalSync from outside the core arrives. In experiment 3.1 we see that the write-buffer entry timeout is at  $2^{13}$  cycles. Thus, every write will be written to the L2 cache after at most  $2^{13} \cdot 2 \text{ GHz} = 2^{-14} \text{ s} \approx 61 \mu \text{s}$ . The ThunderX also implements all data cache maintenance instructions except dc  $zva^2$  only as a write-buffer flush, since they are performance hints. Thus, the easiest way to ensure that a write ends up in the L2 cache for testing is to put a barrier after modifying cache lines.

<sup>&</sup>lt;sup>2</sup>Zero out a cache line

#### Following along: Experiment 3.1: Memory Configuration

Required bitstream: None Script: experiments/mem-conf.sh What you will see: The script shows the contents of the system register CVMMEMCTL0\_EL1. Towards the bottom you can find the values regarding the writebuffer.

Writing back a cache line in the L2 cache to main memory is easy on the ThunderX as it implements special instructions for very specific cache management (see section 2.2.1). In this case we need CvmCache L2 Hit Writeback Invalidate, which writes back and invalidates a cache line based on a physical address if that address hits in the L2 cache.

Armed with the knowledge how we can control a cache line, we show that the ThunderX does execute a prefetching instruction when the mapping of virtual address of the cache line we want to prefetch is cached in the TLB and no page table walk is necessary.

As seen in section 2.2.1, the ThunderX has a translation hierarchy of multiple TLBs: the 32-entry  $\mu$ TLB and the 256-entry MTLB both caching virtual address mappings, and the 128-entry walker cache, which caches address translations for each level of the page table except the last. Hence, if a virtual address hits in the  $\mu$ TLB or the MTLB, no page table walk is required whereas if the address hits in the walker cache, the page table walker must still perform the page table lookup for the last level of translation.

On the ThunderX we can also inspect the contents of the three TLBs. Using the respective CvmCache instructions, we can read a single entry from one of the three TLBs into the memory mapped registers. By reading each entry of a TLB and comparing with a given virtual address, we can thus determine if this virtual address hits in the given TLB. For the implementation details refer to section 4.1.3. However, this introspection overhead of iterating over all entries actually makes it difficult to observe if a virtual address hits in the  $\mu$ TLB. Due to its small size and the large overhead, a virtual address often gets evicted from the  $\mu$ TLBby merely trying to observe it. Experiment 4.1 demonstrates this phenomenon.

With experiment 3.2 we see that the ThunderX only prefetches when the access does not need a page table walk. To show this we use a writing core  $c_1$  and a reading core  $c_2$ .  $c_1$  prepares two adjacent cache lines  $l_1$ ,  $l_2$  on the same page p and one cache line  $l_3$  on the next page q such that they are flushed from the write-buffer and subsequently writes back and invalidates all of them. By accessing  $l_1$ ,  $c_2$  ensures that the mapping for p is valid in at least the MTLB which in turn ensures that prefetching  $l_2$  succeeds. Since the reading core has not accessed a virtual address on page q, its mapping is not present in any of the core's TLBs. When  $c_2$  prefetches  $l_3$ , the ThunderX will not execute it because a page table walk is necessary.

#### Following along: Experiment 3.2: Prefetching CPU-homed addresses

Required bitstream: None

Script: experiment/prefetch-homed.sh

What you will see: Two tmux panes will open. Each with processes pinned to a different core. The core in the left pane writes to cache lines and the core in the right pane accesses cache lines. All addresses are physical addresses in the CPU DRAM address space.

First, prefetching a cache line on a page with its mapping in the MTLB or uTLB will succeed. Then, prefetching a cache line on a page without a cached mapping will fail.

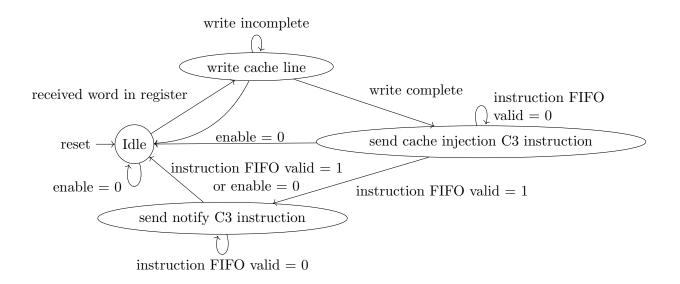

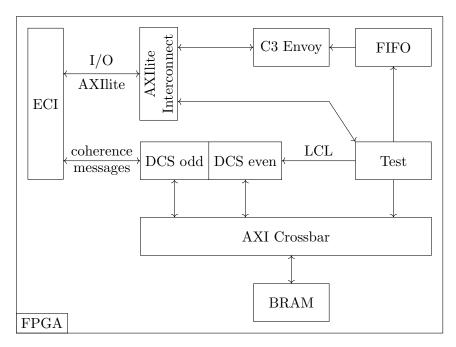

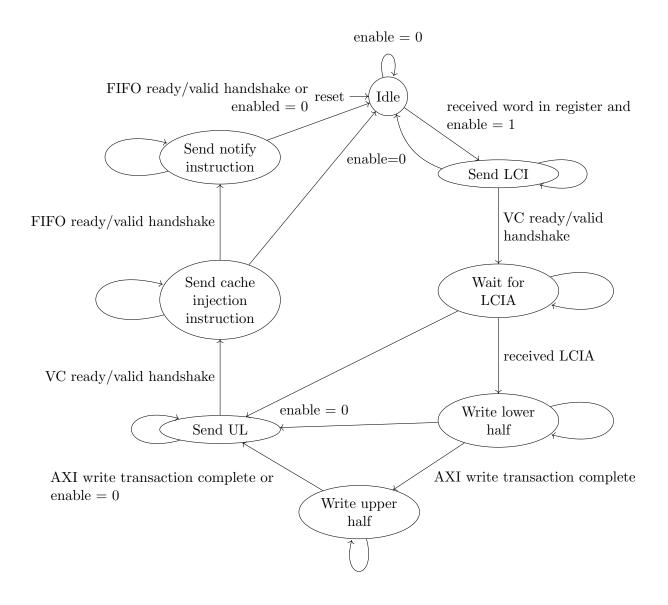

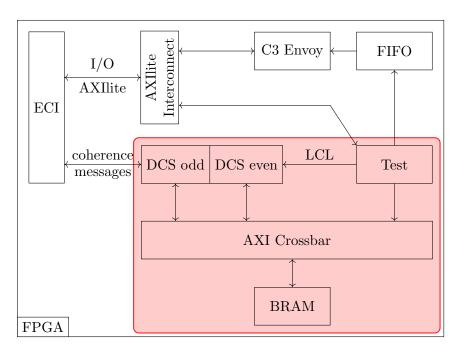

While we cannot inspect the contents of the walker cache because we do not know how to interpret its contents, experiment 3.2 was set up such that the walker cache should contain the translation for the second to last level for  $l_3$ . We set up  $l_3$  on page q that shares its second to last level translation table entry with page p, which contains  $l_2$ . Because we accessed  $l_2$  right before we try to prefetch  $l_3$  and the mapping for  $l_2$  was cached in the MTLB, the shared second to last level translation table is most likely cached in the walker cache at the time of accessing  $l_3$ . This suggests that the ThunderX will not execute a prefetch if this access would cause a page walk for a single level.