Understanding the Capabilities of Privileged Attackers Against Trusted Execution Environments

Ivan Puddu

#### DISS. ETH NO. 29091

# UNDERSTANDING THE CAPABILITIES OF PRIVILEGED ATTACKERS AGAINST TRUSTED EXECUTION ENVIRONMENTS

A thesis submitted to attain the degree of DOCTOR OF SCIENCES

(Dr. sc. ETH Zurich)

presented by IVAN PUDDU

MSc ETH CS, ETH Zurich

born on 18.08.1992

accepted on the recommendation of

Prof. Dr. Srdjan Čapkun, examiner Dr.-Ing. Anil Kurmus, co-examiner Dr. Jonathan M. McCune, co-examiner Prof. Dr. Shweta Shinde, co-examiner

Copyright © Ivan Puddu 2023 https://ivanpuddu.com

All rights reserved. Non-commercial use permitted. http://rightsstatements.org/vocab/InC-NC/1.0/

DOI 10.3929/ethz-b-000610177

#### **Contents**

| Ab | stract | (English/Italiano/Français/Deutsch)    | vii  |

|----|--------|----------------------------------------|------|

|    | Abstra | act                                    | vii  |

|    | Somm   | nario                                  | ix   |

|    | Résun  | né                                     | хi   |

|    |        |                                        |      |

|    | Zusan  | nmenfassung                            | xiii |

| Ac | knowle | edgements                              | xvii |

| T  | Intro  | duction and Background                 | 1    |

| _  |        | •                                      |      |

| 1  |        | luction                                | 3    |

|    |        | hesis Contributions                    | 6    |

|    |        | hesis Organization                     | 9    |

|    | 1.3 P  | Publications and Author Contributions  | 10   |

| 2  | Backg  | round                                  | 13   |

|    | 2.1    | Computer Architecture Fundamentals     | 13   |

|    | 2.2 B  | Basic Isolation Enforcement            | 18   |

|    | 2.3 T  | rusted Execution Environments          | 27   |

|    | 2.4 In | ntel SGX                               | 29   |

|    | 2.5 A  | MD SEV-SNP                             | 36   |

| II | Info   | rmation Leakage in TEEs                | 39   |

| 3  | Fronta | al Attack                              | 41   |

|    | 3.1 In | ntroduction                            | 41   |

|    |        | Background                             | 44   |

|    |        | Overview of the Frontal Attack         | 46   |

|    | 3.4 F  | rontal Attack Profiling                | 49   |

|    |        | rontal Attack Exploitation             | 59   |

|    |        | affected Processors and Configurations | 64   |

iv Contents

|          | 3.7                                                                               | Potential Causes                                                                                                                                                                                                                                                                             |                                                                                                |

|----------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|          | 3.8                                                                               | Defenses                                                                                                                                                                                                                                                                                     |                                                                                                |

|          | 3.9                                                                               | Related Work                                                                                                                                                                                                                                                                                 |                                                                                                |

|          | 3.10                                                                              | Conclusions                                                                                                                                                                                                                                                                                  | 72                                                                                             |

| 4        | Cod                                                                               | e Confidentiality in TEEs                                                                                                                                                                                                                                                                    | 75                                                                                             |

|          | 4.1                                                                               | Introduction                                                                                                                                                                                                                                                                                 |                                                                                                |

|          | 4.2                                                                               | System and Attacker Model                                                                                                                                                                                                                                                                    | 77                                                                                             |

|          | 4.3                                                                               | Leakage Analysis Overview                                                                                                                                                                                                                                                                    |                                                                                                |

|          | 4.4                                                                               | Methodology                                                                                                                                                                                                                                                                                  |                                                                                                |

|          | 4.5                                                                               | Leakage Analysis                                                                                                                                                                                                                                                                             |                                                                                                |

|          | 4.6                                                                               | IR Instruction Leakage in Practice                                                                                                                                                                                                                                                           |                                                                                                |

|          | 4.7                                                                               | Evaluation                                                                                                                                                                                                                                                                                   |                                                                                                |

|          | 4.8                                                                               | Related Work                                                                                                                                                                                                                                                                                 |                                                                                                |

|          | 4.9                                                                               | Discussion                                                                                                                                                                                                                                                                                   |                                                                                                |

|          | 4.10                                                                              | Conclusions                                                                                                                                                                                                                                                                                  | 106                                                                                            |

| 5        | Prev                                                                              | renting Single-Stepping                                                                                                                                                                                                                                                                      | 109                                                                                            |

|          | 5.1                                                                               | AEX-Notify                                                                                                                                                                                                                                                                                   | 110                                                                                            |

|          |                                                                                   |                                                                                                                                                                                                                                                                                              |                                                                                                |

|          |                                                                                   |                                                                                                                                                                                                                                                                                              |                                                                                                |

| II       | [ <b>A</b> :                                                                      | nalysis of Attestation Shortcomings                                                                                                                                                                                                                                                          | 113                                                                                            |

| III<br>6 |                                                                                   | ,                                                                                                                                                                                                                                                                                            | 113<br>115                                                                                     |

|          |                                                                                   | nalysis of Attestation Shortcomings  y-safe Attestation  Introduction                                                                                                                                                                                                                        | 115                                                                                            |

|          | Rela                                                                              | y-safe Attestation                                                                                                                                                                                                                                                                           | <b>115</b> 115                                                                                 |

|          | Rela                                                                              | y-safe Attestation Introduction                                                                                                                                                                                                                                                              | 115<br>115<br>119                                                                              |

|          | <b>Rela</b> 6.1 6.2                                                               | y-safe Attestation Introduction                                                                                                                                                                                                                                                              | 115<br>115<br>119<br>121                                                                       |

|          | Rela<br>6.1<br>6.2<br>6.3                                                         | y-safe Attestation Introduction                                                                                                                                                                                                                                                              | 115<br>115<br>119<br>121<br>127                                                                |

|          | Rela<br>6.1<br>6.2<br>6.3<br>6.4                                                  | y-safe Attestation Introduction SGX Background Relay Attack Analysis PROXIMITEE Experimental Evaluation Addressing Emulation Attacks                                                                                                                                                         | 115<br>115<br>119<br>121<br>127<br>133<br>140                                                  |

|          | Rela<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                                           | y-safe Attestation Introduction SGX Background Relay Attack Analysis PROXIMITEE Experimental Evaluation                                                                                                                                                                                      | 115<br>115<br>119<br>121<br>127<br>133<br>140                                                  |

|          | Rela<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                    | y-safe Attestation Introduction SGX Background Relay Attack Analysis PROXIMITEE Experimental Evaluation Addressing Emulation Attacks                                                                                                                                                         | 115<br>115<br>119<br>121<br>127<br>133<br>140<br>145                                           |

|          | Rela<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                             | y-safe Attestation Introduction SGX Background Relay Attack Analysis PROXIMITEE Experimental Evaluation Addressing Emulation Attacks Discussion and Related Work                                                                                                                             | 115<br>115<br>119<br>121<br>127<br>133<br>140<br>145                                           |

| 6        | Rela<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                             | y-safe Attestation Introduction SGX Background Relay Attack Analysis PROXIMITEE Experimental Evaluation Addressing Emulation Attacks Discussion and Related Work Conclusions                                                                                                                 | 115<br>115<br>119<br>121<br>127<br>133<br>140<br>145<br>146                                    |

| 6        | Rela<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                      | y-safe Attestation Introduction SGX Background Relay Attack Analysis PROXIMITEE Experimental Evaluation Addressing Emulation Attacks Discussion and Related Work Conclusions time Trust in Intel SGX                                                                                         | 115<br>115<br>119<br>121<br>127<br>133<br>140<br>145<br>146                                    |

| 6        | Rela<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Run<br>7.1        | y-safe Attestation Introduction SGX Background Relay Attack Analysis PROXIMITEE Experimental Evaluation Addressing Emulation Attacks Discussion and Related Work Conclusions time Trust in Intel SGX Introduction                                                                            | 115<br>115<br>119<br>121<br>127<br>133<br>140<br>145<br>146<br>147                             |

| 6        | Rela<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Run<br>7.1        | y-safe Attestation Introduction SGX Background Relay Attack Analysis PROXIMITEE Experimental Evaluation Addressing Emulation Attacks Discussion and Related Work Conclusions time Trust in Intel SGX Introduction Attacker Model: Manufacture-Time vs. Post-Deployment                       | 115<br>115<br>119<br>121<br>127<br>133<br>140<br>145<br>146<br>147<br>147                      |

| 6        | Rela 6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8 Run 7.1 7.2                                  | y-safe Attestation Introduction SGX Background Relay Attack Analysis PROXIMITEE Experimental Evaluation Addressing Emulation Attacks Discussion and Related Work Conclusions time Trust in Intel SGX Introduction Attacker Model: Manufacture-Time vs. Post-Deployment Compromise            | 115<br>115<br>119<br>121<br>127<br>133<br>140<br>145<br>146<br>147<br>147                      |

| 6        | Rela<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Run<br>7.1<br>7.2 | y-safe Attestation Introduction SGX Background Relay Attack Analysis PROXIMITEE Experimental Evaluation Addressing Emulation Attacks Discussion and Related Work Conclusions time Trust in Intel SGX Introduction Attacker Model: Manufacture-Time vs. Post-Deployment Compromise Background | 115<br>115<br>119<br>121<br>127<br>133<br>140<br>145<br>146<br>147<br>147<br>148<br>148<br>153 |

<u>Contents</u> <u>v</u>

| 8 Runtime Trust in AMD SEV-SNP 8.1 Introduction                                                                                                                                                                                              | 157                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 9 Closing remarks 9.1 Conclusions                                                                                                                                                                                                            |                                 |

| Appendices                                                                                                                                                                                                                                   | 167                             |

| A Frontal Attack A.1 Responsible Disclosure A.2 Data-Oblivious Execution A.3 Measurement Details A.4 Outside Intel SGX  B Code Leakage B.1 Responsible Disclosure B.2 x86 ISA Instruction Count B.3 Analysis of SotA Attacker Cycle Accuracy | 169<br>170<br>173<br>175<br>175 |

| Bibliography                                                                                                                                                                                                                                 | 177                             |

| List of Figures                                                                                                                                                                                                                              | 189                             |

| List of Tables                                                                                                                                                                                                                               | 195                             |

| List of Listings                                                                                                                                                                                                                             | 197                             |

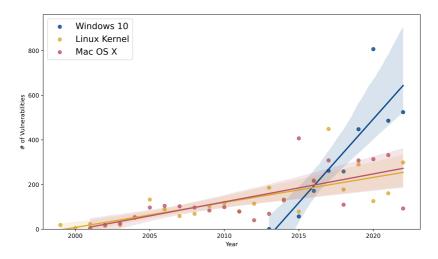

Our lives today rely on the secure operation of computers in a diverse set of sectors, from energy to medicine. However, today's computers execute software bloated with complexity. Their large codebases provide a rich and versatile system, but most functionalities are often not needed in their target applications. This increases the trusted computing base (TCB) – the software and hardware that needs to be trusted for the system to work correctly. A large TCB is undesirable, as it gives attackers a higher likelihood to find and exploit vulnerabilities. Most of this complexity comes from the system software, that is, the operating system (OS) and the hypervisor. Despite this, the system software's codebase cannot generally be removed from the TCB, as it executes with the highest privileges.

Thanks to additional hardware primitives, Trusted Execution Environments (TEEs) break this paradigm, allowing even system software to be removed from the TCB. Most CPU manufacturers and architectures support some form of TEE: they can be found on Intel and AMD CPUs, as well as on ARM and RISC-V architectures. Their advent is promising, as they aim to let applications operate securely both when the (more privileged) system software is malicious and when a physical attacker can tamper with the system. Arguably, however, the guarantees that can be provided against such a strong and privileged attacker are not fully understood and often lead to TEE designs that make compromises invalidating the protections that they aim to provide. For example, previous work shows that the OS can abuse the CPU memory management interface to get notified when the TEE accesses attacker-specified memory regions, breaking data confidentiality. Understanding the capabilities of privileged attackers thus leads to more accurate designs and a more secure computing environment for everyone.

In this thesis, we contribute to the efforts of understanding the capabilities of privileged attackers in the context of TEEs in four main directions. First, we develop the *Frontal* attack, which shows that leveraging the OS to issue interrupts frequently leads to the CPU exposing detailed instruction execution timings, which can be used as a side channel. This side channel is detailed enough to leak encryption keys from a TEE and thus break data confidentiality. Second, we show that current commercial TEEs struggle to provide code confidentiality against a privileged attacker. Notably, we observe that using interpreters or JIT compilers inside TEEs – a popular choice due to their convenience and

viii Abstract

flexibility – leaks significantly more confidential instructions compared to a baseline where native instructions are used instead.

The third and fourth contributions relate to attestation protocols, which are used to verify that a TEE is protecting a given application. We emphasize the impact of previously neglected aspects in attestation protocols in both these contributions. In the third contribution, we highlight that relay attacks, while once thought to be tolerable given the TEE protections, enhance the capabilities of a privileged attacker. Finally, in the fourth contribution, we show that current attestation protocols implicitly assume trust in the TEE manufacturer at runtime – despite the manufacturers often claiming otherwise. While this implicit trust in the TEE manufacturer is often overlooked, our analysis shows that it is a concrete threat in practice and should thus be accounted for in future attestation protocols.

Oggigiorno, diversi aspetti della nostra vita dipendono dal corretto funzionamento dei computer in una vasta gamma di settori, dall'energia alla medicina. Tuttavia, attualmente i computer spesso eseguono software sovradimensionato e altamente complesso. La vastità di questo software fornisce un sistema versatile e ricco di funzionalità, anche se la maggior parte di queste spesso rimangono inutilizzate nelle applicazioni finali. Ciò aumenta la *Trusted Computing Base* (TCB, letteralmente *base fidata per la computazione*), ovvero il software e l'hardware di cui ci si deve fidare affinchè il sistema funzioni correttamente. Un'ampia TCB non è auspicabile, in quanto aumenta le probabilità che gli hacker trovino e sfruttino vulnerabilità per compromettere il sistema. La maggior parte di questa complessità deriva dal software di sistema, ovvero il sistema operativo e l'hypervisor. Nonostante ciò, la codebase del software di sistema non può essere generalmente rimossa dal TCB, poiché viene eseguita con i privilegi più elevati.

Grazie a delle primitive hardware aggiuntive, i Trusted Execution Environments (TEE, letteralmente ambienti di esecuzione affidabili) permettono di abbandonare questo paradigma, in quanto consentono di rimuovere dal TCB anche il software di sistema. La maggior parte dei produttori di CPU e delle architetture hardware supporta una forma di TEE: sono presenti sia sulle CPU di Intel e AMD, che sulle architetture ARM e RISC-V. Il loro avvento è promettente, in quanto mirano a proteggere applicazioni sia da un software di sistema (più privilegiato) malevolo, che da manomissioni fisiche sul sistema. Purtroppo, però, le garanzie che possono essere fornite contro un tipo di attacco così forte e privilegiato non sono ancora del tutto comprese e spesso portano a progettare TEE con compromessi che invalidano le protezioni che essi intendono fornire. Ad esempio, degli studi precedenti hanno dimostrato che il sistema operativo può abusare dell'interfaccia di gestione della memoria della CPU per essere notificato quando un TEE accede a regioni di memoria specificate dall'hacker, violando la riservatezza dei dati. La comprensione delle capacità di tipi di attacchi privilegiati porta quindi a progettare sistemi più accurati e a un ambiente informatico più sicuro per tutti.

In questa tesi, contribuiamo agli sforzi di comprensione delle capacità di tipi di attacchi privilegiati nel contesto dei TEE in quattro direzioni principali. In primo luogo, sviluppiamo l'attacco *Frontal*, che dimostra che sfruttando il sistema operativo per emettere interrupt frequentemente

x Sommario

porta la CPU ad esporre dettagliate tempistiche di esecuzione delle istruzioni, che possono essere utilizzate come canale laterale. Questo canale laterale è sufficientemente dettagliato da far trapelare le chiavi di crittografia da un TEE, così violando la sua riservatezza dei dati. In secondo luogo, dimostriamo che gli attuali TEE commerciali faticano a garantire la riservatezza del codice contro un attacco privilegiato. In particolare, osserviamo che l'uso di interpreti o compilatori JIT all'interno dei TEE – una scelta popolare per la loro convenienza e flessibilità – fa trapelare un numero significativamente maggiore di istruzioni confidenziali rispetto al caso in cui vengono invece utilizzate istruzioni native.

Il terzo e il quarto contributo riguardano i protocolli di attestazione, utilizzati per verificare che un TEE stia proteggendo una determinata applicazione. In entrambi questi contributi sottolineiamo l'impatto di aspetti precedentemente trascurati nei protocolli di attestazione. Nel terzo contributo, osserviamo che gli attacchi di tipo relay, un tempo ritenuti tollerabili visto le protezioni dei TEE, aumentano le capacità e pericolosità di un attacco privilegiato. Infine, nel quarto contributo, dimostriamo che gli attuali protocolli di attestazione presuppongono implicitamente la fiducia nel produttore dei TEE anche in fase di esecuzione, nonostante i produttori spesso affermino il contrario. Sebbene questa fiducia implicita nel produttore sia spesso trascurata, la nostra analisi mostra che si tratta di una minaccia concreta e che quindi dovrebbe essere tenuta in considerazione nei futuri protocolli di attestazione.

Aujourd'hui, notre vie dépend du fonctionnement sécurisé des ordinateurs dans des secteurs très divers, de l'énergie à la médecine. Cependant, les ordinateurs d'aujourd'hui exécutent des logiciels gonflés de complexité. Leurs vastes bases de code fournissent un système riche et polyvalent, mais la plupart des fonctionnalités ne sont souvent pas nécessaires dans leurs applications cibles. Cela augmente la base informatique fiable (TCB) – les logiciels et le matériel qui doivent être fiables pour que le système fonctionne correctement. Une base de confiance importante n'est pas souhaitable, car elle ne fait que donner aux attaquants une plus grande probabilité de trouver et d'exploiter les vulnérabilités. La majeure partie de cette complexité provient du logiciel système, c'est-à-dire du système d'exploitation (OS) et de l'hyperviseur. Malgré cela, la base de code du logiciel système ne peut généralement pas être retirée de la TCB, car elle s'exécute avec les privilèges les plus élevés.

Grâce à des primitives matérielles supplémentaires, les *environnements* d'exécution de confiance (TEE) brisent ce paradigme, permettant même au logiciel système d'être retiré de la TCB. La plupart des fabricants et des architectures de processeurs supportent une certaine forme de TEE : on les trouve sur les CPU Intel et AMD et sur les architectures ARM et RISC-V. Leur avènement est prometteur, car ils visent à permettre aux applications de fonctionner en toute sécurité aussi bien lorsque le logiciel système (plus privilégié) est malveillant que lorsqu'un attaquant physique peut altérer le système. Cependant, les garanties qui peuvent être fournies contre un attaquant aussi puissant et privilégié ne sont pas entièrement comprises et conduisent souvent à des conceptions de TEE qui font des compromis invalidant les protections qu'elles visent à fournir. Par exemple, des travaux antérieurs montrent que le système d'exploitation peut abuser de l'interface de gestion de la mémoire du CPU pour être notifié lorsque le TEE accède à des régions de la mémoire spécifiées par l'attaquant, ce qui brise la confidentialité des données. Comprendre les capacités des attaquants privilégiés conduit donc à des conceptions plus précises et à un environnement informatique plus sûr pour tous.

Dans cette thèse, nous contribuons aux efforts de compréhension des capacités des attaquants privilégiés dans le contexte des TEEs dans quatre directions principales. Tout d'abord, nous développons l'attaque *Frontal*, qui montre que l'utilisation du système d'exploitation pour émettre des interruptions fréquentes conduit le CPU à exposer des temps d'exécution

xii Résumé

d'instructions détaillés, qui peuvent être utilisés comme un canal latéral. Ce canal latéral est suffisamment détaillé pour faire fuir les clés de chiffrement d'un TEE et ainsi briser la confidentialité des données. Deuxièmement, nous montrons que les TEE commerciaux actuels ont du mal à assurer la confidentialité du code contre un attaquant privilégié. En particulier, nous observons que l'utilisation d'interprètes ou de compilateurs JIT dans les TEE – un choix populaire en raison de leur commodité et de leur flexibilité – entraîne la fuite de beaucoup plus d'instructions confidentielles par rapport à une base de référence où les instructions natives sont utilisées à la place.

Les troisième et quatrième contributions concernent les protocoles d'attestation, qui sont utilisés pour vérifier qu'un TEE protège une application donnée. Dans ces deux contributions, nous soulignons l'impact d'aspects précédemment négligés dans les protocoles d'attestation. Dans la troisième contribution, nous mettons en évidence le fait que les attaques de relais, qui étaient auparavant considérées comme tolérables compte tenu des protections du TEE, renforcent les capacités d'un attaquant privilégié. Enfin, dans la quatrième contribution, nous montrons que les protocoles d'attestation actuels supposent implicitement la confiance dans le fabricant du TEE au moment de l'exécution – bien que les fabricants prétendent souvent le contraire. Bien que cette confiance implicite dans le fabricant soit souvent négligée, notre analyse montre qu'elle constitue une menace concrète dans la pratique et devrait donc être prise en compte dans les futurs protocoles d'attestation.

#### Zusammenfassung

Unser heutiges Leben hängt vom sicheren Betrieb von Computern in den verschiedensten Bereichen ab, von der Energie bis zur Medizin mithilfe hochkomplexer Software. Ihre grossen Codebasen bieten ein reichhaltiges und vielseitiges System, aber die meisten Funktionen werden in ihren Zielanwendungen oft nicht benötigt. Dadurch erhöht sich die vertrauenswürdige Computerbasis (Trusted Computing Base – TCB) – die Software und Hardware, der vertraut werden muss, damit das System korrekt funktioniert. Eine grosse TCB ist unerwünscht, da sie nur eine höhere Angriffsfläche für Schwachstellen bietet. Der grösste Teil dieser Komplexität stammt von der Systemsoftware: dem Betriebssystem (OS) und dem Hypervisor. Trotzdem kann die Codebasis der Systemsoftware im Allgemeinen nicht aus der TCB entfernt werden, da sie mit den höchsten Privilegien ausgeführt wird.

Trusted Execution Environments (TEEs) versprechen dieses Paradigma zu ändern und ermöglichen es. Systemsoftware aus der TCB zu entfernen. Die meisten CPU-Hersteller und -Architekturen unterstützen irgendeine Form von TEE: Sie sind auf Intel- und AMD-CPUs sowie auf ARM- und RISC-V-Architekturen zu finden. Ihr Aufkommen ist vielversprechend, da sie darauf abzielen, Anwendungen sicher zu betreiben, sowohl wenn die (privilegiertere) Systemsoftware bösartig ist als auch wenn ein physischer Angreifer das System manipulieren kann. Die Garantien, die gegen einen so starken und privilegierten Angreifer gegeben werden können, sind jedoch nicht vollständig bekannt. Deshalb führen Designentscheidungen in TEE-Designs oft zu Kompromissen, die den angestrebten Schutz So haben frühere Arbeiten gezeigt, dass das zunichtemachen. Betriebssystem die Speicherverwaltungsschnittstelle missbrauchen kann, um benachrichtigt zu werden, wenn das TEE auf vom Angreifer spezifizierte Speicherbereiche zugreift, wodurch Vertraulichkeit der Daten verletzt wird. In der Zukunft wird das Verständnis der Fähigkeiten privilegierter Angreifer somit zu genaueren Entwürfen und einer sichereren Computerumgebung für alle führen.

In dieser Arbeit leisten wir einen Beitrag zu den Bemühungen, die Fähigkeiten privilegierter Angreifer im Kontext von TEEs zu verstehen, und zwar in vier Hauptrichtungen. Erstens entwickeln wir den Frontal-Angriff, der zeigt, dass die Ausnutzung des Betriebssystems zur Ausgabe von Interrupts häufig dazu führt, dass die CPU detaillierte Zeitangaben zur Befehlsausführung preisgibt, die als Seitenkanal genutzt werden können.

Dieser Seitenkanal ist detailliert genug, um Verschlüsselungsschlüssel von einem TEE auszuspähen und so die Vertraulichkeit der Daten zu brechen. Zweitens zeigen wir, dass aktuelle kommerzielle TEEs kaum in der Lage sind, die Vertraulichkeit des Codes gegenüber einem privilegierten Angreifer zu gewährleisten. Insbesondere stellen wir fest, dass bei der Verwendung von Interpretern oder JIT-Compilern innerhalb von TEEs – eine beliebte Wahl aufgrund ihrer Bequemlichkeit und Flexibilität – deutlich mehr vertrauliche Anweisungen durchsickern lassen als bei der Verwendung nativer Anweisungen.

Der dritte und vierte Beitrag bezieht sich auf Bescheinigungsprotokolle, mit denen überprüft werden kann, ob ein TEE eine bestimmte Anwendung schützt. In diesen beiden Beiträgen betonen wir die Auswirkungen von bisher vernachlässigten Aspekten in Attestierungsprotokollen. Im dritten Beitrag heben wir hervor, dass Weiterleitungs-Angriffe, die früher angesichts des TEE-Schutzes als tolerierbar galten, die Möglichkeiten eines privilegierten Angreifers erweitern. Im vierten Beitrag schliesslich zeigen wir, dass die derzeitigen Bescheinigungsprotokolle implizit davon ausgehen, dass dem TEE-Hersteller zur Laufzeit vertraut wird – obwohl die Hersteller oft etwas anderes behaupten. Während dieses implizite Vertrauen in den Hersteller oft übersehen wird, zeigt unsere Analyse, dass es in der Praxis eine konkrete Bedrohung darstellt und daher in zukünftigen Attestierungsprotokollen berücksichtigt werden sollte.

#### Acknowledgements

It is curiosity that sparked my interest in pursuing a PhD. Curiosity to understand how a complex system like a computer works, its limits, and how they can be abused. Curiosity to see if I had what it takes to push the boundaries of knowledge – to be the first to figure out something that no one had before.

Curiosity, however, only goes so far. Reverse engineering undocumented CPU behavior is less enchanting than one idealizes it to be. And after you pour so much of yourself into a project, nothing really prepares you to deal with its paper being rejected again and again.

Nonetheless, despite the difficult times, I found my PhD journey to be incredibly rewarding. I owe that to the people I crossed paths with throughout these years, to those that stepped up when I needed them, and that helped me grow both scientifically and personally. Ultimately then, while curiosity was the spark, it was the people that were alongside me during this journey that kept the fire alive until the end. I hope the following words will do justice in acknowledging the impact each had in helping me see this dissertation to completion.

First, I would like to thank my thesis supervisor, Srdjan Čapkun. Thanks for giving me the opportunity to do a PhD, the freedom to explore different topics, and the safety to take risks in my research. Thanks for leading by example and showing me that excellence and results can be achieved while treating your students and postdocs with dignity and respect – something that sadly is far from being a given in academia – and, at times, even going above and beyond for them. Throughout these years, we shared many stimulating discussions about science, life, and, really, about everything. Through them, I got to know you on a personal level as well, and I feel fortunate to have found in you not just a mentor but also a great friend.

Thanks to my thesis committee, Srdjan, Jon, Anil, and Shweta, for volunteering some of their valuable time to be part of my thesis committee. Thanks also for all the detailed comments and the discussions we had about my thesis. The final version of this dissertation certainly benefitted from them. I am also grateful to Kari Kostiainen for his feedback on the writing of this dissertation, and to Ania Jomard and Moritz Schneider for their help with, respectively, the French and German translations of the thesis abstract.

My day-to-day work benefitted immensely from the interactions with the brilliant people in the System Security group at ETH: Aanjhan, Hubert, Kari, Sinisa, Moritz, Aritra, Patrick, Mridula, Daniele, Karl, Marc, David, Friederike, Martin, Simon, Carolin, Claudio, and Giovanni, to name a few. Thanks for all the fun lunches together, trying to define what makes a sandwich a sandwich, a TEE a TEE, or figuring out who stole the pizzas from the fridge. I was always amazed at how easy it was to bounce technically challenging ideas off of you. Thanks also for the crazy memories from the conferences and summer schools that we traveled to together. I could not have asked for a better team to work with, and I am sure I will carry the friendships that formed with some of you throughout my whole life.

A particular mention goes to my office mate, Moritz Schneider. You impacted me and my research in many more ways than you probably realized. I always appreciated your way of arguing with me. Even when we had diverging views on a subject, you were able to quickly separate facts from speculation while staying respectful – allowing us to learn from each other's point of view. It fascinated me how often our discussions pondered on the meta and technicalities of topics seemingly unrelated to our work, all the while finding a way to influence and inspire it. I learned a great deal from interacting with you, not least the pragmatical but dedicated way you have to go about life and how you carry that into your work (and passions).

Thanks to my friends all over the world, and particularly in Zurich, Germany, the Netherlands, the UK, and Sardinia, for helping me keep my sanity and recharge my batteries while I worked on this thesis. Thanks for all the time we spent together, for the raclette dinners, for the ski trips, for the random trips across Europe, for always welcoming me no matter how long we were apart. Thanks for being there for me, not just to celebrate the victories but also to help me stand up again every time I fell.

It is hard to find the words to express how grateful I am to my better half, Ania, for her unwavering support throughout these years. Often the unsung heroine behind my work, making my life easy and light even through the stress of the looming deadlines. Thanks for having the patience to bear with "just until the next deadline" Ivan, and giving me the space I needed – I know how hard it was for you too. Thanks for showing me the pleasures that life has to offer and how to enjoy them to the fullest; that gave me the strength to keep pushing even when I thought I had none.

To my parents, Paride and Silvia: thanks for giving me the means to pursue my education, for the constant emotional support, and for enabling and empowering me to chase my dreams. You gave me the foundations to become the person I am today. To my siblings, Barbara and Massimo: thanks for always being there for me even when distance separates us. I know I will always be able to count on you no matter what. Thanks to my

family for always believing in me and what I can achieve. In you, I have my biggest supporters.

Finally, this thesis is dedicated to my grandfather, Ignazio Puddu. Thanks for instilling in me my machiavellian nature. Perhaps you did not make it to celebrate it with me, but you kept your promise anyway. I know how proud you would have been.

Ai miei genitori, Paride e Silvia: grazie per avermi dato i mezzi per sostenere i miei gli studi, per il costante supporto emotivo e per avermi permesso di inseguire i miei sogni. Devo a voi la persona che sono oggi. Ai miei fratelli, Barbara e Massimo: grazie per essermi sempre stati vicini nonostante la distanza ci separi. So che potrò sempre contare su di voi, qualunque cosa accada. Grazie alla mia famiglia per aver sempre creduto in me e in ciò che posso raggiungere. In voi ho i miei più grandi sostenitori.

Infine, questa tesi è dedicata a mio nonno, Ignazio Puddu. Grazie per aver instillato in me la mia natura macchiavellica. Forse non ce l'hai fatta a festeggiarla con me, ma so che hai mantenuto comunque la tua promessa. So quanto ne saresti stato orgoglioso.

Zurich, May 2023

# Part I Introduction and Background

### Chapter 1 Introduction

The words of this thesis are far more likely to be read from the screen of a computing device than as ink etched on paper. The rapid evolution of computers in the past 70 years has led to their proliferation in every aspect of our lives. From the first bulky machines designed to aid the census and perform heavy computational workloads, computers have now become ubiquitous in our homes, offices, cars, airplanes, and play a crucial role in sectors ranging from banking to medicine.

Each of these different deployment scenarios has its own unique set of applications and security requirements. In a healthcare setting, for instance, a computer may be utilized to access patient health records and manage prescriptions. This computer may be running multiple applications such as a web browser, a patient record management application, and a PDF viewer. It is crucial that these applications are properly isolated to ensure the confidentiality and integrity of their data and code. Without this isolation, if a web browser is compromised, an attacker could access sensitive patient health records and tamper with prescriptions, with potential consequences to patients' lives. Similar considerations apply in virtually all the sectors where computers are employed.

Despite the potential harm, in today's computing environment, it is common for multiple applications to execute on the same computer or server. One reason for this is economic viability. Running multiple applications on the same hardware allows for better utilization of resources and reduces costs. This is particularly important in cloud computing, where servers are shared among multiple tenants. However, just as the different applications in the hospital example discussed above, these tenants should not have to trust each other for the correct functioning of their deployments.

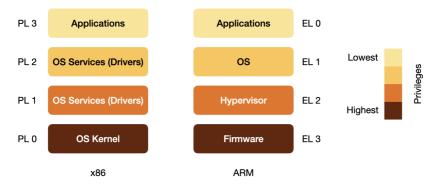

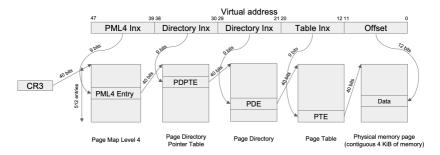

Allowing mistrusting software to share the same hardware has been a concern since the early days of computing. Already in the 1960s, barely ten years since the advent of mainframes, researchers recognized the need for hardware and software cooperation to enable concurrent programs to execute securely. The seminal paper from Dennis and Van Horn [1] called for a supervisor software to manage processes with the aid of hardware primitives. These concepts stood the test of time, becoming the pillars that support isolation in today's computers. Today, two hardware mechanisms are particularly relevant in aiding isolation: *virtual addressing* and *hierarchical privilege levels*. The operating system (OS) and the hypervisor,

4 1 Introduction

acting as the supervisor software, use paging to direct the central processing unit (CPU) virtual address (VA) translation. This gives each application and virtual machine (VM) the illusion of exclusive control of system memory. Hierarchical privilege level separation limits certain instructions and memory accesses to only be executed by the supervisor software, ensuring that low-privileged applications cannot modify VA mappings or access peripherals without cooperation from the OS.

The guarantees provided by these isolation mechanisms are well understood today. To hold, they rely on several assumptions, with the principal ones being the following two: i) the supervisor software is not compromised, and ii) no physical attacker, that is, the user and platform administrators are trusted. These assumptions are not exhaustive, as they, for instance, do not account for side channels [2], but they help in discussing the attacker model. If just one of these assumptions is broken, then the whole system is compromised. The first assumption is deeply linked to the hierarchical privilege layers and to the concept of the trusted computing base (TCB) – the software and hardware components that need to be trusted for the security of the overall system to be guaranteed. Due to it being more privileged, supervisor software is part of the TCB of every VM and application running in the system. Given its part in the TCB of every application, it is therefore crucial for supervisor software to not have any vulnerability.

The supervisor software does not just isolate applications from each other: it executes a scheduler, drivers, the filesystem, and manages network connections, to name a few. All these capabilities come at the cost of code size and complexity, which widens the attack surface. In short, having a large monolithic OS control the entire system makes it difficult to guarantee or verify a compromise-free environment. Thus, the damage inflicted by malware cannot be fully contained in this attacker model. Even if malware is installed as an unprivileged application, once it escalates its privileges to the privileges of supervisor software, it can control the entire system.

The second assumption, the absence of a physical attacker, is also problematic to justify in modern systems. Particularly, in a cloud computing setting, the cloud provider might not be fully trusted. An untrustworthy cloud provider has several avenues to compromise the execution of one of its tenants. Two exemplary ones are cold boot attacks [3] and employing a malicious hypervisor. Cold boot attacks allow to extract the content of DRAM. Even if the OS protects software accesses to peripherals, a physical attacker can completely bypass these restrictions. Having control of the hypervisor has similar consequences to

compromising the OS: the hypervisor is part of the TCB of every VM, so it can read or tamper with the tenants' VMs memory. The difference with the first assumption is that the malicious cloud provider does not need to find a vulnerability in the hypervisor – they can just install a malicious one to target a specific user. In summary, not only do both assumptions weakly hold in modern systems, but they are also impossible to verify by the user.

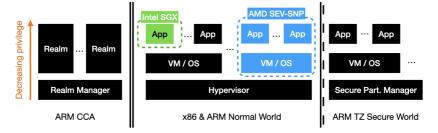

**Trusted Execution Environments.** The increasing difficulty in meeting these assumptions led in the 2000s to the first proposals aiming to remove the supervisor software from the TCB of applications and VMs [4, 5, 6, 7, 8]. These proposals and the many that followed with the same goals [9] are commonly known today as trusted execution environments (TEEs). While TEEs are still an area of active research, recently, they started being rolled out in major architectures. Some examples are Intel SGX [10], AMD SEV-SNP [11], ARM TrustZone [8], ARM CCA [12], and even on RISC-V with Keystone [13].

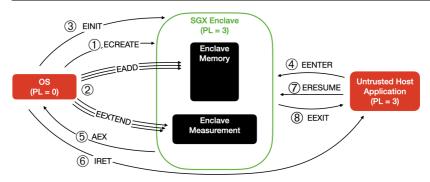

TEEs allow isolating *enclaves*<sup>1</sup> from a malicious environment by leveraging hardware primitives. Intel SGX and AMD SEV are the two most prevalent commercial TEE approaches on general-purpose devices. They aim to protect both against compromised supervisor software and against a physical attacker. Protection against a physical attacker is achieved thanks to the CPU encrypting and authenticating the enclave memory when stored in DRAM. Thus, even with a cold boot attack, at best, only encrypted memory can be recovered from DRAM.

Doing away with the supervisor software in the TCB requires two hardware-supported primitives: *tracking and isolating* the enclave context and *attestation*. Intel SGX and AMD SEV track context switches in and out of the enclave and ensure that only code running inside the enclave can access its memory and resources. The difference between the two approaches in this regard is that SGX enclaves include only low-privileged applications, while SEV enclaves isolate a full VM. Finally, attestation ties all of these protections together. The software itself cannot ascertain whether it is executing within an enclave or as a regular application because the OS could emulate the enclave environment. Attestation solves this impasse in TEEs by allowing to prove to a remote verifier, e.g., a client of a cloud service, that a remote code has been deployed inside an enclave. Attestation is based on cryptographic methods, wherein the CPU computes

<sup>&</sup>lt;sup>1</sup>Different implementations refer to the environment protected by the TEE in different ways. For instance, ARM CCA refers to them as *realms*. Throughout the thesis, we always refer to the environment protected by a TEE as *enclave*, irrespective of how the particular implementation refers to it.

6 1 Introduction

and signs the identity of the enclave with a secret key. Since the supervisor software cannot access the CPU secret keys, the remote verifier can securely deploy secrets to enclaves upon successful attestation, as it proves that the TEE protections are in place.

Protecting against a strong attacker, despite the hardware protections, is more challenging than initially thought. Enclaves still need to communicate with the system software through system or supervisor calls. The results of these calls can, however, be modified by the attacker through what is known as an Iago attack [14]. Control over the supervisor software allows noise reduction for traditional side-channel attacks [15, 16]. The capability to inspect and modify page tables allows controlled-channel attacks [17, 18, 19], a side channel entirely controlled by the attacker. Particularly, with controlled-channel attacks, the attacker can modify page tables so that the CPU notifies the attacker when the enclave accesses certain parts of its memory [17]. The attacks can also be made more stealthy by simply monitoring the accessed and dirty bits of the page tables [18, 19]. Having physical access and supervisor capabilities, the attacker can also undervolt the CPU [20, 21], glitching the execution in enclave mode and thus tampering with its integrity.

At their core, hierarchical isolation primitives and TEEs rely on the same principle: isolating memory between execution contexts. However, isolation against privileged attackers must account for all of the resources and the control they can exert over the system, as the described attacks highlight. While we understand how to effectively isolate against an unprivileged attacker, our understanding of the capabilities of a privileged attacker is not yet sufficient to fully meet the guarantees that TEEs promise.

#### 1.1 Thesis Contributions

Increasing the understanding of the capabilities of a privileged attacker guides the design of the software and hardware of TEE stacks. In this thesis, we contribute to the understanding of the capabilities of the attacker in four main directions. The first two focus on the impact that the ability to control interrupts has on instruction timing and confidential code leakage, while the last two highlight the need for attestation protocols to provide additional properties. In the following, we discuss these contributions in more detail.

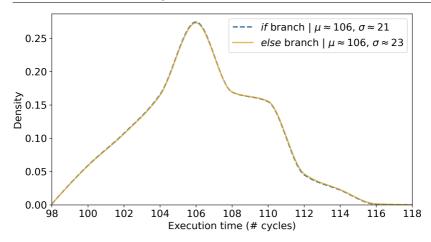

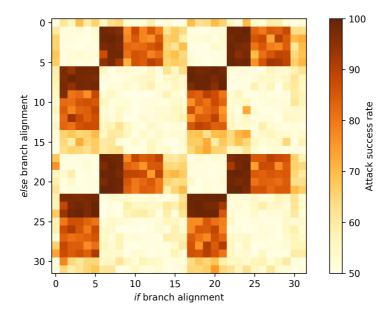

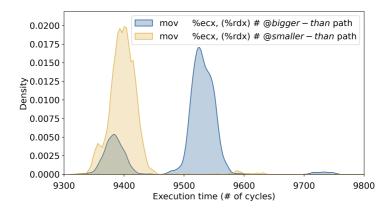

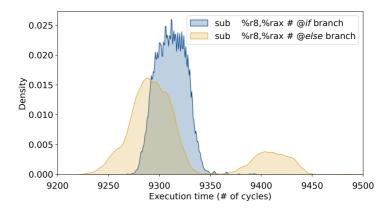

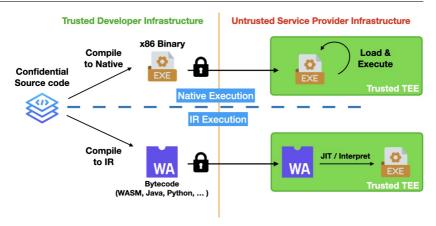

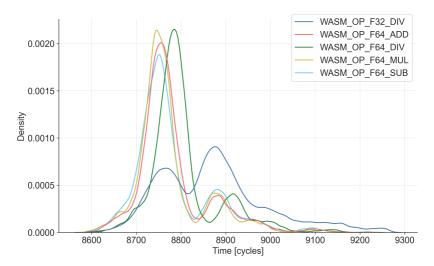

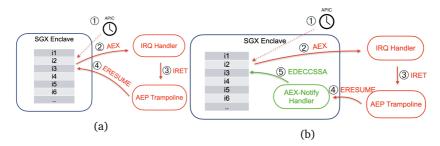

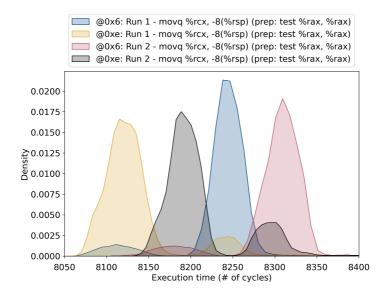

**Timing Leakage Under Frequent Interrupts.** We investigate the impact that issuing frequent interrupts has on instructions' timings. Our evaluation and experiments show that, when frequently issuing interrupts, instruction

execution times correlate with their virtual address. Particularly, we show that the feature of the virtual address that explains the timing variability is its alignment with respect to the CPU fetch window – the range of memory that gets fetched by the CPU to be decoded as instructions depending on the current program counter. We show that this correlation emerges when frequently issuing interrupts but not during normal execution – when the pipeline is not frequently flushed. Thus this attack can only be leveraged by a privileged attacker, e.g., in the context of a TEE. We also observe that since the correlation occurs based on the address, even the execution of the same instruction can produce different timings.

We leverage these observations to introduce the *Frontal* attack against Intel SGX enclaves. The Frontal attack leaks fine-grained control flow in branches containing the same instructions, even when they span less than a cacheline in size – which has been proven challenging in previous work. We demonstrate that it can achieve an accuracy of 99% in our synthetic binaries, but the resolution on real binaries is usually less. Nonetheless, we use it to exploit two cryptographic libraries: the Intel IPP Cryptography library and the mbedTLS library. For the mbedTLS proof-of-concept, we perform an end-to-end attack, using the Frontal attack to leak a full RSA key.

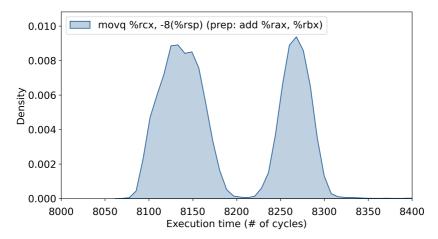

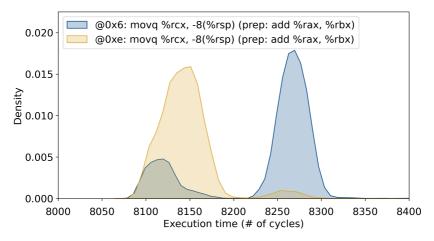

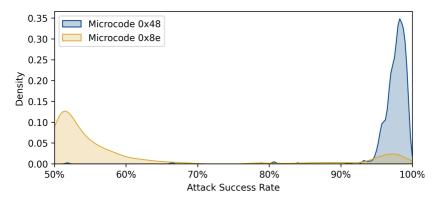

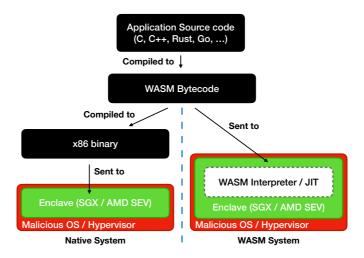

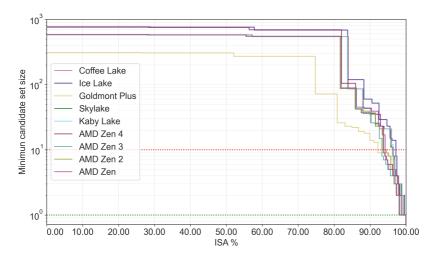

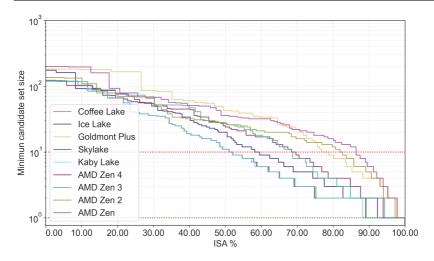

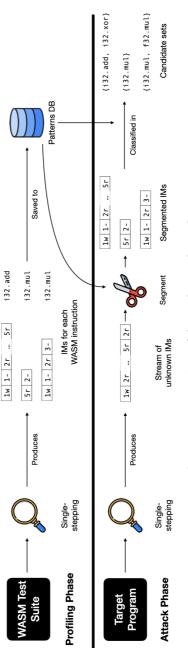

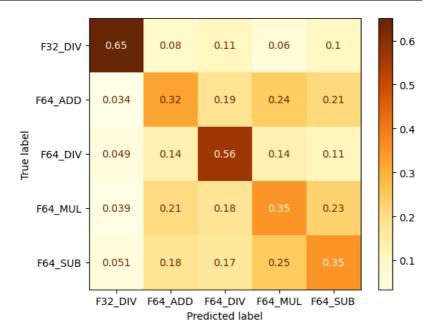

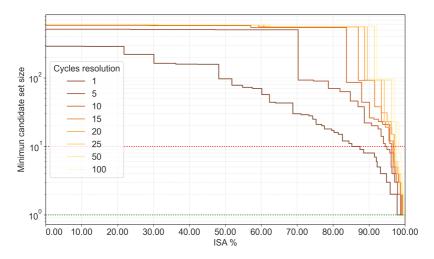

Evaluation of Code Leakage in TEEs. TEEs aim to provide not only data confidentiality but also code confidentiality. Several commercial [22, 23, 24, 25] and academic [26, 27, 28, 29, 30, 31, 32, 33] solutions exist aiming at leveraging code confidentiality in TEEs. We study whether code confidentiality can be truly provided on current TEEs, given the capabilities of privileged attackers. We generalize the existing proposals and show that they generally follow two approaches: native execution and intermediate representation (IR) execution. In native execution, the enclave executes the confidential instructions natively, while in IR execution, an interpreter or just-in-time compiler inside the enclave executes the confidential instructions. We develop a methodology to quantify instruction leakage under different privileged attacker strengths. The methodology leverages the fact that certain types of instructions leave different traces in the system, which can then be combined to construct a list of candidate instructions. We apply our methodology to both Intel and AMD CPUs. Our results highlight that IR execution inherently presents an amplification leakage compared to native execution because to execute one IR execution, multiple native instructions are required – the leakage of which can be combined.

8 1 Introduction

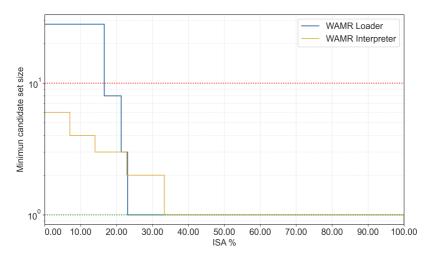

While in native execution, less than 10 % of the ISA instructions can be leaked, the observed leakage amplification in IR execution is significant. To showcase the danger with IR execution, we experimentally demonstrate a practical end-to-end instruction extraction attack against WAMR, a WASM runtime running on Intel SGX. Our attack was able to fully classify known programs and subroutines running inside the enclave and was able to extract with 100% confidence around 50% of an enclave executing a previously unseen program.

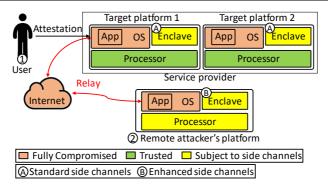

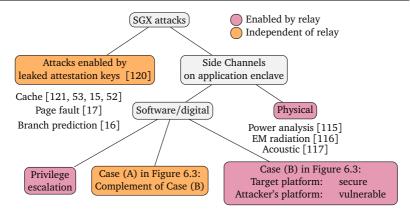

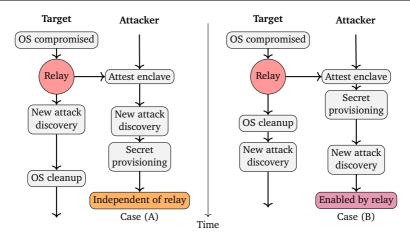

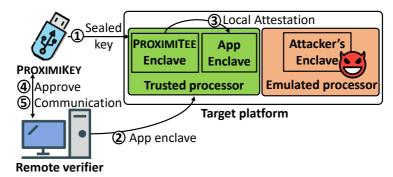

Relay-Safe Attestation. While relay attacks have been known for over a decade, their implications have not been thoroughly analyzed. TEEs' attestation protocols do not usually aim at preventing relay attacks. The rationale behind this choice is that attestation proves to the verifier that it is interacting with a genuine CPU. Since the CPU is genuine, it should not matter in which computer it is exactly. We show, however, that giving the attacker the capability to relay attestation to another platform enhances its capabilities. We observe that relay attacks increase the capability of the attacker to leverage side-channel attacks. For instance, they allow an adversary with only remote access to a platform (say after a compromise) to relay the attestation to a local platform over which it can also perform physical attacks (such as voltage manipulation). Relay attacks also allow a form of "downgrade attack" in which the attacker can relay to a platform that will never receive security updates and thus be exploitable in the future.

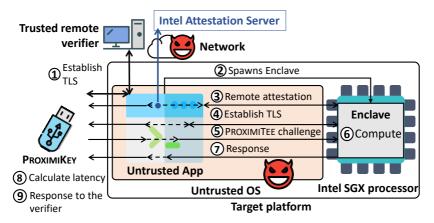

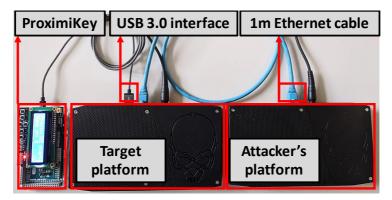

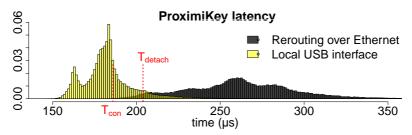

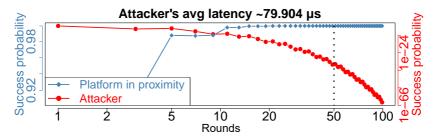

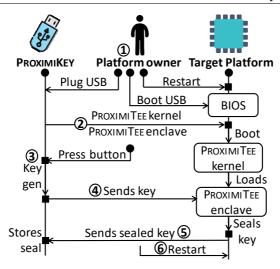

To mitigate these attestation relay attacks, we propose ProximiTEE, which enhances attestation with proof of proximity to a particular CPU. ProximiTEE relies on a physical device that can be connected to the specific target platform that the user wants to attest to. ProximiTEE requires no changes from the manufactures hardware and attestation designs at the cost of the extra device, which has to be connected to the server. We evaluate ProximiTEE and show with a prototype that relay prevention is practical in practice.

Security Analysis of Manufacturer's Runtime Trust. Trust in the hardware manufacturer is implicitly assumed when working with TEEs. Usually, the argument is that since the manufacturer produces the hardware that is being adopted, if they were to be malicious, they would simply compromise the hardware. This often leads to tolerating them as active parties in TEEs attestation protocols. We observe that manufacturers might not be malicious at manufacturing time or that their manufacturing facilities might not be compromised, yet their attestation facilities could be compromised, or they

could be compelled (e.g., with a lawful order) to compromise them. We thus argue that there is an advantage in separating the trust in manufacturers between manufacturing-time trust and runtime or post-deployment trust.

Intel and AMD claim that they cannot compromise attestation post-deployment. However, through our security analysis of their protocols and public patents, we show that if they were to be compromised at runtime, their current attestation mechanisms could be abused by an attacker (particularly a privileged one). With this analysis, we highlight the need to design attestation protocols that do not require runtime trust in the manufacturer.

#### 1.2 Thesis Organization

This thesis is organized into three main parts, Parts I to III. Part I opens up the thesis with the Introduction (this chapter) and the background in Chapter 2. Chapter 2 discusses the background relevant to the rest of the thesis, particularly focusing on Intel SGX and AMD SEV primitives. The rest of the thesis consists of Part II, related to information leakage in TEEs, and Part III, on analyzing attestation protocols shortcomings. In Part II, we discuss data leakage with the Frontal attack in Chapter 3 and introduce our methodology and analysis of code leakage in Chapter 4. The results of both Chapters 3 and 4 rely on the attacker's capability to fine-tune the delivery times of interrupts. We thus conclude the first part with Chapter 5 by discussing AEX-Notify, a new architectural extension with which Intel aims to curb these attacks.

In Part III, we discuss the dangers of relay attacks in Chapter 6, where we also discuss an enhancement to existing attestation protocols to prevent these attacks. Chapters 7 and 8 then conclude Part III by discussing the nuances and importance of separating the trust in the manufacturer between manufacturing time trust and deploy-time trust. The analysis in these chapters focuses mainly on how Intel (in Chapter 7) and AMD (Chapter 8) need to be trusted at runtime in their current attestation protocols.

Finally, we discuss the closing remarks of this thesis and future work in Chapter 9.

10 1 Introduction

#### 1.3 Publications and Author Contributions

This thesis is based, in part, on the following publications:

- [P1] Ivan Puddu, Moritz Schneider, Miro Haller, and Srdjan Čapkun. "Frontal Attack: Leaking Control-Flow in SGX via the CPU Frontend". 30th USENIX Security Symposium (USENIX Security '21).

- [P2] Ivan Puddu, Moritz Schneider, Daniele Lain, Stefano Boschetto, and Srdjan Čapkun. "On (the Lack of) Code Confidentiality in Trusted Execution Environments". *arXiv preprint 2212.07899* (2022) Under submission.

- [P3] Aritra Dhar, Ivan Puddu, Kari Kostiainen, and Srdjan Capkun. "ProximiTEE: Hardened SGX Attestation by Proximity Verification". Proceedings of the Tenth ACM Conference on Data and Application Security and Privacy (CODASPY '20). Best Paper Award.

These publications are the result of the collaboration and contributions of all the involved authors. In the following, when necessary, we refer to the authors of these publications with their initials. As Chapters 3, 4 and 6 are respectively based on [P1, P2, P3], they also contain contributions from the coauthors of the respective papers, including on the writing and figures. The same applies to Chapter 7, which is based on an unpublished report, coauthored with SC, and first written to coordinate a responsible disclosure. Next, we summarize the contributions made by this thesis' author, IP, to these four chapters.

Author Contributions. For Chapter 3, derived from [P1], IP implemented the code of the experiments, the proof-of-concept, and the defenses. In cooperation with the other coauthors, IP designed, executed, and analyzed the data of the experiments to reverse engineer the CPU behavior. IP performed the binary and source code analysis of the Intel IPP and mbedTLS library and executed and evaluated the attacks on the found vulnerabilities. IP evaluated the effectiveness of the defenses. IP coordinated the project across collaborators. All the authors contributed to the final version of the published manuscript.

For Chapter 4, derived from [P2], IP implemented the code of the framework to compute the candidate sets and collected the data. In cooperation with the other coauthors, IP analyzed and interpreted the instruction leakage data for native and IR execution. IP executed the experiments to collect the profiling data for the WASM segmentation

attacks. IP designed, implemented, and evaluated the end-to-end WASM attack. IP coordinated the project across collaborators. All the authors contributed to the final version of the published manuscript.

For Chapter 6, derived from [P3], IP, in cooperation with the other authors, conceptualized the risks posed by relay attacks, designed the protocols, and performed the security analysis. IP and *AD* implemented the protocols and collected the experimental data. In cooperation with the other authors, IP analyzed the data. All the authors contributed to the final version of the published manuscript.

For Chapter 7, derived from an unpublished report authored by IP and SC, IP had the original idea and conceptualized the attack. IP and SC defined the concrete threats posed by the attacks. All the authors contributed to writing the report.

#### 1.3.1 Other Publications

During his doctoral studies, the author of this thesis also coauthored the following publications, which are closely related to the work of this thesis:

- [R1] Ivan Puddu, Daniele Lain, Moritz Schneider, Elizaveta Tretiakova, Sinisa Matetic, and Srdjan Capkun. "TEEvil: Identity Lease via Trusted Execution Environments". arXiv preprint 1903.00449 (2019).

- [R2] Jawad Haj-Yahya, Jeremie S. Kim, A. Giray Yağlıkçı, Ivan Puddu, Lois Orosa, Juan Gómez Luna, Mohammed Alser, and Onur Mutlu. "IChannels: Exploiting Current Management Mechanisms to Create Covert Channels in Modern Processors". 2021 ACM/IEEE 48th Annual International Symposium on Computer Architecture (ISCA '21).

- [R3] Moritz Schneider, Aritra Dhar, Ivan Puddu, Kari Kostiainen, and Srdjan Čapkun. "Composite Enclaves: Towards Disaggregated Trusted Execution". IACR Transactions on Cryptographic Hardware and Embedded Systems (2021).

- [R4] Friederike Groschupp, Mark Kuhne, Moritz Schneider, Ivan Puddu, Shweta Shinde, and Srdjan Capkun. "It's TEEtime: Bringing User Sovereignty to Smartphones". *arXiv preprint 2211.05206 (2022) Under submission*.

In addition, the author of this thesis worked on projects that led to the following publications:

12 1 Introduction

[O1] Patrick Leu, Ivan Puddu, Aanjhan Ranganathan, and Srdjan Capkun. "I Send, Therefore I Leak: Information Leakage in Low-Power Wide Area Networks". *Proceedings of the 11th ACM Conference on Security & Privacy in Wireless and Mobile Networks (WiSec '18)*.

- [O2] Irina Calciu, Ivan Puddu, Aasheesh Kolli, Andreas Nowatzyk, Jayneel Gandhi, Onur Mutlu, and Pratap Subrahmanyam. "Project PBerry: FPGA Acceleration for Remote Memory". *HotOS '19*.

- [O3] Irina Calciu, M. Talha Imran, Ivan Puddu, Sanidhya Kashyap, Hasan Al Maruf, Onur Mutlu, and Aasheesh Kolli. "Rethinking Software Runtimes for Disaggregated Memory". *Proceedings of the 26th ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS '21)*.

- Yaohua Wang, [04] Orosa, Mohammad Sadrosadati, Jeremie S. Kim, Minesh Patel, Ivan Puddu, Haocong Luo, Kaveh Razavi. Juan Gómez-Luna. Hasan Hassan. Nika Mansouri-Ghiasi, Saugata Ghose, and Onur Mutlu. "CODIC: Low-Cost Substrate for Enabling Custom Functionalities and Optimizations". 2021 ACM/IEEE 48th Annual International Symposium on Computer Architecture (ISCA '21).

## Chapter 2 Background

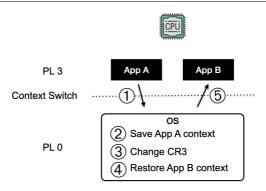

This chapter introduces the relevant background needed to understand the rest of the thesis. We first describe basic computer architecture topics, particularly showing how context switches work in a hierarchical privilege-level system. We then explain what changes trusted execution environments (TEEs) make to these basic systems. We generally focus on Intel SGX, AMD SEV-SNP, and ARM CCA, as at their core, these try to achieve similar objectives and are the most widely deployed TEEs to date. We then describe in more detail how SGX enclaves are initialized and how the operating system manages enclave context switches. Finally, we discuss how these mechanisms translate to AMD SEV enclaves.

#### 2.1 Computer Architecture Fundamentals

We now give a basic overview of a modern *computer architecture*. Computer architecture concerns the design of a computing system at different levels of abstraction: From how it is subdivided into individual hardware components, to the internal implementation of each of these components, and how they interface with each other and to software. Throughout this section, we touch on different design aspects of a modern computer architecture, focusing on how they give rise to security concerns and what mechanisms have been introduced to address these concerns.

#### 2.1.1 Hardware and Software

One of the crucial design aspects of a modern computing system is whether a given functionality should be implemented in hardware or software. This choice has profound implications in terms of performance, flexibility, cost, and security.

In terms of performance, generally, implementing a functionality on a dedicated hardware component or module makes it execute more efficiently and faster than if it was implemented by software. The downsides come in flexibility. As these components are tailor made for their target functionality, they could be under-utilized if their functionality is not often needed. On the other hand, general-purpose hardware, which is fully customizable by software, has the benefit of supporting virtually any application, with a trade-off in efficiency and performance compared to dedicated hardware.

14 2 Background

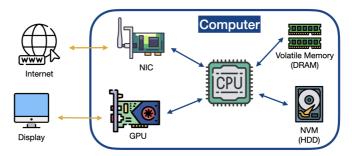

**Figure 2.1:** Example of a typical hardware configuration on a modern computing architecture. The edges between the components show the communication topology. Blue (dark) edges represent typical internal communication links, while the yellow (light) ones show how external entities are connected.

The most ubiquitous architecture nowadays, a CPU-centric architecture, strikes a balance at a system's level between these two extremes. We give a simplified view of this architecture in Figure 2.1. The figure depicts the various components found in the architecture and how they communicate with each other and the external world. At the core of the architecture. we can find the central processing unit (CPU), the only general-purpose hardware component in the system. The remaining hardware components are usually tasked with data acquisition, storage, and communication, to name a few. With this configuration, software that specializes the system for a particular application is mostly meant to execute on the CPU. This leaves other components with the job of aiding the CPU in executing specific sub-tasks. For example, the network interface card (NIC) and the graphics processing unit (GPU), depicted in the figure, help the CPU in networking and graphics processing tasks, respectively. While the CPU could perform both of these tasks, the NIC and the GPU do it far more efficiently than the CPU could, all the while relieving the CPU from performing them, thus freeing its computational resources for other tasks. Note how these two tasks are needed by a wide range of applications, thus justifying the presence of dedicated hardware for them despite their narrow functionalities. A second type of peripherals, shown in the picture, provides custom hardware for various types of memory extension. The CPU itself has some memory, such as read-only memory (ROM), which is non-volatile, and registers and caches, which are volatile<sup>1</sup>. What is important to take away from this is that

<sup>&</sup>lt;sup>1</sup>Volatile memory is memory that is not guaranteed to be preserved upon a system reboot.

the CPU has a limited amount of memory, generally not enough to handle the requirements of today's applications. This is why we find on the system separate hardware components providing additional pools of memory. That said, we will not delve into the advantages and disadvantages of having these non-integrated in the CPU, as it is out of scope for the thesis.

This brief description of the architecture is sufficient to give an intuition as to how these different components work together to form a computing system capable of handling a wide spectrum of applications, from weather forecasting to playing cute cat videos. Intuitively, each component could benefit from directly communicating with all the others. For instance, if a network packet just contains a frame that needs to be rendered on screen, the NIC could instruct the GPU to process it. However, direct communication between each component would go against the design principle we saw before, wherein each hardware component (besides the CPU) is specialized to perform only its given task. In the example of the video frame, the NIC would need to know how to interface itself with the particular GPU installed in the system. The problem with this approach is that the interface of these components is vastly different, not only across different manufacturers but also between models and versions. Recall that their advantage is to have functionality implemented in hardware, and having to support every other possible device in hardware immensely raises the complexity and cost of the hardware design. As a consequence, manufacturers release a particular type of software, known as *driver*, to facilitate this communication. Drivers expose an application programming interface (API) to the rest of the system, which allows other software to interact with the device. As drivers are software, they execute on the only component in the system designed to handle it: the CPU. Because all drivers run in the CPU, the CPU can communicate with all devices. Therefore, for the example mentioned above, the frame received by the NIC is first sent to the CPU, which can talk to the NIC thanks to the specific NIC's driver executing on the CPU. An application's software that received the network packet, and also executing on the CPU, then sends the frame to the GPU, thanks to the GPU drivers installed on the system.

To summarize, due to the fact that drivers execute on the CPU, the CPU is able to communicate with every component on the system, and thus takes in the role of setting up every component, and orchestrating the communication between them. This is shown by the blue (dark) edges in Figure 2.1, which show which communication links form between the components on the platform. The figure highlights how a star topology emerges wherein the CPU is involved in the communication between all

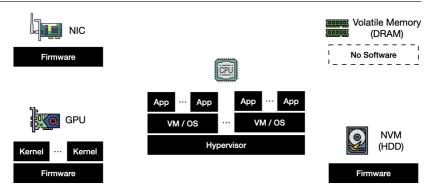

**Figure 2.2:** Software organization on the system

the other components. The only exception to this communication topology occurs with direct memory access (DMA). With DMA, the CPU can configure a portion of system memory (DRAM) to be available to any other peripheral in the system that supports it. The peripheral assigned to a particular range can then read and write to it without involvement from the CPU. This and the rest of the memory management has security implications, as we will see in the next sections.

# 2.1.2 The Trusted Computing Base

We depict the software executing on the various components of the system in Figure 2.2. Not surprisingly, as discussed before, most of the software executes in the CPU. This is indicated in the figure by the various applications, the Operating System (OS), Virtual Machines (VMs), and hypervisor executing on the CPU. Nonetheless, some software also executes on the other hardware components present in the system. For the most part, this software is known as *firmware*, and it takes care of managing several internal implementation-specific hardware resources and provides an interface to the drivers running on the CPU.

This type of software distribution across the system is typical in a CPU-centric architecture. The fact that the system can support multiple applications, even running simultaneously, is a testament to the versatility of this configuration. However, utilizing the same hardware for multiple applications comes with security risks. To explain them and how they are addressed, we briefly comment on how the system can be abused if no protection is in place. Imagine a scenario in which a banking application is executing on the system alongside another utility application, say a music