# **ETH** zürich

# A monolithic bipolar CMOS electronic-plasmonic high-speed transmitter

#### **Journal Article**

#### Author(s):

Koch, Ueli (); Uhl, Christopher; Hettrich, Horst; Fedoryshyn, Yuriy; Hoessbacher, Claudia; Heni, Wolfgang (); Bäuerle, Benedikt ; Bitachon, Bertold Ian (); Josten, Arne (); Ayata, Masafumi; Xu, Huajun; Elder, Delwin L.; Dalton, Larry R.; Mentovich, Elad; Bakopoulos, Paraskevas; Lischke, Stefan; Krüger, Andreas; Zimmermann, Lars; Tsiokos, Dimitris; Pleros, Nikos; Möller, Michael; Leuthold, Juerg ()

Publication date: 2020-06

Permanent link: https://doi.org/10.3929/ethz-b-000420206

Rights / license: In Copyright - Non-Commercial Use Permitted

Originally published in: Nature Electronics 3, <u>https://doi.org/10.1038/s41928-020-0417-9</u>

#### Funding acknowledgement:

688166 - A generic CMOS-compatible platform for co-integrated plasmonics/photonics/electronics PICs towards volume manufacturing of low energy, small size and high performance photonic devices (SBFI)

| 1  | A Monolithic Bipolar CMOS Electronic-                                                                                                                                                          |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2  | Plasmonic High-Speed Transmitter                                                                                                                                                               |

| 3  |                                                                                                                                                                                                |

| 4  | Ueli Koch <sup>1</sup> *, Christopher Uhl <sup>2</sup> , Horst Hettrich <sup>3</sup> , Yuriy Fedoryshyn <sup>1</sup> , Claudia Hoessbacher <sup>1,4</sup> , Wolfgang Heni <sup>1,4</sup> ,     |

| 5  | Benedikt Baeuerle <sup>1,4</sup> , Bertold Ian Bitachon <sup>1</sup> , Arne Josten <sup>1</sup> , Masafumi Ayata <sup>1</sup> , Huajun Xu <sup>5</sup> , Delwin L. Elder <sup>5</sup> ,        |

| 6  | Larry R. Dalton <sup>5</sup> , Elad Mentovich <sup>6</sup> , Paraskevas Bakopoulos <sup>6</sup> , Stefan Lischke <sup>7</sup> , Andreas Krüger <sup>7</sup> , Lars Zimmermann <sup>7,8</sup> , |

| 7  | Dimitris Tsiokos <sup>9</sup> , Nikos Pleros <sup>9</sup> , Michael Möller <sup>2,3</sup> , Juerg Leuthold <sup>1*</sup>                                                                       |

| 8  |                                                                                                                                                                                                |

| 9  | <sup>1</sup> ETH Zurich, Institute of Electromagnetic Fields, Zurich, Switzerland                                                                                                              |

| 10 | <sup>2</sup> Saarland University, Chair of Electronics and Circuits, Saarbrücken, Germany                                                                                                      |

| 11 | <sup>3</sup> MICRAM Microelectronic GmbH, Bochum, Germany                                                                                                                                      |

| 12 | <sup>4</sup> Polariton Technologies Ltd., Zurich, Switzerland                                                                                                                                  |

| 13 | <sup>5</sup> University of Washington, Department of Chemistry, Seattle WA, USA                                                                                                                |

| 14 | <sup>6</sup> Mellanox Technologies Ltd., Yokneam, Israel                                                                                                                                       |

| 15 | <sup>7</sup> IHP – Leibniz-Institut für innovative Mikroelektronik, Frankfurt (Oder), Germany                                                                                                  |

| 16 | <sup>8</sup> Technische Universitaet Berlin, Berlin, Germany                                                                                                                                   |

| 17 | <sup>9</sup> Aristotle University of Thessaloniki, Center for Interdisciplinary Research and Innovation, Thessaloniki, Greece                                                                  |

18 \*e-mail: <u>uelikoch@ethz.ch</u>, <u>leuthold@ethz.ch</u>

#### 20 ABSTRACT

21 In order to address the challenge of increasing data rates, next generation optical communication networks 22 will require the co-integration of electronics and photonics. Heterogeneous integration of these technologies has 23 shown promise, but will eventually become bandwidth limited. Faster monolithic approaches will, therefore, be 24 needed, but monolithic approaches using complementary metal-oxide-semiconductor (CMOS) electronics and 25 silicon photonics are typically limited by their underlying electronic or photonic technologies. Here, we report a 26 monolithically integrated electro-optical transmitter that can achieve symbol rates beyond 100 GBd. Our approach 27 combines advanced bipolar CMOS with silicon plasmonics, and addresses key challenges in monolithic integration 28 through the co-design of the electronic and plasmonic layers, including thermal design, packaging, and a nonlinear 29 organic electro-optic material. To illustrate the potential of our technology, we develop two modulator concepts – 30 an ultra-compact plasmonic modulator and, alternatively, a silicon-plasmonic modulator with photonic routing – both directly processed onto the bipolar CMOS electronics. 31

#### 32 1 Introduction

Future communications systems will require the co-integration of electronic and photonic systems. A key example is optical transmitters: electro-optical devices that convert electrical information to the optical domain for signal transmission. Such devices should currently offer dozens of Gb/s of data speed on a compact footprint, while being cost- and energy-efficient<sup>1</sup>. However, data centres and computing infrastructures will shortly require Tb/s data rates in a single optical link<sup>2,3</sup>. This calls for parallelization and high line data rates, and to achieve such data rates, the co-integration of high-speed electronics and high-bandwidth photonics is needed.

Integration of electronics and photonics is typically achieved heterogeneously using two separate chips. Transmitters using vertical-cavity surface-emitting lasers<sup>4</sup> have demonstrated energy-efficient data links at up to 56 GBd<sup>5-7</sup>. However, such directly modulated sources are bandwidth limited and higher symbol rates are hard to achieve<sup>1</sup>. Externally modulated sources and external modulators offer a photonic high-speed alternative, and photonic solutions based on lithium niobate<sup>8,9</sup>, indium phosphide<sup>10-18</sup>, silicon<sup>19-25</sup> and plasmonics<sup>26-29</sup> have emerged for intensity modulation and direct detection (IM/DD) systems. So far, heterogeneous transmitters in bondwire 45 assembly<sup>14,17,25,29</sup> have shown the highest symbol rates, achieving 222 GBd with plasmonics<sup>29</sup>, 192 GBd with indium 46 phosphide photonics<sup>17</sup>, and 56 GBd with silicon photonics<sup>25</sup>. However, parasitics at the mismatched bondwire 47 interface eventually constitute a bottleneck to the speed. Alternatively, three-dimensional bonding or flip-chip 48 assemblies can reduce the interface parasitics<sup>30</sup>, with 100 GBd operation being demonstrated using indium phosphide 49 photonics<sup>14</sup>. Yet, heterogeneous integration remains a costly and non-ideal approach since two separate 50 high-performance chips are interfacing at the most critical position of highest data bandwidth.

51 Monolithic integration could overcome this bottleneck and reach higher symbol rates using ultra-short direct connections known as on-chip vias. This use of a common substrate could offer a more compact footprint, simplified 52 53 testing and lower costs. However, most electronic and photonic technologies rely on two incompatible material 54 platforms, and thus new approaches are required. The silicon CMOS technology could provide a cost- and energy-efficient solution for both electronics and photonics<sup>31-34</sup>. A full photonic library on a zero-change CMOS 55 platform with a 10 GBd data link has, in particular, been demonstrated<sup>33</sup>, and has shown modulation at 40 GBd<sup>34</sup>. 56 57 However, standard CMOS technology is bandwidth limited and cannot achieve the symbol rates of high-speed heterogeneous demonstrations. Alternative monolithic solutions relying on indium phosphide or bipolar CMOS 58 59 (BiCMOS) technologies are therefore of interest. BiCMOS could be of particular value because it offers high-speed electronics and is CMOS-compatible. In addition, plasmonics is, in principle, an ideal counterpart as a photonic 60 technology<sup>35</sup>, offering bandwidths in excess of 500 GHz<sup>36</sup> and compatibility with a variety of substrate materials<sup>37</sup>. 61

62 In this Article, we report a monolithically integrated BiCMOS electronic-plasmonic transmitter<sup>38</sup> that can 63 achieve symbol rates beyond 100 GBd. The transmitter is comprised of high-speed BiCMOS electronic layers and a plasmonic layer on a single chip. The electronic layers offer a BiCMOS circuit that has been designed in line with 64 65 data-centre standards and performs a 4:1 power multiplexing to deliver on-off keying (OOK) signals to the plasmonic layer above. The plasmonic layer consists of compact and high-bandwidth plasmonic Mach-Zehnder modulators 66 67 (MZM). The electronic and plasmonic layers are interconnected by vias. The chips have been designed to operate at elevated temperatures and are tested in uncooled data modulation experiments. Operation at 120 GBd is 68 69 demonstrated using a silicon-plasmonic MZM, and an ultra-compact modulator is created that shows operation at

100 GBd on a footprint of  $29 \times 6 \mu m^2$ . Neither the BiCMOS electronics nor the plasmonic technologies operate at their fundamental speed limit, suggesting that our approach could provide a route to 200 GBd and beyond.

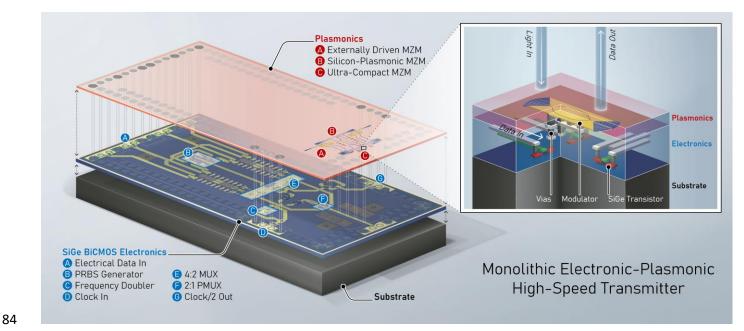

### 72 2 Concept

Our monolithically integrated high-speed transmitter is conceptually depicted in Fig. 1. The transmitter consists of BiCMOS electronic layers (blue) and a plasmonic top layer (red), which are implemented on a common substrate and connected through electrical wires (vias). The zoom-in to the plasmonic modulator shows the direct high-speed connection of electronics with plasmonics.

In the electronic layer stack (blue), electrical signals are generated to drive the plasmonic modulators. A multiplexer (MUX), designed in agreement to data centre standards, achieves highest data rates by performing a 4:1 multiplexing. The MUX input data is either externally supplied or generated on-chip. At the MUX output, a power multiplexing stage replaces the standard output driver amplifier to achieve highest signal quality in an energy-efficient implementation<sup>39</sup>. The SiGe BiCMOS platform hereby not only offers highest speeds and CMOS-compatibility but also enables monolithic integration with photonic components based on the silicon technology.

Fig. 1: Monolithic electronic-plasmonic high-speed transmitter. High-speed SiGe BiCMOS electronic layers (blue) with a top plasmonic layer (red)

monolithically integrated on a common substrate (black) and connected through on-chip vias (cylinders). The electronic circuit performs a 4:1

power multiplexing onto a single high-speed data rate channel. Data inputs are either external or from an on-chip PRBS generator. The optical

layer comprises plasmonic MZMs that convert the electrical signals onto intensity-modulated optical carriers. The zoom-in shows an

ultra-compact monolithically integrated MZM directly driven by high-speed electronics. The compact dimensions of plasmonic devices

demonstrate the perspective towards densest integration of highly parallelized transmitters as anticipated for future optical communication

links.

92 The plasmonic layer (red) comprises silicon photonics and gold plasmonics in a top layer – photonics for passive and plasmonics for active components. In this layer, plasmonic Mach-Zehnder modulators (MZMs) convert 93 94 the electrical signals into the optical domain through light intensity modulation for reception with direct detection. 95 Plasmonic modulators, despite having increased insertion loss, are an ideal solution as they offer ultra-compact footprint<sup>40</sup>, independence of photonic substrates<sup>37</sup>, high electro-optical bandwidth<sup>36</sup>, energy-efficient modulation<sup>41</sup> 96 97 and operation at CMOS-compatible voltages<sup>42</sup>. The transmitter comprises two types of plasmonic MZMs on a single substrate. A silicon-plasmonic MZM using photonic waveguides<sup>43</sup> was implemented together with an alternative 98 99 ultra-compact plasmonic MZM, where direct fiber-to-modulator coupling has been integrated into the device (see 100 zoom-in of Fig. 1). Both modulator types have been simultaneously driven, which is possible due to the compact size 101 and small capacity of plasmonic modulators.

The electronic layers and the plasmonic layer are connected by on-chip vias. Vias at the final power multiplexer (PMUX) stage bring the electrical output signal directly to the plasmonic modulators. The proximity of the PMUX outputs to the plasmonic modulators enables best signal quality at highest speed. Additional vias for high-speed electrical interfaces are connecting the bondpads in the top layer with the electronic circuit beneath. They give access to data input and clock in- and output. Note that the compactness of the plasmonic modulators allows describing them as electrically lumped elements. This renders their electrical impedance a design parameter and allows trading in driving voltage and energy consumption (see Methods).

109 Power dissipation in the high-speed electronics can lead to excess heating with temperatures hot spots above 110 150°C. Hence, thermal co-design of electronics, plasmonics and packaging was crucial to successfully demonstrating a monolithic transmitter (see Methods). Moreover, plasmonic switching in the modulators takes advantage of a 111 nonlinear electro-optic effect in an organic material<sup>44</sup>. Here, a new nonlinear organic electro-optic (OEO) material 112 2:1 HLD1:HLD2<sup>45</sup> has been applied for the first time in a device, which enables operation at elevated temperatures. 113 This organic material system mixes the anthracene-containing chromophore HLD1 and the acrylate-containing 114 115 chromophore HLD2, and allows for crosslinking without additional agents. Its thermal stabilization has guaranteed 116 reliable operation at temperatures beyond 120°C.

In this configuration, we demonstrate for the first time 120 GBd data modulation with a monolithicallyintegrated transmitter.

### 119 3 Electronics

The electronics of the monolithically integrated chip needs to meet multiple demands. First, the data input interface needs to be compatible with standard data centre sources. Second, a sufficiently high voltage swing with smallest possible power consumption must be generated to drive the MZM at symbol rates of at least 100 GBd. Third, a semiconductor technology well-suited for a photonic monolithic integration is required.

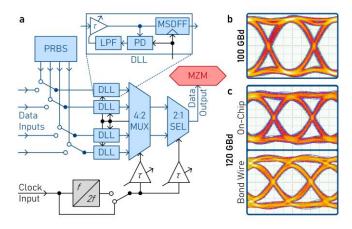

The electronic circuit that forms the MUX to drive the plasmonic modulator is shown with its corresponding building blocks in Fig. 2a. The design considerations are presented in the following with the focus on the monolithical integration together with an on-chip MZM. Details concerning the circuit development and performance can be found

in Refs.<sup>46,47</sup> for a previous version. The present implementation is detailed in Ref.<sup>48</sup>. A 4:1 MUX topology allows for 127 conversion of data-centre-compatible 4 × 25 Gb/s non-return-to-zero (NRZ) on-off-keying (OOK) input signals to a 128 100 Gb/s NRZ-OOK output signal at the MZM. Integrated delay locked loops (DLL) align the input data to the MUX 129 clock, see inset of Fig. 2a, and thereby automatically compensate for a timing skew between the data inputs<sup>49</sup>. 130 131 Regarding the use of the circuit in an integrated transmitter, a trade-off between performance and power 132 consumption has to be chosen. The presented design is optimized to reach highest performance and to provide a large flexibility in order to enable the characterization of the transmitter under various conditions (see Methods). 133 134 Thanks to a wideband circuit design, the chip can be operated at flexible data rates. For this, only the input clock 135 frequency has to be adjusted correspondingly.

136

Fig. 2: Electronic 4:1 power multiplexer performance. a Simplified block diagram of the electronics. The inset shows a DLL element comprising

an adjustable time delay, a master-slave-D-flipflop (MSDFF), a phase detector (PD) and a low-pass filter (LPF). b-c electrical eye diagram

measurements. Scaling: 2 ps/div, 200 mV/div. b 100 GBd on-chip reference eye diagram. c 120 GBd on-chip eye diagram compared to a 120 GBd

eye diagram via a bondwire interface.

To drive the MZM, a power multiplexer (PMUX) concept is chosen such that no additional driver amplifier is required. Instead, the final 2:1 selector (SEL) stage of the MUX directly drives the MZM. This offers several advantages<sup>39,47</sup>. For the present application, the good signal quality at high data rates and the low power consumption should especially be highlighted. The final 2:1 SEL has a power consumption of 0.9 W when operating with a nominal differential voltage swing of 2 V<sub>pp</sub> (1 V<sub>pp</sub> single-ended) at highest data rates. The PMUX concept can readily be extended to implement a PAM-4 transmitter by parallel connection of a second output stage with halved output swing and reduced power consumption. For the present design, this option is not implemented, however, it offers the potential to reach even higher data rates and higher energy efficiency. Design considerations concerning the adaption of the output interface to the MZM are presented in the Methods.

For the implementation, the BiCMOS semiconductor technology SG13G2 from IHP (adaptions in Methods) with a high transit frequency  $f_T = 300$  GHz of the bipolar transistors has been chosen. Compared to compound technologies (e.g. InP), which offer higher transit frequencies (e.g.  $f_T = 400$  GHz enabling the fastest MUX known so far with 222 Gb/s<sup>29</sup>), a BiCMOS technology brings the advantages of being cost-efficient and enabling a dense co-integration of high-speed bipolar electronics with standard CMOS signal processing. Moreover, there are developments of faster BiCMOS technologies that allow for an increase in the data rate of the presented circuit.

156 To assess the performance of the electronics (and of the MZM) without the need for an external data source, an on-chip pseudo-random bit sequence (PRBS) generator has been integrated and connected to the data inputs. 157 158 On-chip measurements with a wafer probe at a chip variant with an electrical output interface demonstrate the 159 performance of the electronics. The presented circuit delivers a flat operation for clock frequencies up to 90 GHz (limited by measurement equipment), which was tested by applying a 1-0-1-0 sequence<sup>48</sup>. Data modulation 160 experiments show a clear open eye diagram for a data rate of 100 Gb/s, see Fig. 2b. Due to the external 50  $\Omega$  load of 161 the measurement equipment, the voltage swing of 1.2 V<sub>pp</sub> is only half of the voltage swing at an integrated high-ohmic 162 163 MZM. A comparison between an on-chip measurement and when interfaced by bondwires at a data rate of 120 Gb/s 164 shows, how bondwires reduce the eye opening by almost 20 % and hereby degrade the signal quality, see Fig. 2c. This demonstrates the advantage of monolithic integration, where no bondwires are needed. 165

#### 166 4 Plasmonics

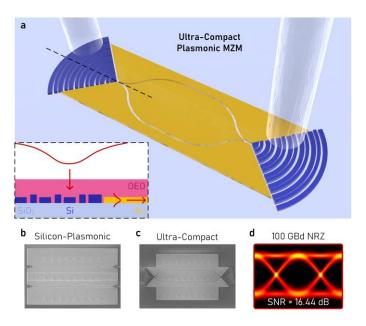

167 The plasmonic MZMs are the principal optical components in the demonstration for a monolithic integrated 168 transmitter. Three plasmonic modulator concepts were pursued in this work and integrated in the plasmonic layer: 169 Two silicon-plasmonic MZM concepts, one driven with the internal MUX and one externally driven as a reference, 170 and a new ultra-compact MZM concept. All three concepts are based on the 500 GHz plasmonic modulator 171 technology<sup>36</sup> and have a built-in asymmetry in order to tune the operation point in the optical domain without the

need of an electrical bias. Fig. 3 introduces the new concept, depicts the co-integrated modulators and demonstrates

the capabilities of monolithic integrated MZMs.

The first modulator concept is based on silicon photonic waveguides and splitters and relies on previous demonstrations from our group<sup>27,43</sup>. Standard single mode fibres connect to this device via grating couplers. Silicon photonic multimode interference coupler split and combine the optical carrier. A photonic delay line in one arm of the Mach-Zehnder interferometer allows choosing the MZM operation point by tuning the optical wavelength. The actual modulation is performed in two plasmonic phase modulators<sup>50</sup> that operate in push-pull mode. The co-integrated silicon-plasmonic MZM offers an extinction ratio of 35 dB with a total insertion loss of 25 dB. Fig. 3b depicts a scanning electron microscope (SEM) image of the two modulator arms of the actual monolithic MZM.

The second concept is the ultra-compact plasmonic MZM with a footprint of only 29 × 6 µm<sup>2</sup>, which is optically connected through a 24 µm pitched optical fiber array (OFA), see Fig. 3a. The direct fiber-to-slot coupling scheme shown in the inset efficiently converts an optical fiber mode directly into a plasmonic slot mode, omitting losses in intermediate photonic components<sup>40</sup>. Metallic y-splitters split and combine the optical carrier. Asymmetric arm lengths cause a phase difference between the two MZM arms and fix the operation point. Two plasmonic phase modulators constitute the MZM, which is driven in push-pull mode. Fig. 3c shows an SEM image of the ultra-compact modulator co-integrated with electronics, which offers an extinction ratio above 10 dB and insertion losses of 27 dB.

Fig. 3: Monolithic integrated plasmonic Mach-Zehnder modulators. a Ultra-compact plasmonic MZM with a footprint of 29 × 6 μm<sup>2</sup> for co-integration with electronics. The inset shows a schematic of the grating coupler for direct fiber-to-slot conversion. b-c SEM images of the actual monolithic modulators before OEO material deposition. b Silicon-plasmonic MZM and c ultra-compact plasmonic MZM. d Eye diagram of a 100 GBd data modulation experiment of a monolithically integrated MZM on the same chip using an external driver. 100 Gb/s NRZ-OOK were modulated with a BER < 10<sup>-5</sup>.

194 As a reference, an externally driven monolithic MZM was processed on the same chip to evaluate the performance of integrated plasmonic devices on BiCMOS chips – but without interface to the electronics. Hereby, the 195 plasmonic modulator with insertion losses of 25 dB and an extinction ratio of 30 dB has been operated under ideal 196 197 conditions at room temperature. An amplified electrical data signal (V<sub>p</sub> = 2.71 V, V<sub>rms</sub> = 1.55 V) has been applied to 198 the modulator via an RF probe, which results in a higher voltage swing than for integrated solutions and does not 199 need a bandwidth-limiting bondwire interface. 100 GBd data modulation was demonstrated with a bit error ratio (BER) < 10<sup>-5</sup> for two-level modulation (NRZ-OOK) (setup and measurement in Methods). Fig. 3d depicts the 200 201 corresponding eye diagrams. The received signal quality of 16 dB signal-to-noise ratio (SNR) indicates an enormous potential for symbol rates beyond 200 GBd<sup>51</sup>. 202

## 203 5 Monolithic Integration

188

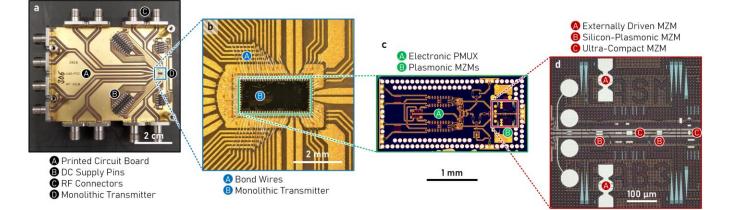

The monolithic integration of electronics and plasmonics was confronted with a set of challenges from platform compatibility over module assembly to high processing demands. While the electronic chips were produced in a SiGe BiCMOS foundry, the plasmonic top layer and the bondpads were post-processed directly onto the electronic

207 chip in the in-house facilities. In a final step, chip assembly and wirebonding to a dedicated printed circuit board (PCB) 208 as well as packaging and connectorisation were performed. The final monolithic test module is depicted in Fig. 4, 209 where the subfigures show zoom-ins at different scales – centimetre to micrometre scale – on which the monolithic integration was optimized. Fig. 4a shows the complete test module with DC and RF connectors and a PCB bringing 210 211 the differential input data, clock and DC supply to the transmitter chip. Fig. 4b shows the bondwire assembly 212 connecting PCB and transmitter chip. Fig. 4c shows a microscope image of the monolithic transmitter chip. Electronics and plasmonics were integrated on the same chip. A zoom-in to the plasmonic devices is shown in the last subfigure, 213 214 see Fig. 4d.

215

Fig. 4: Blow-up of the monolithic transmitter assembly. a Full transmitter assembly with PCB, DC supply pins and RF connectors. b Monolithic

transmitter chip connected via bondwires to the PCB. c Monolithic transmitter chip. d Zoom-in onto the output stage with the plasmonic MZM

devices on top of the electronic driver circuits.

The electronic chip features five output positions, which are driven simultaneously. This allows the implementation of multiple photonic components for evaluation – among which are the two plasmonic MZM concepts presented above. This placement of multiple modulators is only possible for modulators with small capacitances, whose simultaneous operation does not affect the electrical signal quality along the output transmission line. Such an adaption of the electronic MUX would not be possible with alternative photonic concepts.

A major challenge for monolithic integration is the high temperature environment in proximity to electronics. Recent demonstrations showed temperature stability in organic-based plasmonic modulators up to 75°C<sup>41</sup>, while the electronic chips reach 150°C at the core and up to 125°C at the output stage. Thermal modelling of the transmitter chip allowed for improved placement of the modulators along the output transmission line (see Methods). Still, to prevent degradation at high temperatures, a new nonlinear organic electro-optic material 2:1 HLD1:HLD2 was developed<sup>45</sup>. A crosslinking procedure stabilized the organic material such that it can withstand temperature above 120°C (see Methods). On-chip temperature measurements verified uncooled operation of the monolithic transmitter at local temperatures above 112°C. This is the first demonstration of plasmonic transmitters operating in such elevated temperature environment.

# 233 6 Monolithic Transmitter Performance

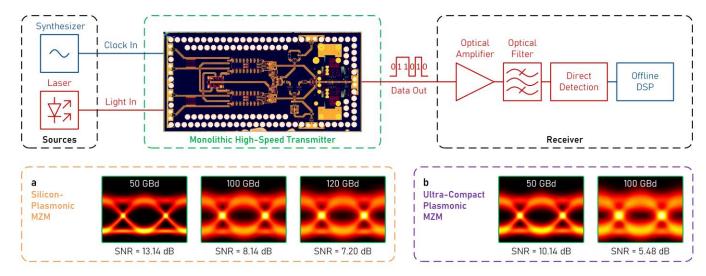

234 The monolithic transmitter was tested in a data modulation experiment with symbol rates of up to 120 GBd 235 under uncooled ambient air conditions and without encapsulation. The experimental setup is schematically given in 236 Fig. 5. An RF synthesizer serves as a clock source for the electronic circuit, which generates a PRBS data sequence of 237  $2^9$ -1 bits with symbol rate of twice the input clock frequency. An external laser serves as light source and delivers 5 238 to 11 dBm optical input power to the chip (measured in fiber before chip). Light is coupled in and out of the monolithic 239 transmitter through optical fibres. Two types of plasmonic MZMs (see section 4) were simultaneously driven – a 240 silicon-plasmonic MZM and an ultra-compact plasmonic MZM. The modulated optical signal was transmitted over an 241 optical fiber link to the receiver. The signal was amplified and filtered before being received with direct detection by 242 a single photodiode. Five million samples of the converted signal are captured using 63 GHz real-time oscilloscope 243 with 160 GS/s. Offline digital signal processing (DSP) was applied for signal recovery and equalization. Fig. 5a and b 244 show the eye diagrams of different data rates for the two MZM types (full details in Methods). 120 GBd were modulated with the silicon-plasmonic MZM with a BER of 1.74 · 10<sup>-2</sup> and 100 GBd with the ultra-compact design with 245 246 a BER of  $3.95 \cdot 10^{-2}$ . The lower-speed performance of the ultra-compact MZM is associated to a non-optimal operation 247 point of the MZM, as the device is only tuneable to the ideal quadrature operation point through a voltage bias. Here, a voltage bias in the electronic layer has been omitted in order to guarantee maximum signal quality at highest speed. 248 Still, both BERs are below  $4 \cdot 10^{-2}$  as required for successful soft-decision forward error correction<sup>52</sup>. 249

250

Fig. 5: Data modulation experiment with monolithic transmitter. The transmitter is operated using on-chip PRBS generation. The symbol rate

thereby corresponds to twice the input clock. Optically, light from a laser source is coupled to the plasmonic MZMs, where it is modulated before

being transmitted via a fiber link. At the receiver, the optical signal is amplified and filtered before being launched to a direct detection receiver. **a** Eye diagrams and SNR for 50, 100 and 120 GBd as obtained with the silicon-plasmonic MZM. **b** Eye diagrams and SNR for 50 and 100 GBd

measured with an ultra-compact plasmonic MZM.

# 256 7 Conclusions

257 Our approach offers a solution to a key challenge in next generation communication networks – the high-speed co-integration of electronics and photonics - and provides a route to overcome the speed limitations in 258 259 current transceiver systems. We developed a monolithic integration platform that combines high-speed BiCMOS 260 electronics with high-bandwidth plasmonics connected through direct on-chip interfaces. The platform offers high-speed data transmission, achieving symbol rates beyond 100 GBd. This was achieved through the co-design of 261 electronics and photonics, including thermal design and a nonlinear organic electro-optic material. Both the BiCMOS 262 263 electronics and plasmonic technologies are not yet at their limits, and symbol rates beyond 200 GBd should be 264 possible.

# 265 8 Methods

# **266** 8.1 Electronic Advantages of Monolithic Integration

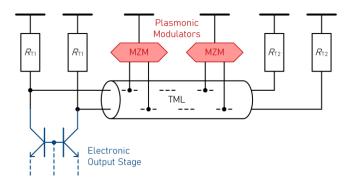

267 Due to the monolithical integration of photonics and electronics on a single chip, the design of the output 268 interface as shown simplified in Extended Data Fig. 1 can be adapted to the MZM load. In contrast, for systems with 269 an external MZM, the output impedance of the electronics ( $R_{T1}$ ) is typically designed as 50  $\Omega$  to match the

270 characteristic impedance of transmission lines (TML). As the MZM ( $R_{T2}$ ) is typically matched to 50  $\Omega$  to terminate the 271 far end of the external TML, the voltage swing at the MZM is only half the source voltage swing for an open output  $(R_{T2} \rightarrow \infty)$ . In case of the monolithically integrated plasmonic MZM, a termination at both ends is not required as the 272 size of the MZM is small and thus can be assumed as electrically lumped. Thus, a single termination that acts as a 273 274 simple load resistor is sufficient, which doubles the output voltage swing compared to an external MZM without an 275 increase in current consumption. In principal, because of the low MZM load capacitance, the matching can also be 276 chosen larger than 50  $\Omega$ , which even decreases the current consumption further. For the current implementation, 277 however, a concept is chosen, where an on-chip TML is matched at one end only by its characteristic impedance of 50  $\Omega$  ( $R_{T1} \rightarrow \infty$ ,  $R_{T2}$  = 50  $\Omega$ ). This allows multiple positions to place the MZM and thus gives a degree of freedom for 278 279 the experiments by choosing an optimal position with respect to temperature, signal quality and integration 280 processing. In our experiments, four MZMs are positioned at dedicated positions along the TML. In the design of the 281 electronics, the MZM capacitance is modelled by an increase in the distributed TML capacitance. The related TML 282 inductance is designed for a wave impedance of 50  $\Omega$ . That allows for a single 50  $\Omega$  termination at the end of the TML whereby the signal amplitude along the TML (i.e. at each of the MZMs along the TML) is approximately constant. 283

In addition to the advantages of the single termination of the lumped MZM, the monolithic integration significantly reduces parasitic inductances and capacitances of the output interface as the interconnect length between output stage and MZM is much shorter than for a heterogeneous approach as neither bondpads nor bondwires are required. This lead to a higher bandwidth at the MUX-MZM interface.

Extended Data Fig. 1: Simplified interface between electronic output stage and plasmonic Mach-Zehnder modulator (MZM). Typically, both

output stage and modulator are terminated by 50 Ω. In our case, the plasmonic MZM can be modelled as electrically lumped, which allows for

single-end termination. Hence, the driving voltage is doubled without increase in energy consumption. Additionally, such an approach allows

tuning of the output impedance to specific needs.

#### 293 8.2 Adaption of BiCMOS Process & Post-Processing

288

To enable the monolithic integration of plasmonic modulators on a BiCMOS electronic chip, the standard BiCMOS fabrication process has been adapted. Normally, the BiCMOS platform does not provide a flat topography at the end of the backend of line (BEOL) process and inter-metal vias are not directly accessible. To enable electronic-plasmonic integration, the top-metal2 interconnect level and passivation were omitted and the chemical-mechanical polishing process was optimized to allow for both low resistance access to the interconnect vias (about 2  $\Omega$  per electrode or 16  $\Omega$  per via) and a smooth surface for modulator post-processing with a root mean square roughness of 0.35 nm.

The post-processing of the plasmonic modulators was performed directly on top of the BiCMOS electronic chip and aligned to the driver's output vias. The passive silicon-photonic structures were etched into a 220 nm thick silicon layer, which was deposited at 300°C in plasma-enhanced chemical vapour deposition. The plasmonic modulators were structured using a lift-off process for 150 nm of gold deposited by electron-beam evaporation. In a last step, the OEO material was deposited by spin-coating. In order to stay below the thermal budget of a BiCMOS electronic chip, all processes were performed at temperatures not exceeding 300°C.

#### **307** 8.3 Specifications of the Transmitter Module

The main specification of a transmitter module is its performance in terms of maximum symbol rate, which was targeted in this demonstration. However, side specifications such as energy consumption and active device area

are becoming more and more relevant with increasing integration. Extended Data Fig. 2 shows both active area and 310 311 power consumption for each of the electronic circuit parts. The final 2:1 SEL and the high-speed clock distribution 312 (50 GHz) are the critical electronic components that have to be integrated on the transmitter chip. The other circuit parts are optional and are implemented to show advanced functionalities and for testing purposes. First, a 4:2 MUX 313 314 is implemented in order to allow external data input at 25 GBd as in former data centre standards for NRZ. Second, a 315 circuit for input data alignment allows compensating for a timing skew on-chip. Third, a reference clock out is added as an optional feature for clock synchronization in the measurement system. Further, a frequency doubler serves as 316 317 an alternative way to reach high-speed clock frequencies exceeding externally available speeds. Last, an on-chip PRBS generator offers convenient and fast testing capabilities without external data input and complements the external 318 319 data inputs. Regarding the power consumption, the consumed energy-per-bit amounts to 28 pJ/b for the critical 320 on-chip circuit parts and 99 pJ/b for the full transmitter electronics including all optional features. To analyse the data 321 rate per unit area, the footprints of the plasmonic modulators have to be measured. The area of the silicon-plasmonic 322 MZM covers 13,000  $\mu$ m<sup>2</sup>, while the ultra-compact plasmonic MZM occupies an extremely compact area of only 400  $\mu$ m<sup>2</sup>. By adding these values to the active area of the critical electronic components, a data rate per unit area of 323 2.39 Tb/s/mm<sup>2</sup> for the silicon-plasmonic and of 2.65 Tb/s/mm<sup>2</sup> for the ultra-compact transmitter is found. 324

| Circuit Parts                          | Active Area | Power |

|----------------------------------------|-------------|-------|

| Final 2:1 SEL (MZM driver)             | 13,200 μm²  | 0.9 W |

| High-speed clock distribution (50 GHz) | 24,150 μm²  | 1.9 W |

| Subtotal for critical components       | 37,350 μm²  | 2.8 W |

|                                        |             |       |

| 4:2 MUX                                | 60,500 μm²  | 1.4 W |

| Input data alignment                   | 288,000 μm² | 2.4 W |

| Reference clock output                 | 24,000 μm²  | 0.9 W |

| Frequency doubler                      | 35,200 μm²  | 0.7 W |

| PRBS generator                         | 101,000 µm² | 1.7 W |

| Total for all components               | 546,050 μm² | 9.9 W |

325

- Extended Data Fig. 2: Active area and power consumption per circuit part. The operation-critical functions (2:1 SEL and clock distribution) are

separated from the optional parts for advanced functionalities and for measurement purposes.

#### 328 8.4 High Temperature Environment

Monolithic transmitters experience a high temperature environment due to power consumption on smallest areas. This has a significant influence on the transmitter performance. The temperature distribution on a transmitter chip has therefore been computed in simulations. The power is dissipated mainly in the transistors and resistors in

the electronic layers and the released heat is conducted to the chip backside, which is coupled to a heat sink using a 332 333 thermally conductive adhesive. The thermal model consists of the chip, which is discretized as an FEM tetrahedral 334 mesh, and the adhesive modelled by its thermal surface resistance to the heat sink, which is considered as a constant temperature constraint. As the adhesive coverage of the chip backside is not known exactly, two cases are 335 336 considered: ideal and reduced thermal conduction to the heat sink. The temperature map for the reduced case is 337 depicted in Extended Data Fig. 3. A maximum temperature of 156°C has been simulated at the core, which decays just below 100°C towards the chip edges. Multiple output positions to place the modulator have been implemented. 338 339 Beneath every odd output position and beneath the MUX core, a temperature diode has been placed to measure the 340 local on chip temperature. The measured values from a purely electronic chip and a post-processed transmitter chip 341 are stated in the table inset of Extended Data Fig. 3. The electronic chip thereby agrees well with the ideal conducting 342 simulation, while the post-processed transmitter chip experiences about 20°C higher temperatures. The same 343 difference is found in simulations for lower thermal conduction to the substrate. Therefore, the temperature rise is 344 assumed to be caused by the adhesive for transmitter assembly on the PCB.

| $ \begin{array}{c} - 156 \\ - 150 \\ - 145 \\ - 140 \\ - 135 \\ - 130 \\ - 125 \\ - 120 \\ - 125 \\ - 120 \\ - 115 \\ - 110 \\ - 106 \\ - 100 \\ - 97 \\ \end{array} $ |       | Y     | 1 3   | 6     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Position                                                                                                                                                               | Core  | MZM1  | MZM3  | MZM5  |

| Simulated (ideal thermal cond.)                                                                                                                                        | 135°C | 106°C | 88°C  | 82°C  |

| Simulated (reduced thermal cond.)                                                                                                                                      | 156°C | 124°C | 112°C | 106°C |

|                                                                                                                                                                        |       | 10/00 | 0100  |       |

| Measured (w/o post-processing)                                                                                                                                         | 151°C | 106°C | 91°C  | 81°C  |

345

346 Extended Data Fig. 3: Temperature map of monolithic transmitter. Thermal simulations of the electronic circuit revealed the temperatures listed

347 in the table inset, which have been compared to measurements with on-chip temperature diodes. Ideal and reduced thermal conduction to the

348 substrate match well with measurements on a raw electronic chip and a post-processed transmitter chip, respectively.

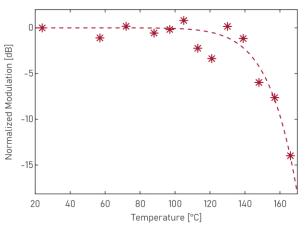

#### **350** 8.5 Temperature-Stable Nonlinear Organic Electro-Optic Material

Temperature-stable nonlinear organic electro-optic (OEO) materials are a requirement for stable operation of monolithic integrated plasmonic modulators. Besides temperature stability, the OEO material should maintain its high electro-optic activity and large intrinsic bandwidth. The OEO material composite 2:1 HLD1:HLD2 exhibits exactly these properties<sup>45</sup>. The material's glass temperature can rise by up to 100°C to a maximum of 175°C using a crosslinking procedure while keeping a maximum thin-film electro-optic coefficient  $r_{33}$  of about 286 pm/V at 1310 nm wavelength. A thermostability measurement over 500 hours at 85°C in a vacuum oven confirmed the long-term stability (99%) of the organic material.

358 In this work, we applied the OEO material 2:1 HLD1:HLD2 for the first time in an actual device and 359 demonstrated data modulation at temperatures above 112°C. The OEO material was poled with a poling field of 360 180 V/µm and crosslinked at 150°C. Note that the monolithic modulators were connected to the electronics during 361 this process. The in-device temperature stability was evaluated by steadily increasing the chip temperature and measuring the modulation efficiency using a sinusoidal signal at 60 GHz phase modulated onto an optical carrier at 362 1550 nm wavelength. Extended Data Fig. 4 depicts the measurement results. The in-device OEO performance shows 363 stable operation up to 140°C after which the performance starts to degrade. The small dip at about 120°C is associated 364 365 to fluctuations in the measurement setup due to fiber instabilities because of thermal fluxes.

367 Extended Data Fig. 4: Temperature stability of the nonlinear organic electro-optic material. Stable operation until about 140°C was measured

368 with a drastic degradation when reaching the glass temperature of 150°C. The small dip at 120°C is due to thermally induced setup fluctuations.

369 The trend line (dashed) serves to guide the eye.

366

#### **370** 8.6 Characterization of Monolithic Modulators

371 The two plasmonic modulator concepts were characterized in optical transmission measurements. Typical 372 silicon-plasmonic MZMs achieve fiber-to-fiber insertion losses of 17 dB. In this first monolithic implementation, the 373 insertion losses are higher, which is attributed to the following reasons. First, monolithic integration requires the use 374 of polycrystalline or amorphous rather than crystalline silicon in the photonic sections. Second, longer Mach-Zehnder 375 configurations were chosen to guarantee sufficient modulation margin. The monolithic silicon-plasmonic modulators 376 were measured to deliver 25 dB total insertion loss (fiber-to-fiber) at a wavelength of 1549 nm with a large extinction 377 ratio exceeding 35 dB. Through cut-back measurements, the losses can be attributed to 5.5 dB per grating coupler, 378 1 dB per photonic-plasmonic converter and 12 dB plasmonic propagation loss in a 20 µm long and 75 nm wide 379 plasmonic slot waveguide. The ultra-compact plasmonic MZM was showing fiber-to-fiber losses of 16.5 dB in test 380 structures. These losses are assigned to 6.5 dB plasmonic propagation loss, 4.5 dB per grating coupler and y-splitter, 381 and an extra 1 dB fiber array insertion loss. In the monolithic version, the total transmission was -27 dB (on-state 382 equivalent). The additional losses come from a longer plasmonic modulator section (14 dB in a 24 μm long modulator) 383 and slightly lower grating coupler and splitter efficiency (6 dB). With progress in technology, we anticipate total 384 insertion losses to reach values below 10 dB for plasmonic modulators. Lower losses can be achieved e.g. by 385 introducing a differential signal operation<sup>42</sup>, which will allow to reduce the modulator length by a factor two, or by improving the nonlinear efficiency of the crosslinked OEO material<sup>45</sup>. Thus, the fundamental plasmonic losses can be 386 387 reduced below 5 dB. Further, by transferring the plasmonic modulator technology to photonic fabrication sites, the 388 fiber-to-chip coupling losses can be reduced to values below 2 dB alongside with a reduction in silicon waveguide 389 propagation losses<sup>53</sup>.

The electro-optic performance of plasmonic modulators using the OEO material 2:1 HLD1:HLD2 was measured on a reference plasmonic phase modulator. For this purpose, the OEO material was stabilized for high-temperature environments using a crosslinking procedure, aged for 28 days and measured at 100°C. At 60 GHz, a voltage-length product of  $V_{\pi}L = 240 V\mu m$  was extracted for a phase modulator. For the monolithic Mach-Zehnder modulators demonstrated in this work, it can be halved to 120 Vµm and corresponds to a  $V_{\pi}$  voltage of 6 V. From the voltage-length product, a nonlinear electro-optic coefficient  $r_{33} = 100 \text{ pm/V}$  is estimated.

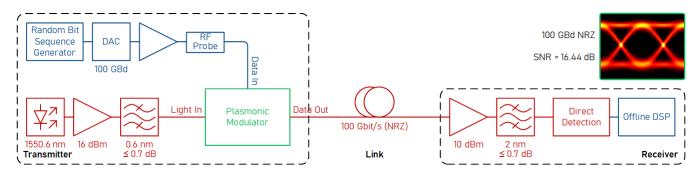

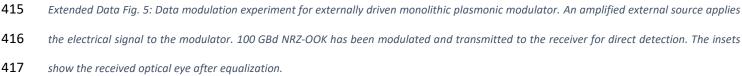

#### **396** 8.7 Externally Driven Monolithic Modulator

414

397 On the monolithic transmitter chip, separate modulators for external drive have been integrated as a 398 reference for the characterization of the monolithic modulators, which are internally driven by the MUX. These modulators have not been connected to the underlying BiCMOS circuit, but equipped with contact pads to be 399 400 externally driven via an RF probe. The passive characteristics were almost identical to the aforementioned integrated 401 devices. Total insertion losses (IL) of 25 dB and an extinction ratio of 30 dB were measured. For the data modulation 402 experiment, see Extended Data Fig. 5, the on-chip electronics has been turned off to measure the modulator performance at ideal room temperature. A 100 GBd electrical signal is generated using random bit sequence 403 404 generator and an external DAC (MICRAM DAC4). The signal is then amplified and applied to the modulator via an RF 405 probe. A tuneable external cavity laser source (9 dBm maximum output power, 100 kHz linewidth) generates the 406 optical carrier at 1550.6 nm. The power of the laser can be adapted to power levels between 3 and 16 dBm by means 407 of an amplifier. A subsequent band-pass filter (0.6 nm,  $IL \le 0.7 dB$ ) suppresses the amplifier noise. This way, the 408 modulator's performance can be tested for a large dynamic range of input powers. The plasmonic modulator converts 409 the electrical signal onto the optical carrier before the data is transmitted over a back-to-back optical fiber link. At 410 the receiver, the modulated signal is amplified to 10 dBm, band-pass filtered (2 nm,  $L \le 0.7$  dB) and received in a direct detection scheme (70 GHz photodiode with 0.6 A/W responsivity, 63 GHz real-time oscilloscope with 411 412 160 GS/s). In-house offline DSP is applied for signal recovery and equalization. 100 Gb/s NRZ were transmitted with a BER below 10<sup>-5</sup> and an SNR of 16.44 dB. 413

#### 418 8.8 Monolithic Transmitter Data Modulation Experiment

419 In this section, more details on the monolithic transmitter data experiment is given.

The monolithic transmitter has been tested in a data modulation experiment. To evaluate the BER, five million samples of the modulated signal are captured using 63 GHz real-time oscilloscope with 160 GS/s. Offline DSP has been used for signal recovery and equalization. For the latter, a linear equalization with 101 filter taps and nonlinear mapping with pattern length of 7 have been applied as required for high-speed data modulation and compensation of nonlinearities in the complete communication system. Note that the first few filter taps show the most significant improvement<sup>42</sup>.

For the silicon-plasmonic MZM, data experiments with 50, 100 and 120 GBd were performed at a wavelength of 1551.7 nm with chip input powers of 8, 11 and 11 dBm, respectively. This corresponds to power ranges of 1.5 to 4.5 dBm into the modulator on the chip, -10.5 to -7.5 dBm at the modulator output and -17 to -14 dBm in the optical fiber at the output. 50 GBd were modulated with a BER of  $1.93 \cdot 10^{-5}$  (SNR of 13.14 dB) below the KP4 FEC limit of  $2 \cdot 10^{-4}$  <sup>54</sup>. 100 and 120 GBd were modulated with a BER of  $9.21 \cdot 10^{-3}$  (SNR of 8.14 dB) and  $1.74 \cdot 10^{-2}$  (SNR of 7.20 dB), respectively. Both BERs are below the SD-FEC limit of  $4 \cdot 10^{-2}$  <sup>52</sup>.

For the ultra-compact plasmonic modulator, 50 and 100 GBd data modulation was tested using an optical carrier at a wavelength of 1559 nm with 5 and 9 dBm chip input power. The corresponding powers are -1.5 and 2.5 dBm at the modulator input, -15.5 and -11.5 dBm at the modulator output, and -22 and -18 dBm in the fiber at the output. 50 GBd were modulated with a BER of  $1.36 \cdot 10^{-3}$  (SNR of 10.14 dB) below the hard-decision FEC limit of  $3.8 \cdot 10^{-3}$  <sup>55</sup> and 100 GBd with a BER of  $3.95 \cdot 10^{-2}$  (SNR of 5.48 dB) below the SD-FEC limit.

# 437 Data Availability Statement

The data that support the plots within this paper and other findings of this study are available from the corresponding author upon reasonable request.

### 440 References

Thraskias, C. A. *et al.* Survey of Photonic and Plasmonic Interconnect Technologies for Intra-Datacenter and

High-Performance Computing Communications. *IEEE Communications Surveys & Tutorials* 20, 2758-2783,

(2018).

- Winzer, P. J. & Neilson, D. T. From Scaling Disparities to Integrated Parallelism: A Decathlon for a Decade. *Journal of Lightwave Technology* **35**, 1099-1115, (2017).

- Alexoudi, T. *et al.* Optics in Computing: From Photonic Network-on-Chip to Chip-to-Chip Interconnects and

Disintegrated Architectures. *Journal of Lightwave Technology* **37**, 363-379, (2019).

- 448 4 Kanakis, G. *et al.* High-Speed VCSEL-Based Transceiver for 200 GbE Short-Reach Intra-Datacenter Optical 449 Interconnects. *Appl. Sci.* **9**, 2488, (2019).

- Szilagyi, L., Khafaji, M., Pliva, J., Henker, R. & Ellinger, F. 40-Gbit/s 850-nm VCSEL-Based Full-CMOS Optical

Link With Power-Data Rate Adaptivity. *IEEE Photonics Technology Letters* **30**, 611-613, (2018).

- Hu, S. *et al.* A 50Gb/s PAM-4 Retimer-CDR plus VCSEL Driver with Asymmetric Pulsed Pre-Emphasis Integrated

into a Single CMOS Die. *2019 Optical Fiber Communications Conference and Exhibition (OFC)*, (2019).

- Ledentsov, N. *et al.* Energy efficient 850-nm VCSEL based optical transmitter and receiver link capable of 56

Gbit/s NRZ operation. *Vertical-Cavity Surface-Emitting Lasers XXIII*, San Francisco, USA, 10938-18, (2019).

- Wang, C. *et al.* Integrated lithium niobate electro-optic modulators operating at CMOS-compatible voltages.

*Nature* 562, 101-+, (2018).

- He, M. B. *et al.* High-performance hybrid silicon and lithium niobate Mach-Zehnder modulators for 100 Gbit

s(-1) and beyond. *Nature Photon.* 13, 359-+, (2019).

- 10 Nagarajan, R. *et al.* InP Photonic Integrated Circuits. *IEEE Journal of Selected Topics in Quantum Electronics*16, 1113-1125, (2010).

- 462 11 Katopodis, V. *et al.* Serial 100 Gb/s connectivity based on polymer photonics and InP-DHBT electronics. *Opt.* 463 *Express* 20, 28538-28543, (2012).

- 46412Ogiso, Y. et al. Over 67 GHz Bandwidth and 1.5 V Vπ InP-Based Optical IQ Modulator With n-i-p-n465Heterostructure. Journal of Lightwave Technology **35**, 1450-1455, (2016).

- 466 13 Ozolins, O. *et al.* 100 Gbaud 4PAM Link for High Speed Optical Interconnects. *43rd European Conference on* 467 *Optical Communication (ECOC 2017)*, (2017).

- 468 14 Going, R. *et al.* Multi-channel InP-based Coherent PICs with Hybrid Integrated SiGe Electronics Operating up

469 to 100 GBd, 32QAM. *2017 European Conference on Optical Communication (ECOC),* Gothenburg, Sweden,

470 Th.PDP.C.3, (2017).

- 471 15 Lange, S. *et al.* 100 GBd Intensity Modulation and Direct Detection With an InP-Based Monolithic DFB Laser

472 Mach-Zehnder Modulator. *Journal of Lightwave Technology* **36**, 97-102, (2018).

- 47316Estaran, J. M. et al. 140/180/204-Gbaud OOK Transceiver for Inter- and Intra-Data Center Connectivity.474Journal of Lightwave Technology 37, 178-187, (2019).

- 47517Nakamura, M. et al. 192-Gbaud Signal Generation Using Ultra-Broadband Optical Frontend Module476Integrated with Bandwidth Multiplexing Function. 2019 Optical Fiber Communications Conference and477Exhibition (OFC), San Diego, USA, Th4B.4, (2019).

- 47818Zhang, J. et al. Demonstration of 260-Gb/s Single-Lane EML-Based PS-PAM-8 IM/DD for Datacenter479Interconnects. 2019 Optical Fiber Communications Conference and Exhibition (OFC), W4I.4, (2019).

- Leuthold, J. *et al.* Silicon-Organic Hybrid Electro-Optical Devices. *IEEE Journal of Selected Topics in Quantum Electronics* 19, (2013).

- 48220Rakowski, M. et al. Low-Power, Low-Penalty, Flip-Chip Integrated, 10Gb/s Ring-Based 1V CMOS Photonics483Transmitter. 2013 Optical Fiber Communication Conference and Exposition and the National Fiber Optic484Engineers Conference (OFC/NFOEC), (2013).

- Yashiki, K. *et al.* 25-Gbps error-free operation of chip-scale Si-photonics optical transmitter over 70 degrees

C with integrated quantum dot laser. *2016 Optical Fiber Communications Conference and Exhibition (OFC)*,

(2016).

- Verbist, J. *et al.* Real-Time 100 Gb/s NRZ and EDB Transmission With a GeSi Electroabsorption Modulator for

Short-Reach Optical Interconnects. *Journal of Lightwave Technology* **36**, 90-96, (2017).

- Wolf, S. *et al.* Coherent modulation up to 100 GBd 16QAM using silicon-organic hybrid (SOH) devices. *Opt. Express* 26, 220-232, (2018).

- 492 24 Sun, J. *et al.* A 128 Gb/s PAM4 Silicon Microring Modulator with Integrated Thermo-optic Resonance Tuning.

493 *Journal of Lightwave Technology*, 1-1, (2018).

- Li, H. et al. A 112 Gb/s PAM4 Transmitter with Silicon Photonics Microring Modulator and CMOS Driver. 2019

Optical Fiber Communications Conference and Exhibition (OFC), San Diego, USA, Th4A.4, (2019).

- Emboras, A. *et al.* Electrically Controlled Plasmonic Switches and Modulators. *IEEE Journal of Selected Topics in Quantum Electronics* 21, 276-283, (2015).

- 498 27 Hoessbacher, C. *et al.* Plasmonic modulator with > 170 GHz bandwidth demonstrated at 100 GBd NRZ. *Opt.* 499 *Express* 25, 1762-1768, (2017).

- 500 28 Messner, A. *et al.* Plasmonic Ferroelectric Modulators. *Journal of Lightwave Technology*, 1-1, (2018).

- 50129Heni, W. et al. Ultra-High-Speed 2:1 Digital Selector and Plasmonic Modulator IM/DD Transmitter Operating502at 222 GBaud for Intra-Datacenter Applications. Journal of Lightwave Technology, (2020).

- 50330Settaluri, K. T. *et al.* Demonstration of an Optical Chip-to-Chip Link in a 3D Integrated Electronic-Photonic504Platform. *Proc Eur Solid-State*, (2015).

- Vlasov, Y. A. Silicon CMOS-Integrated Nano-Photonics for Computer and Data Communications Beyond 100G.

*IEEE Commun Mag* 50, S67-S72, (2012).

- 50732Gill, D. M. et al. Demonstration of Error-Free 32-Gb/s Operation From Monolithic CMOS Nanophotonic508Transmitters. IEEE Photonics Technology Letters 28, 1410-1413, (2016).

- 50933Atabaki, A. H. *et al.* Integrating photonics with silicon nanoelectronics for the next generation of systems on510a chip. *Nature* **556**, 349-354, (2018).

- 511 34 Stojanovic, V. *et al.* Monolithic silicon-photonic platforms in state-of-the-art CMOS SOI processes. *Opt.* 512 *Express* **26**, 13106-13121, (2018).

- 513 35 Weeber, J. C. *et al.* Characterization of CMOS metal based dielectric loaded surface plasmon waveguides at 514 telecom wavelengths. *Opt. Express* **25**, 394-408, (2017).

- 51536Burla, M. et al. 500 GHz plasmonic Mach-Zehnder modulator enabling sub-THz microwave photonics. APL516Photonics 4, 056106, (2019).

- 517 37 Ayata, M. *et al.* High-speed plasmonic modulator in a single metal layer. *Science* **358**, 630-632, (2017).

- 51838Koch, U. et al. MONOLITHIC HIGH-SPEED TRANSMITTER ENABLED BY BICMOS-PLASMONIC PLATFORM. 2019519European Conference on Optical Communication (ECOC), Dublin, Ireland, PD.1.4, (2019).

- Möller, M. *et al.* SiGe retiming high-gain power MUX for directly driving an EAM up to 50 Gbit/s. *Electron Lett*34, 1782-1784, (1998).

- 52240Koch, U. *et al.* Ultra-Compact Terabit Plasmonic Modulator Array. Journal of Lightwave Technology **37**, 1484-5231491, (2019).

- Heni, W. *et al.* Plasmonic IQ modulators with attojoule per bit electrical energy consumption. *Nat. Commun.* **10**, (2019).

- 52642Baeuerle, B. *et al.* 120 GBd plasmonic Mach-Zehnder modulator with a novel differential electrode design527operated at a peak-to-peak drive voltage of 178 mV. *Opt. Express* 27, 16823-16832, (2019).

- Heni, W. *et al.* 108 Gbit/s Plasmonic Mach-Zehnder Modulator with >70 GHz Electrical Bandwidth. *Lightwave Technology, Journal of* PP, 1-1, (2015).

- Heni, W. *et al.* Nonlinearities of organic electro-optic materials in nanoscale slots and implications for the optimum modulator design. *Opt. Express* **25**, 2627-2653, (2017).

- 53245Xu, H. *et al.* Ultrahigh Electro-Optic Coefficients, High Index of Refraction, and Long-Term Stability from Diels-533Alder Cross-Linkable Binary Molecular Glasses. *Chem Mater* **32**, 1408-1421, (2020).

- 534 46 Uhl, C., Hettrich, H. & Möller, M. A 100 Gbit/s 2 Vpp Power Multiplexer in SiGe BiCMOS Technology for

535 Directly Driving a Monolithically Integrated Plasmonic MZM in a Silicon Photonics Transmitter. *IEEE Bipol*536 *Bicmos*, 106-109, (2017).

- 537 47 Uhl, C., Hettrich, H. & Möller, M. Design Considerations for a 100 Gbit/s SiGe-BiCMOS Power Multiplexer With

538 2 V-pp Differential Voltage Swing. *IEEE J Solid-St Circ* 53, 2479-2487, (2018).

- 53948Uhl, C., Hettrich, H. & Möller, M. 180 Gbit/s 4:1 power multiplexer for NRZ-OOK signals with high output540voltage swing in SiGe BiCMOS technology. *Electron Lett*, (2019).

- 49 Möller, M. Challenges in the cell-based design of very-high-speed SiGe-bipolar ICs at 100 Gb/s. *IEEE J Solid-St* 542 *Circ* 43, 1877-1888, (2008).

- 543 50 Melikyan, A. *et al.* High-speed plasmonic phase modulators. *Nature Photon.* **8**, 229-233, (2014).

- 54 51 Essiambre, R. J., Kramer, G., Winzer, P. J., Foschini, G. J. & Goebel, B. Capacity Limits of Optical Fiber Networks. 545 *Journal of Lightwave Technology* **28**, 662-701, (2010).

- 545 52 Schuh, K. *et al.* Single Carrier 1.2 Tbit/s Transmission over 300 km with PM-64 QAM at 100 GBaud. *2017* 547 *Optical Fiber Communications Conference and Exposition (OFC),* Los Angeles, USA, Th5B.5, (2017).

- 53 Carroll, L. *et al.* Photonic Packaging: Transforming Silicon Photonic Integrated Circuits into Photonic Devices.

549 *Appl. Sci.* 6, (2016).

- 54 El-Fiky, E. *et al.* First demonstration of a 400 Gb/s 4 lambda CWDM TOSA for datacenter optical interconnects.

551 *Opt. Express* 26, 19742-19749, (2018).

- 552 55 *ITU-T Recommendation G.975.1* International Telecommunications Union, Geneva, Switzerland, 2004.

- 553

# 554 Acknowledgements

- 555 The work was in part funded by the EU-projects PLASMOfab (688166) and plaCMOS (980997), and the Air

- 556 Force Office of Scientific Research (FA9550-19-1-0069). This work was in parts carried out at the Binnig and Rohrer

- 557 Nanotechnology Center.

# 558 Author Contributions

- 559 U.K., C.H. and J.L. designed the plasmonic platform. C.U., H.H. and M.M. designed the BiCMOS electronic

- 560 platform. U.K., C.U., H.H. and Y.F. developed the monolithic integration process. C.H., W.H. and M.A. contributed to

- the design and testing of the monolithic modulator. W.H., B.B., B.I.B. and A.J. contributed to the data modulation

- 562 experiment. H.X., D.L.E. and L.R.D developed the temperature-stable organic material. E.M. and B.P. contributed to

- the design process. L.Z., S.L. and A.K. coordinated the wafer fabrication process. D.T., N.K. M.M. and J.L. designed and

- 564 coordinated the project. All authors contributed to drafting of the manuscript.

# 565 Competing Interest

566 C.H., W.H., B.B. are involved in activities toward commercializing high-speed plasmonic modulators at 567 Polariton Technologies Ltd. The other authors declare no competing interests.