# Ge2Sb2Te5 p-type thin-film transistors on flexible plastic foil

#### **Journal Article**

#### Author(s):

Daus, Alwin; Han, Songyi; Knobelspies, Stefan; Cantarella, Giuseppe; Tröster, Gerhard 🕞

#### **Publication date:**

2018-09

#### Permanent link:

https://doi.org/10.3929/ethz-b-000357129

#### Rights / license:

Creative Commons Attribution 4.0 International

# Originally published in:

Materials 11(9), https://doi.org/10.3390/ma11091672

Article

# Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> p-Type Thin-Film Transistors on Flexible Plastic Foil

Alwin Daus \*, Songyi Han, Stefan Knobelspies, Giuseppe Cantarella and Gerhard Tröster

Electronics Laboratory, Department of Information Technology and Electrical Engineering, 8092 Zürich, Switzerland; songyi.han@polytechnique.edu (S.H.); kstefan@ife.ee.ethz.ch (S.K.); gcantare@ife.ee.ethz.ch (G.C.); troester@ife.ee.ethz.ch (G.T.)

\* Correspondence: daus.alwin@gmail.com or dausa@ife.ee.ethz.ch; Tel.: +41-44-632-68-70

Received: 27 July 2018; Accepted: 7 September 2018; Published: 9 September 2018

Abstract: In this work, we show the performance improvement of p-type thin-film transistors (TFTs) with Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) semiconductor layers on flexible polyimide substrates, achieved by downscaling of the GST thickness. Prior works on GST TFTs have typically shown poor current modulation capabilities with ON/OFF ratios ≤20 and non-saturating output characteristics. By reducing the GST thickness to 5 nm, we achieve ON/OFF ratios up to ≈300 and a channel pinch-off leading to drain current saturation. We compare the GST TFTs in their amorphous (as deposited) state and in their crystalline (annealed at 200 °C) state. The highest effective field-effect mobility of 6.7 cm²/Vs is achieved for 10-nm-thick crystalline GST TFTs, which have an ON/OFF ratio of ≈16. The highest effective field-effect mobility in amorphous GST TFTs is 0.04 cm²/Vs, which is obtained in devices with a GST thickness of 5 nm. The devices remain fully operational upon bending to a radius of 6 mm. Furthermore, we find that the TFTs with amorphous channels are more sensitive to bias stress than the ones with crystallized channels. These results show that GST semiconductors are compatible with flexible electronics technology, where high-performance p-type TFTs are strongly needed for the realization of hybrid complementary metal-oxide-semiconductor (CMOS) technology in conjunction with popular n-type oxide semiconductor materials.

**Keywords:** GST; thin-film transistor; flexible electronics; P-type semiconductor; crystalline materials; amorphous materials; phase-change materials; germanium; antimony; tellurium

#### 1. Introduction

Flexible electronics have received increased attention in the last years, promising great innovations in emerging display technology [1], healthcare [2–4], human-machine interfaces [4,5], textiles [6] and flexible sensor systems for Internet-of-Things (IoT) applications [7]. Especially, the latter requires high-frequency operation (13.56 MHz) to enable wireless data transmission via radio frequency identification (RFID) and near-field communication (NFC). Oxide semiconductor based thin-film transistors (TFTs) offer large carrier mobilities (>10 cm²/Vs), which enable these high frequencies, and additionally provide low off-currents and large area uniformity [8–11]. Thus, recent reports have shown that unipolar circuit technology based on oxide semiconductors can be employed for NFC and RFID applications [12,13]. However, the use of complementary metal-oxide-semiconductor (CMOS) technology could dramatically improve the power consumption, gain, noise immunity and circuit design of these systems [14].

Recently, several groups of materials have been studied to realize flexible hybrid CMOS together with n-type oxide semiconductors involving p-type SnO [14] or carbon nanotubes [15–18]. So far only few works have considered GeSbTe (GST) compounds as channel materials for TFTs [19–25], despite their p-type semiconducting properties [26,27], potentially large hole mobilities between

Materials 2018, 11, 1672 2 of 10

10–100 cm²/Vs [27,28], as well as low-temperature processability. Notably, the material has been extensively studied for phase-change memory applications [29] and is commercially applied in rewritable optical discs [30]. Prior works on GST TFTs have found difficulties in the ON/OFF current modulation and the output characteristics did not show saturating drain currents ( $I_D$ ) [19–25]. In this work, we study GST TFTs on a flexible substrate and demonstrate performance improvements through downscaling of the GST thickness to 5 nm. For this GST thickness, we find ON/OFF ratios up to ≈300, which represents a 15-fold improvement compared to prior work. The thickness reduction also leads to a pinch-off of the semiconductor channel, resulting in a saturating  $I_D$  in TFT output characteristics. Furthermore, we compare the device characteristics before and after thermal annealing above the crystallization temperature, which leads to an increased conductivity and mobility for GST thin-films ≥10 nm.

### 2. Experimental

# 2.1. Device Fabrication

The bottom gate TFTs were processed on a flexible 50  $\mu$ m thick polyimide substrate. First, the substrate was cleaned in isopropanol and acetone by sonication, followed by a baking at 200 °C in an air oven for 24 h. Then, a SiN<sub>X</sub> buffer layer was applied on both sides of the substrate by plasma-enhanced chemical vapor deposition at 150 °C. The Ti/Au/Ti (5/30/5 nm) gate electrode was deposited by electron-beam evaporation and structured by lift-off. The surface was cleaned by 1 min of ultraviolet (UV) ozone treatment and subsequently a 20-nm-thick Al<sub>2</sub>O<sub>3</sub> gate dielectric was deposited by thermal atomic-layer deposition at 150 °C. The amorphous GST p-type semiconductor layer was direct-current (dc) magnetron sputtered from a Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> target at room temperature (see reference [31]) and structured by lift-off. To avoid damage to the Al<sub>2</sub>O<sub>3</sub>, this lift-off was executed using Poly(methyl methacrylate) (PMMA) photoresist and deep-ultraviolet lithography. Afterwards, via holes were wet chemically etched into Al<sub>2</sub>O<sub>3</sub>. Finally, the Ge/Ni/Au (5/5/30 nm) source/drain electrodes were electron-beam evaporated and patterned by lift-off. The post-fabrication crystallization was performed in a vacuum oven at a pressure p = 200 mbar and 200 °C for 1 h.

## 2.2. Material Characterization

The *x*-ray diffraction (XRD) measurements of the GST thin-films were performed with a D2 Phaser 2nd Gen, Bruker, Billerica, MA, USA (30 kV, 10 mA, wavelength  $\lambda$  = 0.154 nm).

The Hall measurements were done on a Nanometrics HL5500 Hall System at ambient temperature at a magnetic field of 0.32 Tesla. The GST thin-films had Ge/Ni/Au (5/5/30 nm) contacts and were simultaneously fabricated with the TFTs. The current for 10 nm, 20 nm and 50-nm-thick crystallized GST films was set to 0.01 mA, 0.5 mA and 1 mA, respectively. The amorphous films were too resistive to perform Hall measurements.

#### 2.3. Thin-Film Transistor Characterization

All electrical measurements were performed on a probe station (Rucker Kolls, Inc., Milpitas, CA, USA) at ambient conditions with a B1500A semiconductor device analyzer (Agilent Technologies, Santa Clara, CA, USA). Bias stress was applied on the TFTs with a constant gate-source voltage  $V_{GS} = -5 \text{ V}$  and a constant drain-source voltage  $V_{DS} = -100 \text{ mV}$ , immediately followed by a double-sweep measurement of the transfer characteristic.

#### 3. Results and Discussion

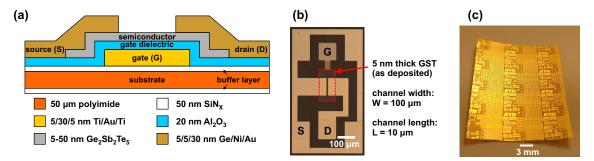

The GST TFTs have been fabricated on a free-standing flexible  $50~\mu m$  thick polyimide foil as described above. Here, different GST thicknesses between 5~and~50~nm are studied. A schematic cross-section of the TFTs is shown in Figure 1a. A micrograph of a fully fabricated TFT with 5-nm-thick GST (as deposited) is displayed in Figure 1b. Figure 1c shows a photograph of the flexible polyimide

Materials 2018, 11, 1672 3 of 10

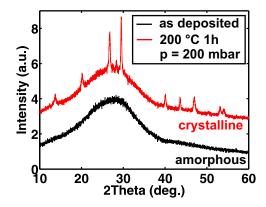

substrate after the device fabrication. The device performance is tested in the amorphous (as deposited) state and after annealing at 200 °C in a vacuum oven. To confirm the phase-change of GST upon annealing, we performed XRD measurements. Figure 2 reveals a mixed face-centered cubic (fcc) and hexagonal close-packed (hcp) crystal structure of GST after annealing [32,33].

**Figure 1.** Thin-film transistors (TFTs) on flexible plastic substrates. (a) Schematic TFT cross-section. (b) Optical micrograph of a TFT top view. (c) Photograph of fully fabricated devices on 50  $\mu$ m thick polyimide.

Figure 2. X-ray diffraction of 100-nm-thick GST on quartz glass.

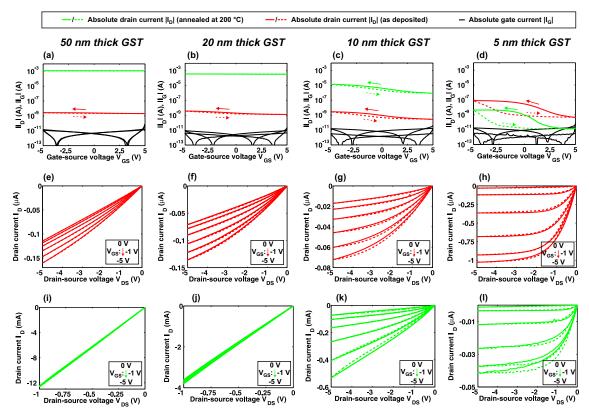

In Figure 3, the electrical characteristics of 5–50-nm-thick GST TFTs are compared. All TFTs display the expected p-type behavior with increasing  $|I_D|$  for negative  $V_{GS}$ . The transfer characteristics of 50 nm and 20-nm-thick GST TFTs show the desired  $|I_D|$  increase upon annealing, however, nearly all  $I_D$  modulation capabilities are lost (see Figure 3a,b). With decreasing GST thickness, the  $I_D$  ON/OFF modulation is improved (Figure 3a-d). Furthermore, the significantly increased  $|I_D|$  at  $V_{GS} = -5$  V for 5-nm-thick amorphous GST TFTs (≈20x compared to thicker amorphous layers) leads to the largest ON/OFF ratio of  $\approx$ 300 at this GST thickness. The annealing of these ultra-thin GST films results in an  $|I_D|$  decrease, which can be attributed to a degradation of the channel and contact area as discussed later. The output characteristics of amorphous GST TFTs (Figure 3e-h) show an increasingly saturating behavior for reduced GST thicknesses. The strongly saturated characteristics for 5-nm-thick amorphous GST TFTs indicate that the channel pinch-off is successfully obtained. After annealing, the thick GST films  $\geq$ 20 nm are highly conductive and the TFTs show ohmic behavior with large  $|I_D|$  (Figure 3i,j). We found that large  $V_{DS}$  lead to a breakdown of the these devices and thus the maximum  $V_{DS}$  was set to 1 V. Nevertheless, the TFTs with GST thicknesses  $\leq$ 10 nm after annealing can sustain larger  $V_{DS}$ (Figure 3k,l). A fully saturating I<sub>D</sub> was only obtained for 5-nm-thick annealed GST semiconductor layers, which is similar to the findings in the as deposited state.

Materials **2018**, 11, 1672 4 of 10

Figure 3. Electrical characteristics of GST thin-film transistors (TFTs) with channel lengths of 10  $\mu$ m and a channel widths of 100  $\mu$ m. Transfer characteristics at a drain-source voltage  $V_{DS}$ = -100 mV for (a) 50 nm, (b) 20 nm, (c) 10 nm and (d) 5-nm-thick GST. Output characteristics of amorphous (as deposited) GST TFTs for (e) 50 nm, (f) 20 nm, (g) 10 nm and (h) 5-nm-thick GST. Output characteristics of annealed GST TFTs for (i) 50 nm, (j) 20 nm, (k) 10 nm and (l) 5-nm-thick GST.

In Table 1, the threshold voltages  $(V_{Th})$  and subthreshold swings (SS) of the devices are presented. Both measures monotonously rise with increasing GST thickness. It has to be noted that due to the low ON/OFF ratio, which is further evaluated below, the values for TFTs with 50-nm-thick amorphous (as deposited) GST channels are impractical. For the same reason, no  $V_{Th}$  or SS could be extracted for TFTs with GST thicknesses  $\geq 20$  nm after annealing.

**Table 1.** Threshold voltages ( $V_{Th}$ ) and subthreshold swings (SS) of the GST TFTs extracted at a drain-source voltage  $V_{DS}$ = -100 mV.

| GST Thickness<br>(nm) | V <sub>Th</sub> (V)<br>as Deposited | $V_{Th}$ (V)<br>Annealed at 200 $^{\circ}$ C | SS (V/Decade)<br>as Deposited | SS (V/Decade)<br>Annealed at 200 °C |

|-----------------------|-------------------------------------|----------------------------------------------|-------------------------------|-------------------------------------|

| 5                     | 0.86                                | 0.6                                          | 1.3                           | 1.0                                 |

| 10                    | 1.8                                 | 1.72                                         | 5.4                           | 5.1                                 |

| 20                    | 4.56                                | -                                            | 13                            | -                                   |

| 50                    | 20.55                               | <del>-</del>                                 | 22                            | -                                   |

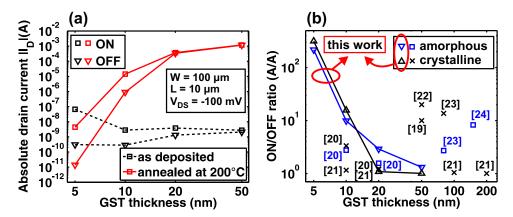

In Figure 4a, we compare the TFT ON-currents ( $|I_{D,ON}|$  at  $V_{GS}$ = -5 V) and OFF-currents ( $|I_{D,OFF}|$  at  $V_{GS}$ = +5 V) for different GST thicknesses. For amorphous (as deposited) GST, the  $|I_{D,OFF}|$  can be reduced when scaling the thickness to  $\leq 10$  nm and the  $|I_{D,ON}|$  exhibits an increase between 10 nm and 5 nm of GST. As shown in Table 2, the effective field-effect mobilities  $\mu_{FE,eff}$  agree with these trends and have values in the expected range [27,34,35]. The annealing provides the desired  $|I_{D}|$  increase only down to 10 nm of GST below which the post-annealing  $|I_{D}|$  deteriorates. The  $\mu_{FE,eff}$  values for 20 and 50 nm of annealed GST cannot be extracted due to the low ON/OFF ratio, and for

Materials 2018, 11, 1672 5 of 10

10-nm-thick GST TFTs we obtain  $\mu_{\rm FE,eff}$  = 6.7 cm<sup>2</sup>/Vs. Further, we performed Hall measurements on the crystallized GST films (see Table 2). The amorphous films were too resistive for the Hall measurements. We obtained Hall mobilities around  $\approx 3 \text{ cm}^2/\text{Vs}$  and carrier concentrations in the order of 10<sup>20</sup> cm<sup>-3</sup>, which is in agreement with prior findings for fcc-GST [34,35]. Figure 4b displays the ON/OFF ratio for different GST thicknesses with a literature comparison. Other works have so far not investigated GST TFTs with active layer thicknesses below 10 nm. In contrast to prior work, we find a clear trend indicating an increasing ON/OFF ratio with reduced GST film thickness. Our maximum ON/OFF ratio of 316 for 5-nm-thick annealed GST results in a ≈15-fold improvement compared to prior reports. The strong thickness dependence of the ON/OFF ratio and the significant improvement for ultra-thin GST layers can be attributed to the electronic energetics of GST in both the amorphous and crystalline phases. For both situations, the gate electric field has a limited penetration depth into the GST layer. For the amorphous phase, GST exhibits a large number of acceptor-like and donor-like traps, which compensate each other leading to strong Fermi-level pinning in the middle of the band gap [36–38]. Additionally, there are Te lone-pairs, which could also be responsible for the observed hysteresis in the transfer characteristics (Figure 3a-d) [36,37]. In the crystalline phase, mainly acceptor-type vacancy defects are present [36,37], which results in strong p-type doping and a Fermi-level shift into the valence band forming a degenerate semiconductor [35,38]. In this case, the depletion width for the gate electric field is strongly limited [39] and a fully-depleted TFT can only be achieved for ultra-thin semiconductor layers. Thus, the OFF-current of GST TFTs is a strong function of GST thickness and can be reduced with thinner GST layers. In the following, the dependence of the ON-current on the GST thickness is discussed.

**Figure 4.** Comparison of the ON-currents and OFF-currents for different GST thicknesses. (a) ON- and OFF-currents. (b) ON/OFF ratio with a comparison to literature using [19–24].

**Table 2.** Effective field-effect mobility  $\mu_{\text{FE,eff}}$  (cm<sup>2</sup>/Vs) for TFTs with different GST thicknesses extracted in the linear regime and Hall mobilities  $\mu_{\text{Hall}}$  (cm<sup>2</sup>/Vs) and carrier concentrations n (cm<sup>-3</sup>) measured in GST thin-films.

| GST Thickness<br>(nm) | $\mu_{	ext{FE,eff}}$ as Deposited | $\mu_{\rm FE,eff}$<br>Annealed at 200 $^{\circ}$ C | $\mu_{ m Hall}$ Annealed at 200 $^{\circ}$ C | n<br>Annealed at 200 °C |

|-----------------------|-----------------------------------|----------------------------------------------------|----------------------------------------------|-------------------------|

| 5                     | 0.041                             | 0.0032                                             | -                                            | -                       |

| 10                    | 0.0014                            | 6.72                                               | 2.79                                         | $+9.6 \times 10^{19}$   |

| 20                    | 0.0013                            | -                                                  | 3.7                                          | $+4.1 \times 10^{20}$   |

| 50                    | 0.0004                            | -                                                  | 2.92                                         | $+7.2 \times 10^{20}$   |

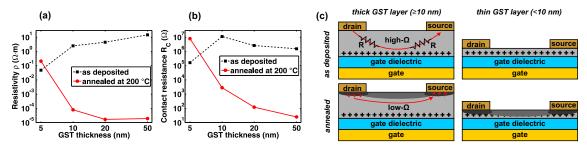

For that, we analyze TFTs with different channel lengths between 7  $\mu$ m and 100  $\mu$ m to extract the resistivity  $\rho$  (Figure 5a) and contact resistance  $R_C$  (Figure 5b). For the amorphous case, we find that the  $\rho$  and  $R_C$  are strongly reduced for 5-nm-thick GST compared to thicker layers. This can be attributed to a parasitic resistance of the highly resistive GST film [40,41], due to the limited

Materials 2018, 11, 1672 6 of 10

penetration depth of the gate electric field forming a very thin conductive accumulation region (see Figure 5c, top-left) [42,43]. Thus, the ON-current in TFTs with amorphous GST channels can be improved by thickness downscaling due to a reduction of the parasitic series resistances. In contrast, the annealed GST thin-film exhibits a significant decrease in  $\rho$  and  $R_C$  for GST thicknesses  $\geq 10$  nm, which is related to the large conductivity of the crystalline phase. We attribute the unsuccessful reduction of  $\rho$  and  $R_C$  upon annealing for 5-nm-thick GST to a degradation of the contact and surface area, which could be caused by an oxidation during annealing and migration effects in the source/drain contact area. We believe that these effects should certainly have an increased impact for thinner GST channels as indicated in dark gray in Figure 5c (bottom). To confirm that the device oxidation is responsible for the degradation of  $\rho$ , future work should address different annealing parameters and environment such as higher vacuum level or nitrogen atmosphere.

**Figure 5.** Influence of GST thickness and annealing on resistivity and contact resistance. (a) Resistivity  $\rho$ . (b) Contact resistance  $R_C$ . (c) Sketch visualizing the proposed mechanisms.

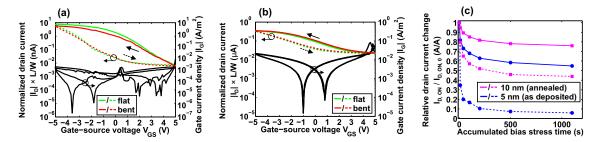

From the above described measurements and analysis, we conclude that among the amorphous (as deposited) and crystallized (annealed) devices the TFTs with 5-nm-thick GST and 10-nm-thick GST show the highest performance, respectively. Thus, we performed bending tests with these devices by wrapping the polyimide substrates around a metallic rod with a radius R = 6 mm. Figure 6a, b show the results of the bending tests for TFTs with 5-nm-thick amorphous GST channels and 10-nm-thick crystallized GST channels, respectively. Both devices remain fully operational during the bending experiments. The former (a) shows a reduction of  $|I_{D,ON}|$  and  $\mu_{FE,eff}$  [44] while the latter (b) remains almost unaltered with a small  $|I_{D,ON}|$  increase. From prior findings, we know that, typically, devices on 50 µm thick polyimide sustain bending to R = 5-6 mm without any significant alterations in their characteristics [45–47]. However, the here observed  $|I_{D,ON}|$  reduction by  $\approx 25$  % for TFTs with 5-nm-thick amorphous GST channels indicates that not the bending, but the preceding electrical characterization may have caused this change. Thus, we investigated the changes in |I<sub>D,ON</sub>| upon bias stress measurements (see Figure 6c). After a cumulative bias stress time of 1100 s, the TFT with a 5-nm-thick amorphous GST channel has an  $|I_{D,ON}|$ , which is reduced to less than 10 % of its initial value, which is then partially recovered to about 60 % after a sweep to positive V<sub>GS</sub>. In contrast, the changes for the TFT with a 10-nm-thick crystallized GST channel are significantly smaller. A reason for the strong bias stress dependence of the TFTs with amorphous channels could be intrinsic defects such as Te lone-pairs [36,37], which we also attributed to the observed hysteresis in the transfer characteristics. These defects are not expected to be present in the crystalline phase of GST. Consequently, we see less bias stress dependence in the crystallized films. However, due to the mixed crystalline phase of GST (see Figure 2) after annealing, there could still be Te lone-pairs present e.g., at grain boundaries. An additional effect, which needs to be taken into account, is the known resistance drift over time in amorphous GST, which could also partially cause the |I<sub>D,ON</sub>| reduction [48,49].

Materials 2018, 11, 1672 7 of 10

**Figure 6.** Bending and bias stress measurements. (a) Transfer characteristic of a TFT with a 5-nm-thick amorphous (as deposited) GST channel under bending (radius R = 6 mm). (b) Transfer characteristic of a TFT with a 10-nm-thick crystallized (annealed) GST channel under bending (radius R = 6 mm). (c) ON-current  $I_{D,ON}$  change upon bias stress. The dashed lines represent  $I_{D,ON}$  directly after bias stress and the solid lines correspond to  $I_{D,ON}$  after a sweep to positive  $V_{GS}$ .

#### 4. Conclusions and Outlook

We have reported a significant performance improvement for GST TFTs by lowering the semiconductor thickness down to 5 nm. The ON/OFF-ratio was improved by a factor of  $\approx\!15$  and saturating output characteristics were obtained. Although a  $\mu_{\rm FE,eff}$  of 6.7 cm²/Vs for 10-nm-thick crystalline GST TFTs was observed, the abovementioned performance improvements could only be achieved at a GST thickness of 5 nm, where the maximum  $\mu_{\rm FE,eff}$  was found to be 0.04 cm²/Vs. This work shows that GST is a promising p-semiconductor for flexible electronics. Thus, we recently demonstrated the integration of such TFTs with n-type InGaZnO4 to form flexible CMOS circuits [44]. Therein, we showed a bending stability of these circuits to a tensile radius of 6 mm.

However, several aspects still need to be addressed in the future. The crystallization process for 5-nm-thick GST films needs improvement, which could be achieved by changing the crystallization temperature, atmosphere and time, and by applying appropriate passivation layers to GST prior to the crystallization. In addition, different source/drain contact materials could be studied to investigate their impact on  $R_C$  before and after annealing. Furthermore, other material compositions could be investigated. The electronic properties of crystalline GST could be altered by increasing the Ge content, which could reduce the number of Ge vacancies responsible for the p-type doping [50]. The resulting reduction of free carriers could then increase the minimum GST thickness required for the improved TFT performance, and thus the crystallization process could be simplified. Furthermore, a significant increase of the Sb content has resulted in reduced resistivities in the amorphous phase of GST [51], which could be a path for improvements of TFTs with amorphous GST channels.

**Author Contributions:** A.D. conceived the experiments and did the material characterization. A.D. and S.H. did the device fabrication, electrical characterization and analyzed the results. G.T. supervised the work. All authors reviewed and commented on the manuscript.

Funding: The work was funded by the Swiss National Science Foundation (SNSF) grant No. 2000021\_149495/1.

**Acknowledgments:** We would like to express our gratitude to S. Danzi and R. Spolenak for allowing the usage of the GST sputter target.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Niu, Y.F.; Liu, S.F.; Chiou, J.Y.; Huang, C.Y.; Chiu, Y.W.; Lai, M.H.; Liu, Y.W. Improving the flexibility of AMOLED display through modulating thickness of layer stack structure. *J. Soc. Inf. Disp.* **2016**, 24, 293–298. [CrossRef]

- 2. Takei, K. High performance, flexible CMOS circuits and sensors toward wearable healthcare applications. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 6.1.1–6.1.4.

Materials 2018, 11, 1672 8 of 10

3. Sekitani, T.; Someya, T. Human-friendly organic integrated circuits. *Mater. Today* **2011**, *14*, 398–407. [CrossRef]

- 4. Kim, D.H.; Lu, N.; Ma, R.; Kim, Y.S.; Kim, R.H.; Wang, S.; Wu, J.; Won, S.M.; Tao, H.; Islam, A.; et al. Epidermal electronics. *Science* **2011**, *333*, 838–843. [CrossRef] [PubMed]

- 5. Bauer, S. Flexible electronics: Sophisticated skin. Nat. Mater. 2013, 12, 871–872. [CrossRef] [PubMed]

- 6. Cherenack, K.; Zysset, C.; Kinkeldei, T.; Münzenrieder, N.; Tröster, G. Woven electronic fibers with sensing and display functions for smart textiles. *Adv. Mater.* **2010**, 22, 5178–5182. [CrossRef] [PubMed]

- 7. Heremans, P.; Papadopoulos, N.; de Jamblinne de Meux, A.; Nag, M.; Steudel, S.; Rockele, M.; Gelinck, G.; Tripathi, A.; Genoe, J.; Myny, K. Flexible metal-oxide thin film transistor circuits for RFID and health patches. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 6.3.1–6.3.4.

- 8. Petti, L.; Münzenrieder, N.; Vogt, C.; Faber, H.; Büthe, L.; Cantarella, G.; Bottacchi, F.; Anthopoulos, T.D.; Tröster, G. Metal oxide semiconductor thin-film transistors for flexible electronics. *Appl. Phys. Rev.* **2016**, 3, 021303. [CrossRef]

- 9. Gupta, V.O. A survey on stunning IGZO technology. Int. J. Appl. Inf. Syst. 2013, 2249, 0868.

- 10. Nathan, A.; Ahnood, A.; Cole, M.T.; Lee, S.; Suzuki, Y.; Hiralal, P.; Bonaccorso, F.; Hasan, T.; Garcia-Gancedo, L.; Dyadyusha, A.; et al. Flexible electronics: the next ubiquitous platform. *Proc. IEEE* **2012**, 100, 1486–1517. [CrossRef]

- 11. Münzenrieder, N.; Petti, L.; Zysset, C.; Kinkeldei, T.; Salvatore, G.A.; Tröster, G. Flexible self-aligned amorphous InGaZnO thin-film transistors with submicrometer channel length and a transit frequency of 135 MHz. *IEEE Trans. Electron Devices* **2013**, *60*, 2815–2820. [CrossRef]

- 12. Yang, B.D.; Oh, J.M.; Kang, H.J.; Park, S.H.; Hwang, C.S.; Ryu, M.K.; Pi, J.E. A Transparent Logic Circuit for RFID Tag in a-IGZO TFT Technology. *ETRI J.* **2013**, *35*, 610–616. [CrossRef]

- 13. Myny, K.; Tripathi, A.K.; van der Steen, J.L.; Cobb, B. Flexible thin-film NFC tags. *IEEE Commun. Mag.* **2015**, 53, 182–189. [CrossRef]

- 14. Li, Y.S.; He, J.C.; Hsu, S.M.; Lee, C.C.; Su, D.Y.; Tsai, F.Y.; Cheng, I.C. Flexible complementary oxide–semiconductor-based circuits employing n-channel ZnO and p-channel SnO thin-film transistors. *IEEE Electron Devices Lett.* **2016**, *37*, 46–49. [CrossRef]

- 15. Honda, W.; Arie, T.; Akita, S.; Takei, K. Bendable CMOS Digital and Analog Circuits Monolithically Integrated with a Temperature Sensor. *Adv. Mater. Technol.* **2016**, *1*. [CrossRef]

- 16. Petti, L.; Bottacchi, F.; Münzenrieder, N.; Faber, H.; Cantarella, G.; Vogt, C.; Büthe, L.; Namal, I.; Späth, F.; Hertel, T.; et al. Integration of solution-processed (7, 5) SWCNTs with sputtered and spray-coated metal oxides for flexible complementary inverters. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 26.4.1–26.4.4.

- 17. Chen, H.; Cao, Y.; Zhang, J.; Zhou, C. Large-scale complementary macroelectronics using hybrid integration of carbon nanotubes and IGZO thin-film transistors. *Nat. Commun.* **2014**, *5*, 4097. [CrossRef] [PubMed]

- 18. Petti, L.; Loghin, F.; Cantarella, G.; Vogt, C.; Münzenrieder, N.; Abdellah, A.; Becherer, M.; Haeberle, T.; Daus, A.; Salvatore, G.; et al. Gain-tunable complementary common-source amplifier based on a flexible hybrid thin-film transistor technology. *IEEE Electron Device Lett.* **2017**, *38*, 1536–1539. [CrossRef]

- 19. Hosaka, S.; Miyauchi, K.; Tamura, T.; Sone, H.; Koyanagi, H. Proposal for a memory transistor using phase-change and nanosize effects. *Microelectron. Eng.* **2004**, *73*, *736–740*. [CrossRef]

- 20. Yin, Y.; Miyachi, A.; Niida, D.; Sone, H.; Hosaka, S. Electrical properties of phase change and channel current control in ultrathin phase-change channel transistor memory by annealing. *Jpn. J. Appl. Phys.* **2006**, *45*, 3238. [CrossRef]

- 21. Yin, Y.; Miyachi, A.; Niida, D.; Sone, H.; Hosaka, S. Thickness Dependences of Phase Change and Channel Current Control in Phase-Change Channel Transistor. In Proceedings of the 2005 IEEE Conference on Electron Devices and Solid-State Circuits, Hong Kong, China, 19–21 December 2005; pp. 617–620.

- 22. Hosaka, S.; Miyauchi, K.; Tamura, T.; Yin, Y.; Sone, H. Prototype of phase-change channel transistor for both nonvolatile memory and current control. *IEEE Trans. Electron Devices* **2007**, *54*, 517–523. [CrossRef]

- 23. Liao, F.; Ding, Y.; Lin, Y.; Tang, T.; Qiao, B.; Lai, Y.; Feng, J.; Chen, B. Characterization of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> thin film transistor and its application in non-volatile memory. *Microelectron. J.* **2006**, *37*, 841–844. [CrossRef]

- 24. Cai, Y.; Zhou, P.; Tang, T.; Gao, C.; Lin, Y. Multi-Bit Storage Based on Chalcogenide Thin Film Transistor for High Density Nonvolatile Memory Application. *Integr. Ferroelectr.* **2009**, *110*, 34–42. [CrossRef]

Materials 2018, 11, 1672 9 of 10

25. Song, K.B.; Lee, S.S.; Kim, K.A.; Suh, J.D.; Kim, J.H.; Lee, T.S.; Cheong, B.K.; Kim, W.M. Undoped homojunction chalcogen thin-film transistors on glass. *Appl. Phys. Lett.* **2007**, *90*, 263510. [CrossRef]

- 26. Song, K.B.; Sohn, S.W.; Kim, J.; Kim, K.A.; Cho, K. Chalcogenide thin-film transistors using oxygenated n-type and p-type phase change materials. *Appl. Phys. Lett.* **2008**, *93*, 043514. [CrossRef]

- 27. Kato, T.; Tanaka, K. Electronic properties of amorphous and crystalline Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> films. *Jpn. J. Appl. Phys.* **2005**, *44*, 7340. [CrossRef]

- 28. Yanez-Limon, J.; González-Hernández, J.; Alvarado-Gil, J.; Delgadillo, I.; Vargas, H. Thermal and electrical properties of the Ge: Sb: Te system by photoacoustic and Hall measurements. *Phys. Rev. B* **1995**, 52, 16321. [CrossRef]

- 29. Wong, H.S.P.; Raoux, S.; Kim, S.; Liang, J.; Reifenberg, J.P.; Rajendran, B.; Asheghi, M.; Goodson, K.E. Phase change memory. *Proc. IEEE* **2010**, *98*, 2201–2227. [CrossRef]

- 30. Kolobov, A.V.; Fons, P.; Frenkel, A.I.; Ankudinov, A.L.; Tominaga, J.; Uruga, T. Understanding the phase-change mechanism of rewritable optical media. *Nat. Mater.* **2004**, *3*, 703–708. [CrossRef] [PubMed]

- 31. Schlich, F.F.; Wyss, A.; Galinski, H.; Spolenak, R. Cohesive and adhesive properties of ultrathin amorphous and crystalline Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> films on polyimide substrates. *Acta Mater.* **2017**, 126, 264–271. [CrossRef]

- 32. Ting, Z.; Bo, L.; Ji-Lin, X.; Zhi-Tang, S.; Song-Lin, F.; Bomy, C. Structure and electrical properties of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> thin film used for ovonic unified memory. *Chin. Phys. Lett.* **2004**, *21*, 741. [CrossRef]

- 33. Zhang, Z.; Pan, J.; Fang, L.W.W.; Yeo, Y.C.; Foo, Y.L.; Zhao, R.; Shi, L.; Tok, E.S. Temperature-dependent phase separation during annealing of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> thin films in vacuum. *Appl. Surf. Sci.* **2012**, 258, 6075–6079. [CrossRef]

- 34. Baily, S.; Emin, D.; Li, H. Hall mobility of amorphous Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>. *Solid State Commun.* **2006**, 139, 161–164. [CrossRef]

- 35. Lee, B.S.; Abelson, J.R.; Bishop, S.G.; Kang, D.H.; Cheong, B.K.; Kim, K.B. Investigation of the optical and electronic properties of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> phase change material in its amorphous, cubic, and hexagonal phases. *J. Appl. Phys.* **2005**, *97*, 093509. [CrossRef]

- 36. Pirovano, A.; Lacaita, A.L.; Benvenuti, A.; Pellizzer, F.; Bez, R. Electronic switching in phase-change memories. *IEEE Trans. Electron Devices* **2004**, *51*, 452–459. [CrossRef]

- 37. Pirovano, A.; Lacaita, A.L.; Pellizzer, F.; Kostylev, S.A.; Benvenuti, A.; Bez, R. Low-field amorphous state resistance and threshold voltage drift in chalcogenide materials. *IEEE Trans. Electron Devices* **2004**, 51, 714–719. [CrossRef]

- 38. Huang, B.; Robertson, J. Defect models and electrical storage mechanism in GeSbTe phase change materials. *J. Non-Cryst. Solids* **2012**, *358*, 2393–2397. [CrossRef]

- 39. Jeong, J.; Hong, Y. Debye length and active layer thickness-dependent performance variations of amorphous oxide-based TFTs. *IEEE Trans. Electron Devices* **2012**, *59*, 710–714. [CrossRef]

- 40. Martin, S.; Chiang, C.S.; Nahm, J.Y.; Li, T.; Kanicki, J.; Ugai, Y. Influence of the amorphous silicon thickness on top gate thin-film transistor electrical performances. *Jpn. J. Appl. Phys.* **2001**, *40*, 530. [CrossRef]

- 41. Li, Y.; Pei, Y.; Hu, R.; Chen, Z.; Zhao, Y.; Shen, Z.; Fan, B.; Liang, J.; Wang, G. Effect of channel thickness on electrical performance of amorphous IGZO thin-film transistor with atomic layer deposited alumina oxide dielectric. *Curr. Appl. Phys.* **2014**, *14*, 941–945. [CrossRef]

- 42. Lee, J.; Kim, K.; Kim, J.H.; Im, S.; Jung, D.Y. Optimum channel thickness in pentacene-based thin-film transistors. *Appl. Phys. Lett.* **2003**, *82*, 4169–4171. [CrossRef]

- 43. Das, S.; Chen, H.Y.; Penumatcha, A.V.; Appenzeller, J. High performance multilayer MoS<sub>2</sub> transistors with scandium contacts. *Nano Lett.* **2012**, *13*, 100–105. [CrossRef] [PubMed]

- 44. Daus, A.; Han, S.; Knobelspies, S.; Cantarella, G.; Vogt, C.; Münzenrieder, N.; Tröster, G. Flexible CMOS electronics based on p-type Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> and n-type InGaZnO<sub>4</sub> semiconductors. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 8.1.1–8.1.4.

Materials **2018**, 11, 1672

45. Daus, A.; Roldán-Carmona, C.; Domanski, K.; Knobelspies, S.; Cantarella, G.; Vogt, C.; Grätzel, M.; Nazeeruddin, M.K.; Tröster, G. Metal-Halide Perovskites for Gate Dielectrics in Field-Effect Transistors and Photodetectors Enabled by PMMA Lift-Off Process. *Adv. Mater.* 2018, *30*, 1707412. [CrossRef] [PubMed]

- 46. Zysset, C.; Münzenrieder, N.; Petti, L.; Büthe, L.; Salvatore, G.A.; Tröster, G. IGZO TFT-based all-enhancement operational amplifier bent to a radius of 5 mm. *IEEE Electron Device Lett.* **2013**, *34*, 1394–1396. [CrossRef]

- 47. Münzenrieder, N.; Zysset, C.; Petti, L.; Kinkeldei, T.; Salvatore, G.A.; Tröster, G. Flexible double gate a-IGZO TFT fabricated on free standing polyimide foil. *Solid State Electron.* **2013**, *84*, 198–204. [CrossRef]

- 48. Braga, S.; Cabrini, A.; Torelli, G. Dependence of resistance drift on the amorphous cap size in phase change memory arrays. *Appl. Phys. Lett.* **2009**, *94*, 092112. [CrossRef]

- 49. Ielmini, D.; Lavizzari, S.; Sharma, D.; Lacaita, A.L. Physical interpretation, modeling and impact on phase change memory (PCM) reliability of resistance drift due to chalcogenide structural relaxation. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 939–942.

- 50. Caravati, S.; Bernasconi, M.; Kühne, T.; Krack, M.; Parrinello, M. First-principles study of crystalline and amorphous Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> and the effects of stoichiometric defects. *J. Phys. Condens. Matter* **2009**, *21*, 255501. [CrossRef] [PubMed]

- 51. Choi, K.J.; Yoon, S.M.; Lee, N.Y.; Lee, S.Y.; Park, Y.S.; Yu, B.G.; Ryu, S.O. The effect of antimony-doping on Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>, a phase change material. *Thin Solid Films* **2008**, *516*, 8810–8812. [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).