## Three-Phase PFC Rectifier and High-Voltage Generator for X-Ray Systems

A thesis submitted to attain the degree of

#### DOCTOR OF SCIENCES of ETH ZURICH (Dr. sc. ETH Zurich)

presented by MICHAEL LEIBL

MSc ETH born on 5.5.1986 citizen of Austria

accepted on the recommendation of

Prof. Dr. Johann W. Kolar, examiner Prof. Dr. Hans-Peter Nee, co-examiner

ETH Zurich Power Electronic Systems Laboratory Physikstrasse 3 | ETL H23 8092 Zurich | Switzerland

$\rm http://www.pes.ee.ethz.ch$

@ 2017 by Michael Leibl

Printed in Switzerland

# Acknowledgments

**F**<sup>IRST I</sup> want to thank Prof. Dr. Johann W. Kolar for encouraging me to start a PhD at the Power Electronic Systems Laboratory (PES) in the first place. His inspiring attitude alone, which I knew from his lectures, contributed a great deal to the following work, not to mention all those valuable discussions after 6 pm, his meticulous attention to details in manuscripts, the links to the sought-after publications and his never ending deep interest to discuss new concepts and ideas.

I also want to thank Prof. Dr. Hans-Peter Nee for taking the time to travel to Zurich and attend my defense as a co-examiner and for his effort on commenting this thesis.

Furthermore, I would like to thank Siemens Healthcare GmbH for funding the project and in particular Dr. Josef Deuringer, who in weekly telephone discussions provided valuable inputs concerning the X-ray system surrounding the high-voltage generator.

Also I want to thank all members of PES for creating the inspiring and motivating atmosphere I enjoyed here. In particular I want to thank Gabriel Ortiz for getting me started as well as Christoph Gammeter, Lukas Schrittwieser, David Boillat and Jon Azurza Anderson for enduring endless white-board discussions in the afternoons. Also I am very grateful for the discussions about electromagnetic problems with Thomas Guillod, for the introduction to wireless power transfer by Oliver Knecht and for all the discussions and the good time that I enjoyed with the rest of the team.

I want to thank Monica Kohn, Roswitha Coccia, Prisca Maurantonio, Yvonne Schnyder-Lieberherr and Damaris Egger for managing all the time consuming administrative work that conference publications, industry relations, teaching tasks and patent applications bring along. Also I want to express my gratitude to Peter Albrecht and Peter Seitz for their assistance with assembling prototypes and ordering material and the team of the ITET workshop around Martin Vogt for manufacturing all the mechanical parts with great precision.

Finally, I want to thank my fiancée Mirjam for her support in particular before approaching dead-lines.

> Zurich, February 2018 Michael Leibl

## Abstract

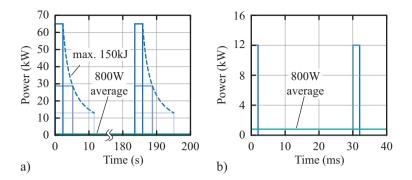

$\mathbf{M}$  EDICAL X-ray systems have been under steady development since the discovery of X-rays by Röngten in 1895. However, the principle of X-ray generation has remained the same. Electrons are accelerated within an evacuated tube by a high-voltage difference from the cathode towards the anode. X-rays are emitted when electrons hits the anode. However, most of the energy of the electrons is dissipated by the anode in form of heat. Therefore, an X-ray power supply needs to provide not only voltages up to 150 kV but also a peak power of up to 100 kW. Since the cooling capability of the vacuum tube is typically only in the range of 1 kW, the power supply has to deliver high peak but only low average power.

In the development of X-ray systems there are three major trends affecting the high-voltage generator. First, nowadays X-ray systems use passive three-phase rectifiers which limit the application with weak power grids, emit low-frequency current harmonics and usually require adaption transformers for use with different nominal mains voltages. It is desired to use an active rectifier instead in order to provide a wide input voltage range that allows world-wide use of the device without modifications to the hardware. Second, currently available high-voltage generators typically provide rise- and fall-times of the tube voltage in the range of 500 µs. In pulsed fluoroscopy applications short rise- and fall-times of the tube voltage would eliminate the need for the cathode control grid which is necessary to keep the patient dose at a minimum. In dual energy computer tomography shorter fall- and rise-times could replace nowadays systems using two X-ray tubes at two different voltage levels by a single tube which is alternating between two voltage levels. Finally, the additional features should be achieved in a cost effective manner in order to make the technology affordable for all patients.

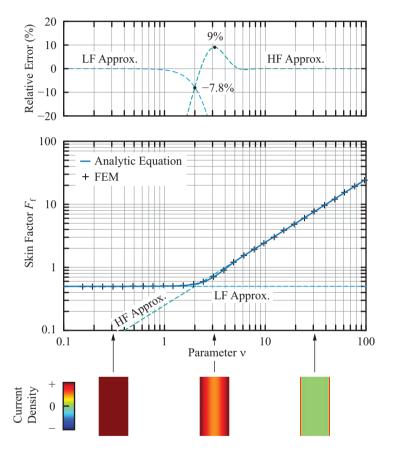

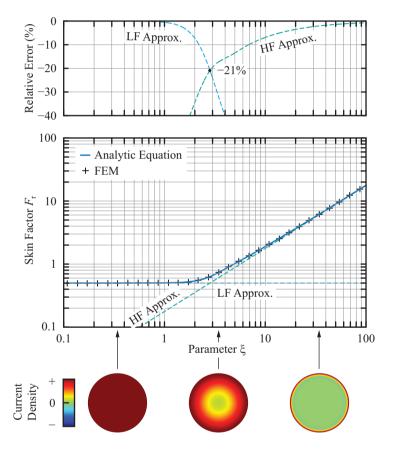

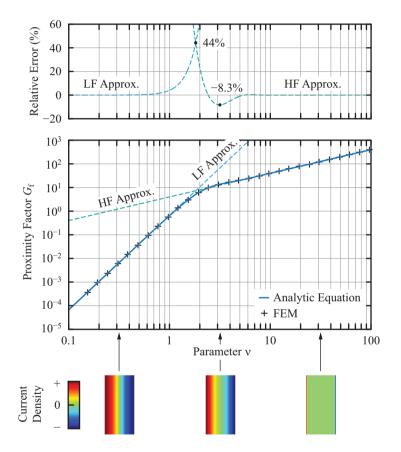

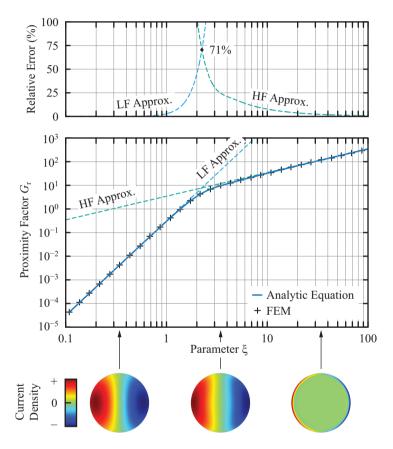

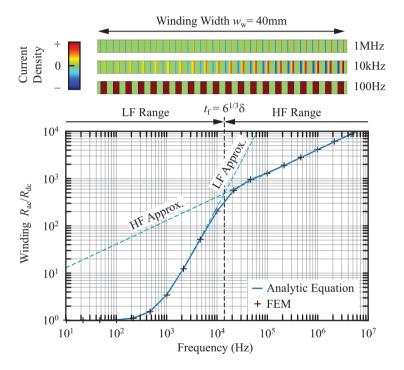

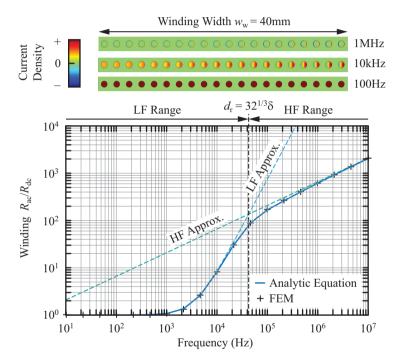

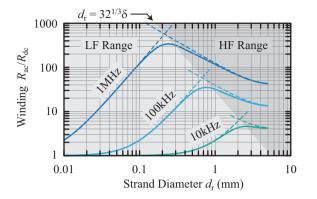

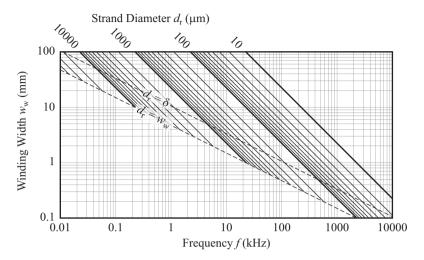

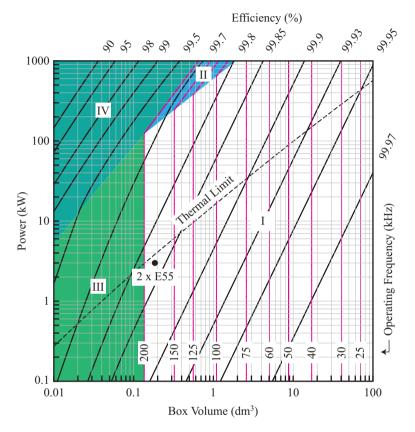

In order to achieve cost reductions the design of the inductive components is of particular importance. The high peak power but low average power of the application allows to reduce the volume and material cost of inductors and transformers substantially without exceeding the thermal limit. One basic element for the design of inductive components is the winding loss model which needs to take into account skin effect and proximity effect losses within the winding. An easy to use winding loss model is presented based on asymptotic approximations of the exact analytic equations for skin effect and proximity effect. Using appropriate asymptotic solutions for the low-frequency and for the high-frequency range, is usually sufficient. The error introduced by the approximations is only significant at the border between low-frequency and high-frequency range which is located approximately at the frequency where the conductor dimension equals twice the skin depth. It can be shown that windings with conductor dimensions close to this border should be avoided since they exhibit a higher AC resistance than windings with thicker or thinner conductors than twice the skin depth. Furthermore, the low-frequency asymptotic approximation allows to show that due to the proximity effect there is an optimum operating frequency of transformers which is inversely proportional to the conductor dimension and the winding width.

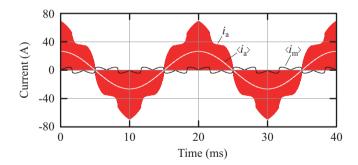

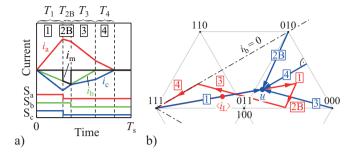

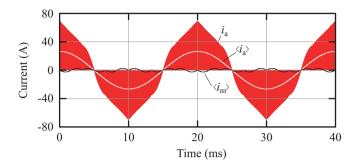

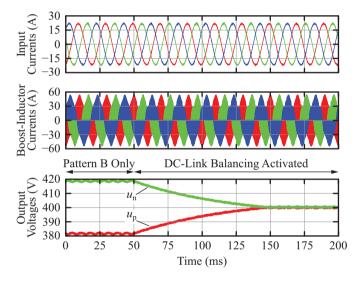

Based on the winding loss model an active three-phase rectifier is optimized for minimum total cost of ownership, which is the sum of material cost and loss energy cost. Due to the high peak-to-average load profile a high power density  $(9.56 \, \text{kW/dm}^3)$  and moderate efficiency (97.3%) design results. The prototype is designed for  $65 \,\mathrm{kW}$  nominal power and provides stabilized 800 V DC for the required input voltage range of 290 V-530 V line-to-line RMS. Due to their competitive price, silicon IGBTs provide a lower total cost of ownership for the considered application than silicon carbide MOSFETs while also providing high reliability and availability. The Vienna rectifier as a unidirectional system exhibits a discontinuous conduction mode which is usually entered only at very low power levels. Due to the high power density of the boost inductors a relatively high current ripple occurs and discontinuous conduction occurs already at 20% load. Since the duty cycle to voltage relationship is no longer linear in discontinuous conduction mode, high input current distortion is encountered with traditional closed-loop current controllers. Therefore, a special control scheme is presented that maintains sinusoidal input currents also with low load. The duty cycle values to obtain sinusoidal input currents can be directly expressed by analytic equations depending on the mains voltages, the DC-link voltage and the current set value. The control scheme is demonstrated on a 65 kW rectifier prototype.

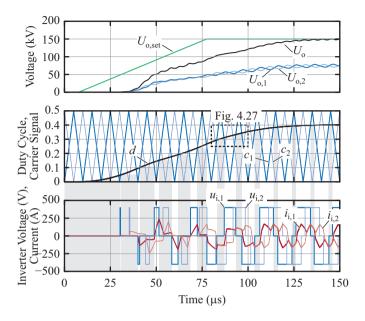

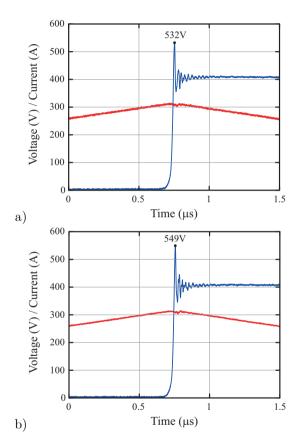

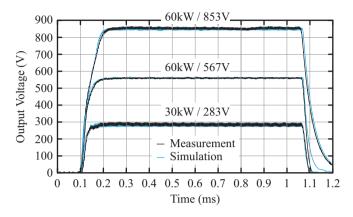

In order to reach a high tube voltage control bandwidth a nonresonant high-voltage generator topology is proposed. The topology extends a single active bridge converter using two coupled transformers which are feeding two series connected rectifier stages at the output. Compared to commonly used resonant converter solutions the proposed topology mainly provides the advantage of zero voltage switching with constant switching frequency and high output voltage control bandwidth. Compared to a conventional single active bridge, which also shares these advantages, the proposed topology additionally provides lower inverter RMS currents and a higher maximum output current. The concept is demonstrated on a 60 kW DC-DC converter prototype. With two interleaved inverters using silicon IGBTs operating at 50 kHz output voltage rise-times and fall-times of  $\approx 100 \,\mu s$ , i.e. five switching cycles, are achieved.

The conclusion of the thesis summarizes the main findings and contributions and provides an outlook on future research topics emanating mainly from the construction of the high-voltage transformer.

# Kurzfassung

${f S}$  EIT der Entdeckung der Röntgenstrahlen 1895 wurde der Funktionsumfang medizinischer Röntgengeräte ständig weiterentwickelt. Unverändert blieb jedoch das grundlegenden Prinzip der Röntgenstrahlerzeugung. In einer Vakuumröhre werden Elektronen durch eine hohe Beschleunigungsspannung von einer Kathode in die Anode geschleudert. Beim Auftreffen auf die Anode wird Röntgenstrahlung in Form von Bremsstrahlung ausgesendet. Ein Grossteil der Energie bleibt jedoch in Form von Wärme ungenutzt. Der Hochspannungserzeuger muss daher nicht nur eine Spannung von bis zu 150 kV sondern auch eine Spitzenleistung von bis zu 100 kW bereitstellen. Die Kühlleistung der Anode in der Vakuumröhre ist jedoch stark begrenzt sodass die durchschnittlich aufzubringende Leistung in der Grössenordung von 1 kW liegt.

Die Entwicklung des Hochspannungserzeugers bestimmen zur Zeit drei wesentliche Trends. Einerseits weisen heute übliche passive Diodengleichrichter relativ hohe Oberschwingungsströme auf, erlauben einen Einsatz mit verschiedenen Netzspannungen nur mit Hilfe von Anpasstransformatoren und sind mit weichen Netzen nicht kompatibel. Um einen weltweiten Einsatz des Geräts ohne Anpassungen gewährleisten zu können ist der Einsatz eines aktiven Pulsgleichrichters von grossem Interesse. Eine weitere Schwäche aktueller Hochspannungserzeuger sind die relativ langen Anstiegs- und Abfallzeiten der Röhrenspannung von etwa 500 us. Kürzere Anstiegs- und Abfallzeiten würden das bei Fluoroskopie heute übliche Steuergitter der Röhre überflüssig machen. Zudem könnten für Dual Energy Computer Tomographie Anwendungen eingesetzte, mit zwei verschiedenen Spannungen arbeitende Zweiröhrensysteme mit nur einer Röhre auskommen die schnell zwischen zwei Spannungsniveaus wechselt. Schlussendlich sollen die gewünschten Zusatzfunktionen kostengünstig umgesetzt werden um die Technologie allgemein zugänglich zu machen.

Besonders die Auslegung der induktiven Komponenten des Hochspannungsgenerators birgt grosses Einsparpotential. Durch die hohe Spitzen- aber niedrige Durchschnittsleistung können Baugrösse und Materialkosten stark reduziert werden ohne das thermische Limit zu überschreiten. Ein wichtiges Element für die Berechung induktiver Komponenten ist das Modell der Hochfrequenzwicklungsverluste. Basierend auf den exakten Gleichungen zur Bestimmung der Wirbelstromverluste in Wicklungen werden asymptotische Näherungen hergeleitet die sich durch einfache Anwendbarkeit auszeichnen. Es muss dabei zwischen zwei Näherungen für Nieder- und Hochfrequenzbereich unterschieden werden. Der maximale Fehler entsteht an der Bereichsgrenze welche etwa bei der Frequenz erreicht wird bei der die Abmessung eines Einzelleiters der doppelten Skintiefe entspricht. Es lässt sich jedoch zeigen, dass Leiterabmessungen der doppelten Skintiefe vermieden werden sollten, da der AC Widerstand der Wicklung sowohl für kleinere als auch für grössere Leiterabmessungen niedriger ist. Die asymptotische Näherung für den Niederfrequenzbereich erlaubt ausserdem die Herleitung der optimalen Betriebsfrequenz von Transformatoren welche indirekt proportional zum Produkt aus Einzelleiterabmessung und Wicklungsbreite ist.

Basierend auf dem Wicklungsverlustmodell wird ein Dreiphasenpulsgleichrichter für minimale Lebenszykluskosten, also der Summe von Betriebs- und Investitionskosten, optimiert. Aufgrund des hohen Verhältnisses von Spitzen- zu Durchschnittsleistung wird eine hohe Leistungsdichte von  $9.56 \,\mathrm{kW/dm^3}$  bei einem Wirkungsgrad von 97.3% erreicht. Der Prototyp weist eine Nennleistung von 65 kW auf und stellt eine konstante Ausgangsspannung von 800 V bei einem Eingangsspannungsbereich von 290 V - 530 V (Aussenleiterspannung effektiv) zur Verfügung. Für die gegebene Anwendung sind die Lebenszykluskosten bei Verwendung kostengünstiger Silizium IGBTs geringer als beim Einsatz von Siliziumkarbid MOSFETs. Ausserdem erweist sich die hohe Zuverlässigkeit und Verfügbarkeit als vorteilhaft. Unidirektionale Systeme wie der verwendete Vienna Rectifier weisen einen lückenden Betrieb auf welcher typisch nur bei sehr niedrigen Leistungen auftritt. Aufgrund der hohen Leistungsdichte ergibt sich jedoch ein relativ grosser Stromrippel in den Boost-Induktivitäten was dazu führt, dass der lückende Betrieb bis zu 20% der Nennleistung vorherrscht. Da im lückenden Betrieb der Zusammenhang zwischen Tastverhältnis und Brückenzweigspannung nicht mehr linear ist, entsteht bei Verwendung eines herkömmlichen Stromreglers eine relativ hohe Eingangsstromverzerrung. Es wird gezeigt dass durch Verwendung eines speziellen Steuerverfahrens auch im lückenden Betrieb sinusförmige Eingangsströme erreichbar sind. Die nötigen Tastverhältnisse lassen sich direkt aus den Phasenspannungen, der Zwischenkreisspannung und der geforderten Leistung berechnen. Das Steuerverfahren wird an einem 65 kW Prototyp gezeigt.

Um die geforderte Dynamik der Ausgangsspanungsregelung zu erreichen wird eine neuartige nicht-resonante Schaltungsstruktur des Hochspannungserzeugers verwendet. Die Schaltung verbessert die Eigenschaften des *Single Active Bridge* Konverters mittels zweier Transformatoren mit gekoppelten Wicklungssystemen und in Serie geschalteten Ausgangsgleichrichtern. Im Vergleich zu häufig eingesetzten Resonanzkonvertern bietet die vorgeschlagene Struktur die Vorteile weichen Schaltens bei konstanter Schaltfrequenz sowie höherer Bandbreite der Ausgangsspannungsregelung. Im Vergleich zum ursprünglichen *Single Active Bridge* Konverter ist dabei der Effektivwert des Wechselrichterstroms geringer und die, bei gegebener Baugrösse der Transformatoren, übertragbare Leistung höher. Das Konzept wird an einem 60 kW Prototyp demonstriert. Mit zwei phasenversetzt mit jeweils 50 kHz betriebenen Wechselrichtern können Anstiegs- und Abfallzeiten der Ausgangsspannung im Berich von  $\approx 100 \,\mu$ s, also der Dauer von fünf Schaltperioden, erreicht werden.

Abschliessend werden die wesentlichen Resultate und Beiträge der Arbeit zusammengefasst. Ausserdem werden weitere Forschungsthemen die sich vor allem aus der Konstruktion des Hochspannungstransformators ableiten diskutiert.

# Abbreviations

| AC                     | Alternating Current                                |

|------------------------|----------------------------------------------------|

| ADC                    | Analog to Digital Converter                        |

| AVG                    | Average                                            |

| $\mathbf{CCM}$         | Continuous Conduction Mode                         |

| CCM1                   | Continuous Conduction Mode 1                       |

| CCM2                   | Continuous Conduction Mode 2                       |

| CCM3                   | Continuous Conduction Mode 3                       |

| CISABC                 | Coupled Interleaved Single Active Bridge Converter |

| CISPR                  | Comité International Spécial des Perturbations     |

|                        | Radioélectriques                                   |

| $\mathbf{C}\mathbf{M}$ | Common Mode                                        |

| $\mathbf{CT}$          | Computer Tomography                                |

| DAB                    | Dual Active Bridge                                 |

| $\mathbf{DC}$          | Direct Current                                     |

| DCM                    | Discontinuous Conduction Mode                      |

| DCM1                   | Discontinuous Conduction Mode 1                    |

| DCM2                   | Discontinuous Conduction Mode 2                    |

| DCM3                   | Discontinuous Conduction Mode 3                    |

| DECT                   | Dual Energy CT                                     |

| DS-ADC                 | Delta-Sigma ADC                                    |

| DSP                    | Digital Signal Processor                           |

| $\mathbf{D}\mathbf{M}$ | Differential Mode                                  |

| DUT                    | Device Under Test                                  |

| EMI                    | Electro Magnetic Interference                      |

| $\mathbf{ESL}$         | Equivalent Series Inductance                       |

| $\mathbf{FFT}$         | Fast Fourier Transform                             |

| FEM                    | Finite Element Method                              |

| FOM                    | Figure Of Merit                                    |

| FPGA                   | Field Programmable Gate Array                      |

| GaN                    | Gallium Nitride                                    |

| GSE                    | Generalized Steinmetz Equation                     |

| HET                    | High Efficiency Transformer                        |

| HF                     | High-Frequency                                     |

| HVT                    | High-Voltage Transformer                           |

| IC2OC                  | Inverter Current RMS to DC Output Current          |

| IGBT                   | Insulated Gate Field Effect Transistor             |

| iGSE                   | Improved Generalized Steinmetz Equation            |

| IPOS                   | Input Parallel Output Series                       |

| TANDA          |                                                   |

|----------------|---------------------------------------------------|

| ISABC          | Interleaved Single Active Bridge Converter        |

| ISOS           | Input Series Output Series                        |

| $\mathbf{LF}$  | Low-Frequency                                     |

| LISN           | Line Impedance Stabilization Network              |

| MOSFET         | Metal Oxide Semiconductor Field Effect Transistor |

| NPC            | Neutral Point Clamped                             |

| OTC            | Optimum Trajectory Control                        |

| PCB            | Printed Circuit Board                             |

| PFC            | Power Factor Correction                           |

| РК             | Peak                                              |

| $\mathbf{PWM}$ | Pulse Width Modulation                            |

| $\mathbf{QP}$  | Quasi Peak                                        |

| $\mathbf{RMS}$ | Root Mean Square                                  |

| SABC           | Single Active Bridge Converter                    |

| $\mathbf{SiC}$ | Silicon Carbide                                   |

| SRC            | Series Resonant Converter                         |

| TCM            | Triangular Current Mode                           |

| TCO            | Total Cost of Ownership                           |

| THD            | Total Harmonic Distortion                         |

| $\mathbf{UPS}$ | Uninterruptible Power Supply                      |

| $\mathbf{VR}$  | Vienna Rectifier                                  |

| ZCS            | Zero Current Switching                            |

| ZMPC           | Zero Midpoint Current                             |

| $\mathbf{ZVS}$ | Zero Voltage Switching                            |

| PES            | Power Electronic Systems Laboratory               |

|                |                                                   |

# Contents

| $\mathbf{A}$ | bstra | $\mathbf{ct}$ |                                                                                                            | $\mathbf{v}$ |

|--------------|-------|---------------|------------------------------------------------------------------------------------------------------------|--------------|

| K            | urzfa | ssung         |                                                                                                            | ix           |

| $\mathbf{A}$ | bbre  | viation       | s                                                                                                          | xiii         |

| 1            | Intr  | oducti        | on                                                                                                         | 1            |

|              | 1.1   | X-Ray         | Generators                                                                                                 | 1            |

|              |       | 1.1.1         | X-Ray Tube                                                                                                 | 2            |

|              |       | 1.1.2         | High-Voltage Supply                                                                                        | 4            |

|              | 1.2   | Applic        | $ations \ldots \ldots$ | 5            |

|              | 1.3   | Recent        | t Developments                                                                                             | 6            |

|              | 1.4   | Object        | tive and Contributions                                                                                     | 6            |

|              |       | 1.4.1         | Three-Phase PFC Rectifier                                                                                  | 7            |

|              |       | 1.4.2         | High-Voltage Generator                                                                                     | 8            |

|              | 1.5   | List of       | Publications                                                                                               | 8            |

| <b>2</b>     | Opt   | imized        | l Design of Inductive Components                                                                           | 11           |

|              | 2.1   | High-I        | Frequency Winding Losses                                                                                   | 12           |

|              |       | 2.1.1         | Skin Effect                                                                                                | 13           |

|              |       | 2.1.2         | Proximity Effect                                                                                           | 22           |

|              |       | 2.1.3         | Winding of Foil or Round Conductors                                                                        | 29           |

|              | 2.2   | Core I        | Loss Model                                                                                                 | 39           |

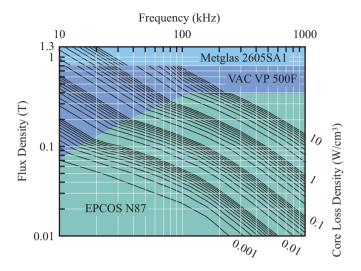

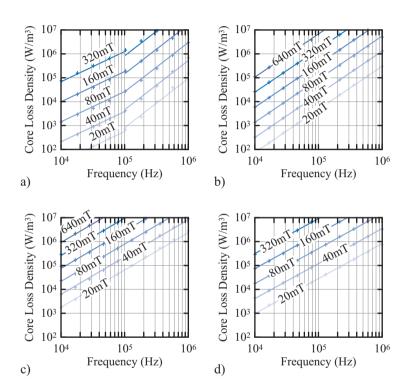

|              |       | 2.2.1         | Magnetic Materials                                                                                         | 40           |

|              |       | 2.2.2         | Sinusoidal Flux-Waveforms                                                                                  | 42           |

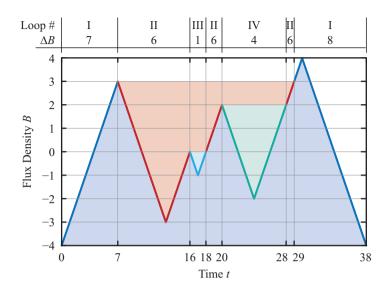

|              |       | 2.2.3         | Arbitrary Flux-Waveforms                                                                                   | 45           |

|              | 2.3   | Optim         | ized Transformer Design                                                                                    | 48           |

|              |       | 2.3.1         | Losses in a Transformer                                                                                    | 48           |

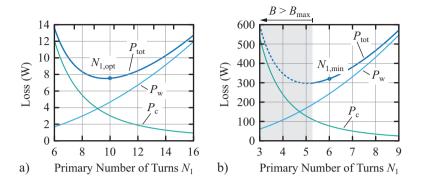

|              |       | 2.3.2         | Optimum Number of Turns                                                                                    | 49           |

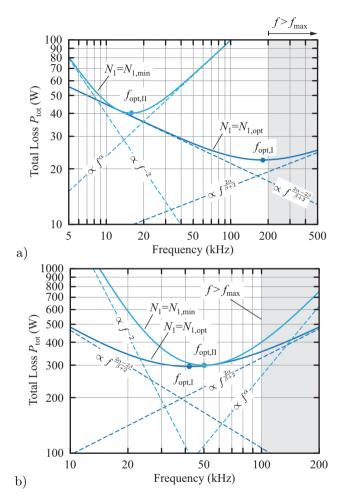

|              |       | 2.3.3         | Optimum Operating Frequency                                                                                | 51           |

|              |       | 2.3.4         | Transformer Scaling Laws                                                                                   | 55           |

|              | 2.4   | Optim         | ized Inductor Design                                                                                       | 59           |

|              |       | 2.4.1         | Losses in an Inductor $\ldots \ldots \ldots \ldots \ldots \ldots$                                          | 60           |

|              |       | 2.4.2         | Optimum Inductance and Number of Turns                                                                     | 60           |

|              |       | 2.4.3         | Total Cost of Ownership Optimization                                                                       | 63           |

|              | 2.5   | Summ          | ary of the Chapter                                                                                         | 65           |

| 3 | Vie |        | ectifier with High Peak-to-Average Load Ratio      | 67  |

|---|-----|--------|----------------------------------------------------|-----|

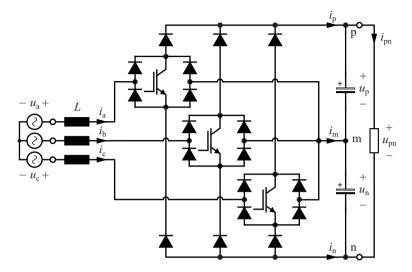

|   | 3.1 | Circui | it Variants                                        | 68  |

|   |     | 3.1.1  | Three-Switch Topology                              | 69  |

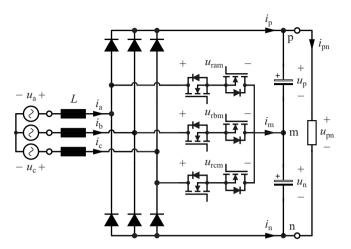

|   |     | 3.1.2  | T-Type Topology                                    | 70  |

|   |     | 3.1.3  | Neutral Point Clamped Topology                     | 70  |

|   | 3.2 | Contin | nuous Conduction Mode                              | 71  |

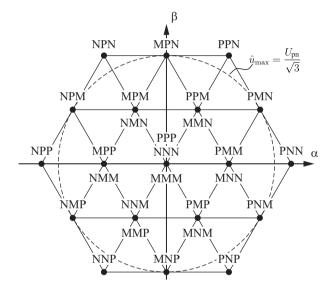

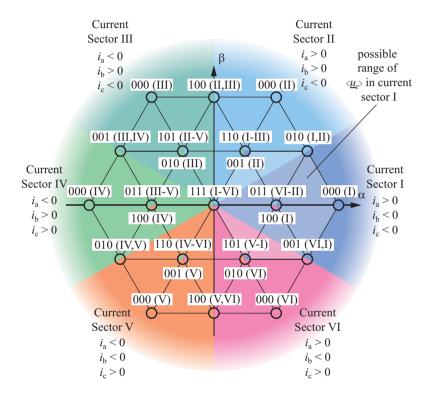

|   |     | 3.2.1  | Space Vector Diagram                               | 72  |

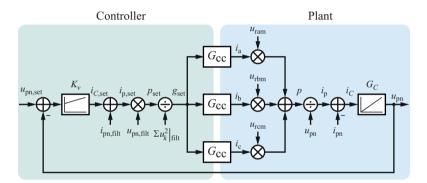

|   |     | 3.2.2  | Output Voltage Control                             | 76  |

|   |     | 3.2.3  | Input Current Control                              | 78  |

|   |     | 3.2.4  | DC-Link Balancing                                  | 80  |

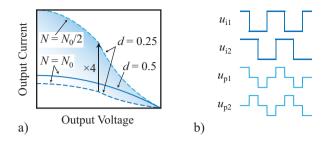

|   |     | 3.2.5  | Pulse Width Modulation                             | 87  |

|   | 3.3 | Discor | ntinuous Conduction Mode                           | 91  |

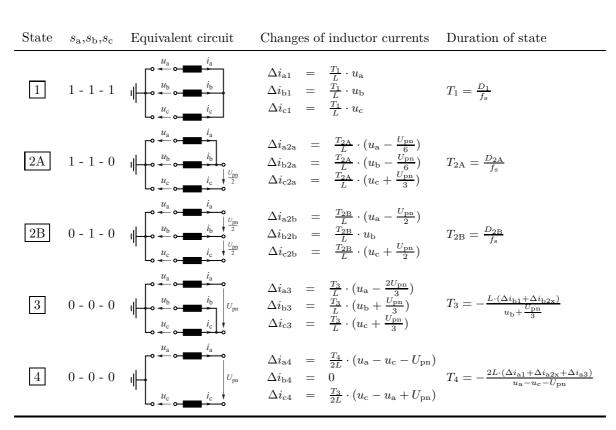

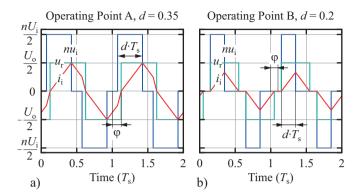

|   |     | 3.3.1  | Synchronous Switching DCM                          | 93  |

|   |     | 3.3.2  | Proposed Sinusoidal Current DCM Pattern A          | 94  |

|   |     | 3.3.3  | Proposed Sinusoidal Current DCM Pattern B          | 95  |

|   |     | 3.3.4  | Calculation of the Duty Cycles                     | 98  |

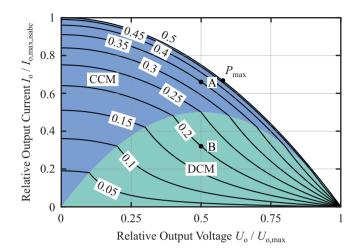

|   |     | 3.3.5  | DCM/CCM Threshold                                  | 100 |

|   |     | 3.3.6  | DC-Link Balancing & Midpoint Current Limit         | 104 |

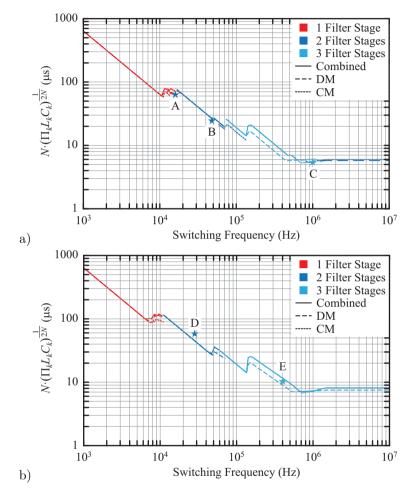

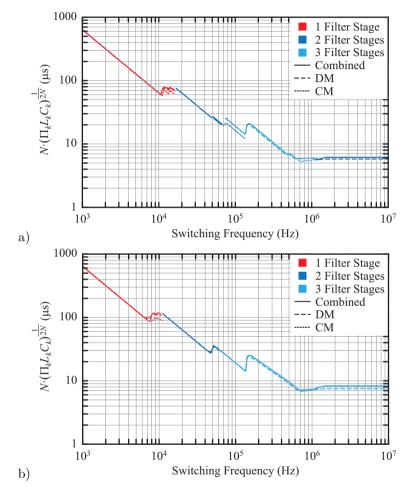

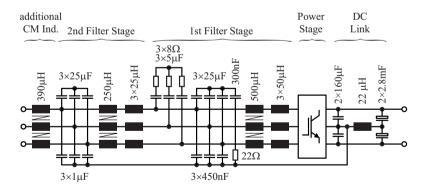

|   | 3.4 | Input  | Filter Dimensioning                                | 108 |

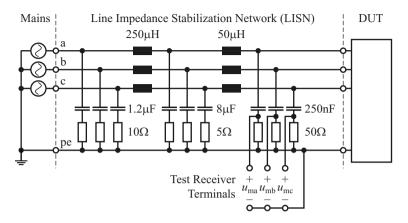

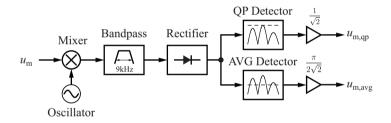

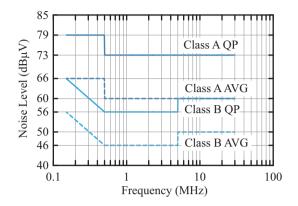

|   |     | 3.4.1  | Emission Regulations and Limits                    | 108 |

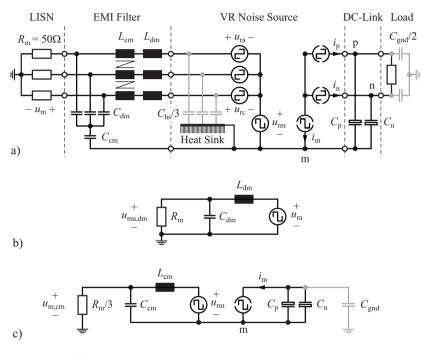

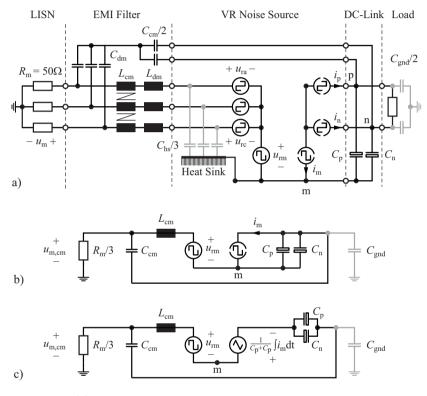

|   |     | 3.4.2  | Vienna Rectifier Noise Emission Model              | 110 |

|   |     | 3.4.3  | Vienna Rectifier Noise Emission Spectrum           | 113 |

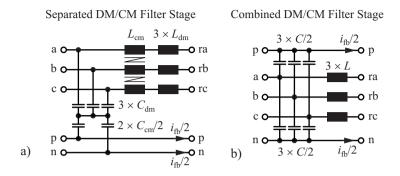

|   |     | 3.4.4  | Filter Design Procedure                            | 116 |

|   | 3.5 | Exper  | iments                                             | 126 |

|   |     | 3.5.1  | Switching Period Waveforms in DCM                  | 128 |

|   |     | 3.5.2  | Load Step Response                                 | 132 |

|   |     | 3.5.3  | Input Current THD                                  | 132 |

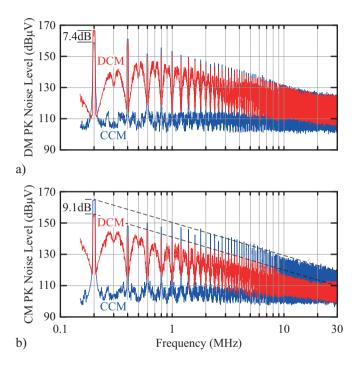

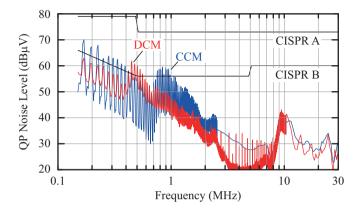

|   |     | 3.5.4  | Conducted EMI Measurement                          | 135 |

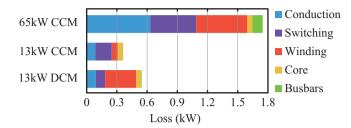

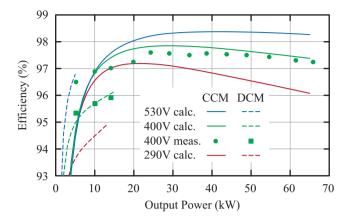

|   |     | 3.5.5  | Loss Distribution and Efficiency                   | 136 |

|   | 3.6 | Summ   | hary of the Chapter                                | 139 |

| 4 | Hig | h Ban  | dwidth Non-Resonant High Voltage Genera            | -   |

|   | tor |        |                                                    | 143 |

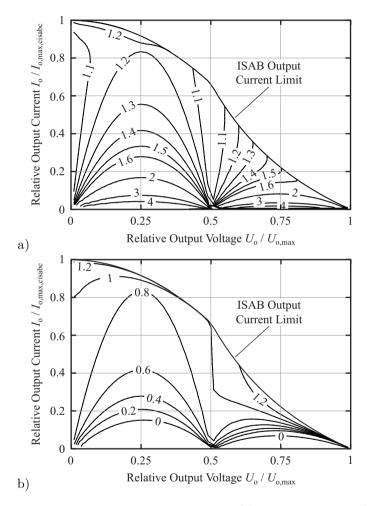

|   | 4.1 | Steady | y-State Analysis                                   | 145 |

|   |     | 4.1.1  | Interleaved Single Active Bridge Converter         | 146 |

|   |     | 4.1.2  | Coupled Interleaved Single Active Bridge Converter |     |

|   | 4.2 | Dynar  | mic Analysis                                       | 166 |

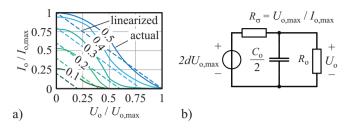

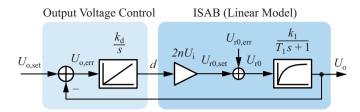

|   |     | 4.2.1  | Linear Model                                       | 166 |

|   |     | 4.2.2  | Output Voltage Closed-Loop Control                 | 168 |

|   |     | 4.2.3  | Midpoint Balancing Closed-Loop Control             | 170 |

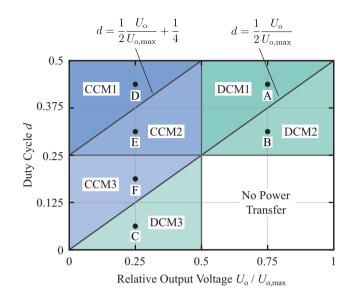

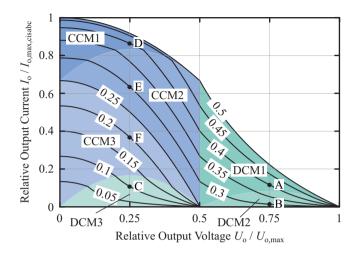

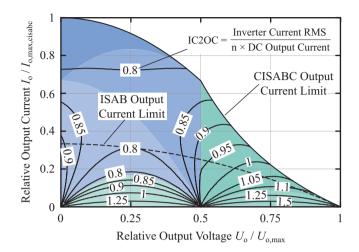

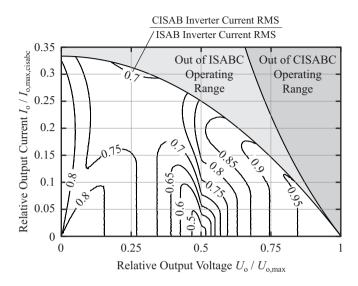

| Bi | Act<br>A.1<br>A.2 | <b>ive Bri</b><br>Discon<br>A.1.1<br>A.1.2<br>A.1.3                      | idge Converter         atinuous Conduction Modes         Discontinuous Conduction Mode 1         Discontinuous Conduction Mode 2         Discontinuous Conduction Mode 3         Discontinuous Conduction Mode 3         Conduction Modes         Continuous Conduction Mode 1         Continuous Conduction Mode 1         Continuous Conduction Mode 1         Continuous Conduction Mode 2         Continuous Conduction Mode 3         Continuous Conduction Mode 3         Continuous Conduction Mode 3 | <b>203</b>                                    |

|----|-------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|    | Act<br>A.1        | ive Bri<br>Discon<br>A.1.1<br>A.1.2<br>A.1.3<br>Contir<br>A.2.1<br>A.2.2 | idge Converter         atinuous Conduction Modes         Discontinuous Conduction Mode 1         Discontinuous Conduction Mode 2         Discontinuous Conduction Mode 3         nuous Conduction Modes         Continuous Conduction Mode 1         Continuous Conduction Mode 2         Continuous Conduction Mode 1         Continuous Conduction Mode 2         Continuous Conduction Mode 1         Continuous Conduction Mode 2                                                                        | 203<br>203<br>205<br>206<br>207<br>207<br>208 |

|    | Act<br>A.1        | ive Bri<br>Discon<br>A.1.1<br>A.1.2<br>A.1.3<br>Contir<br>A.2.1<br>A.2.2 | idge Converter         atinuous Conduction Modes         Discontinuous Conduction Mode 1         Discontinuous Conduction Mode 2         Discontinuous Conduction Mode 3         nuous Conduction Modes         Continuous Conduction Mode 1         Continuous Conduction Mode 2         Continuous Conduction Mode 1         Continuous Conduction Mode 2         Continuous Conduction Mode 1         Continuous Conduction Mode 2                                                                        | 203<br>203<br>205<br>206<br>207<br>207<br>208 |

|    | Act<br>A.1        | ive Bri<br>Discon<br>A.1.1<br>A.1.2<br>A.1.3<br>Contir                   | idge Converter         ttinuous Conduction Modes         Discontinuous Conduction Mode 1         Discontinuous Conduction Mode 2         Discontinuous Conduction Mode 3         Discontinuous Conduction Mode 3         Discontinuous Conduction Mode 3                                                                                                                                                                                                                                                     | <b>203</b><br>203<br>203<br>205<br>206<br>207 |

|    | Act<br>A.1        | <b>ive Bri</b><br>Discon<br>A.1.1<br>A.1.2<br>A.1.3                      | idge Converter         attinuous Conduction Modes         Discontinuous Conduction Mode 1         Discontinuous Conduction Mode 2         Discontinuous Conduction Mode 3                                                                                                                                                                                                                                                                                                                                    | <b>203</b><br>203<br>203<br>205<br>206        |

|    | Act               | ive Bri<br>Discon<br>A.1.1<br>A.1.2                                      | idge Converter         attinuous Conduction Modes         Discontinuous Conduction Mode 1         Discontinuous Conduction Mode 2                                                                                                                                                                                                                                                                                                                                                                            | <b>203</b><br>203<br>203<br>205               |

|    | Act               | ive Bri<br>Discor<br>A.1.1                                               | idge Converter         atinuous Conduction Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>203</b><br>203<br>203                      |

|    | Act               | <b>ive Br</b> i<br>Discor                                                | idge Converter<br>atinuous Conduction Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>203</b><br>203                             |

|    | Act               | ive Bri                                                                  | idge Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 203                                           |

|    |                   |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

|    |                   |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

| ٨  | Cor               | ductio                                                                   | on Modes of the Coupled Interleaved Singl                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                             |

|    | 5.2               |                                                                          | Research and Outlook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 202                                           |

|    | 5.1               | Result                                                                   | s and Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 199                                           |

| 5  | Cor               | clusio                                                                   | ns and Outlook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 199                                           |

|    | 4.5               | Summ                                                                     | ary of the Chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 195                                           |

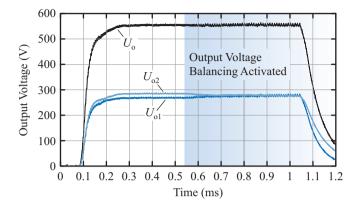

|    |                   | 4.4.4                                                                    | Output Voltage Balancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 195                                           |

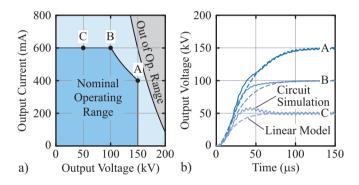

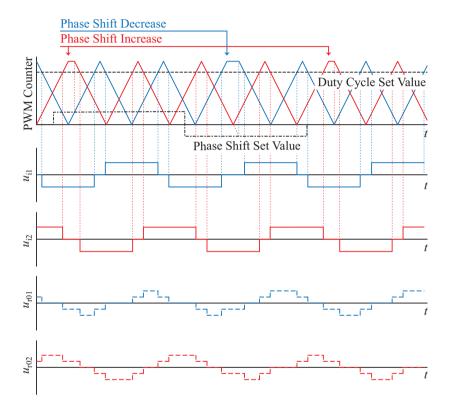

|    |                   | 4.4.3                                                                    | Output Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 194                                           |

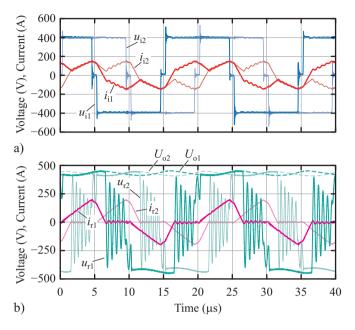

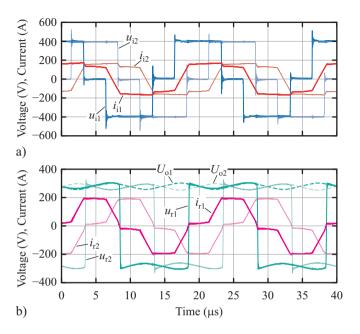

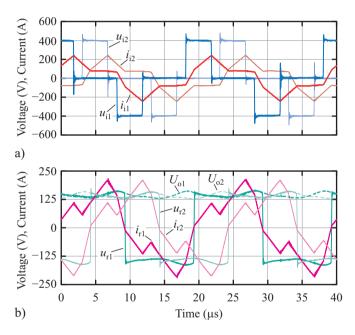

|    |                   | 4.4.2                                                                    | Steady-State Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 189                                           |

|    |                   | 4.4.1                                                                    | Inverter Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 185                                           |

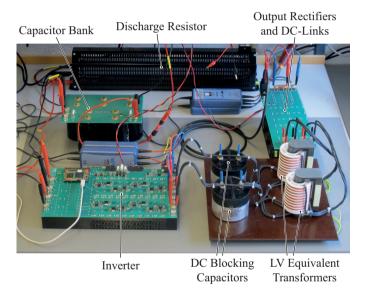

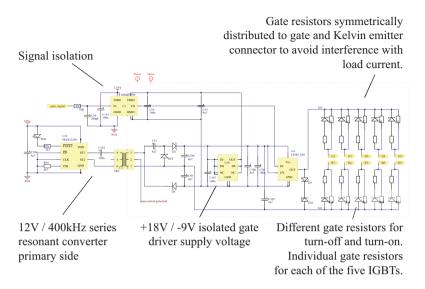

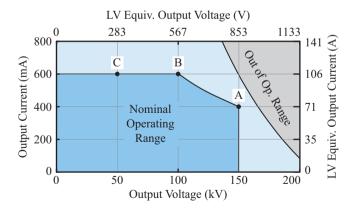

|    | 4.4               |                                                                          | imental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 181                                           |

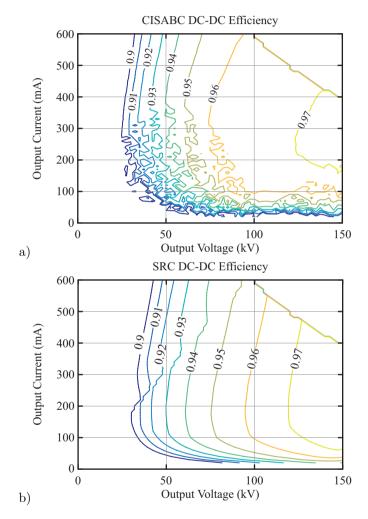

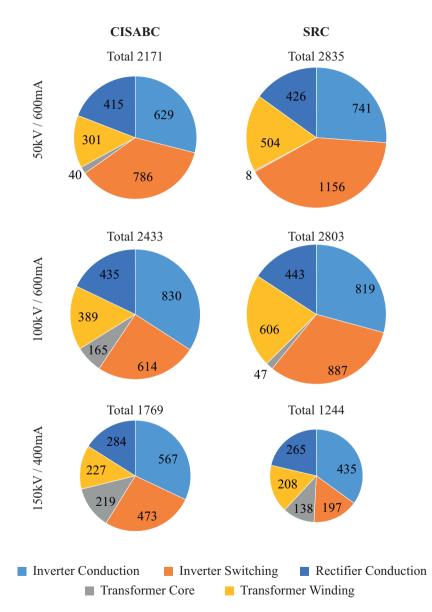

|    | 4.3               |                                                                          | Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 178                                           |

|    |                   | 4.2.6                                                                    | Sampling Delay Reduction with Delta-Sigma ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

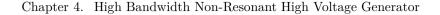

|    |                   | 4.2.5                                                                    | PWM Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 173                                           |

|    |                   | 4.2.4                                                                    | Input Voltage Balancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 172                                           |

# Introduction

N the evening of Friday, November 8, 1895, Wilhelm Conrad Röntgen discovered a new kind of rays. At that time he was Director of the Physical Institute of the University of Würzburg and conducted experiments using a Hittorf-Crookes tube, an evacuated glass tube, connected to a *relatively large Ruhmkorff* high-voltage generator [1]. While applying voltage to the tube that he covered with black cardboard he noticed fluorescence of bariumtetracyanoplatinate coated paper located on a nearby table. He soon ruled out his initial assumption that the rays would be a different kind of light, similar to ultraviolet light because he observed that rays are passing through a wide varity of materials without being able to observe the phenomena of deflection or refraction. However, he noted that with increasing density and thickness of the material that the rays are passing through absorption increases. He published the results of his thorough examinations first in German on December 28, 1895, in Sitzungsberichte der Physikalisch-Medizinischen Gesellschaft in Würzburg [2], English translations in Nature [3] and Science [4] followed early in 1896. In his report he coined the term X-rays, after the unknown variable x. The discovery soon lead to widespread use, not only in medicine but also for entertainment purposes. However, it took years until the actual physical nature of X-rays as high energy photon beams was theoretically described.

#### 1.1 X-Ray Generators

X-rays used for imaging purpose originate mostly as Bremsstrahlung, which is emitted when an electron is deflected and slowed down by the positively charged core of an atom of the anode.

#### 1.1.1 X-Ray Tube

The electron is accelerated within an evacuated tube using a highvoltage applied between a negative cathode and a positive anode. The accelerated electron hits the target, which is part of the anode and usually made of tungsten for its high melting point. The energy spectrum of the photon beam emitted from the target as Bremsstrahlung is continuous since only a few electrons still have their initial energy when being slowed down by an atom's core. Most of the electrons already lost part of their energy due to other Coulomb interactions within the anode. The maximum energy of a photon is thus limited to the initial energy eU the electron has when reaching the target. Increasing the tube voltage U, therefore, increases the mean energy of the photon beam. According to the Beer-Lambert law X-rays entering into matter are exponentially attenuated with increasing depth [5]. The attenuation decreases with increasing photon energy and decreasing material density. Therefore, in order to obtain a high contrast X-ray image the tube voltage needs to be selected depending on the volume and density of the object.

Röntgen's experiment and early X-ray tubes employed cold cathodes where the free electrons for acceleration are generated from discharge ionization of residual gas atoms in the tube. In 1913 William Coolidge invented a tube using a glowing tungsten filament as cathode [6,7]. The thermionic electron emission at the surface of the filament allows higher tube currents and offers the possibility to control the tube current by adjusting the filament temperature and, since the photon generation rate is proportional to the tube current, the intensity of the emitted X-ray beam. This improvement allowed to reduce the exposure time from several minutes or even hours to seconds or less.

The principle of modern X-ray sources is still the same. A tungsten filament, which is part of the cathode and therefore on negative potential, is supplied with an adjustable heating current. The electrons emitted from the filament are accelerated with the tube voltage towards the anode. A large share of the electrons, equivalent to approximately 40% of the energy, is scattered back from the target. Most of the electrons entering the target transfer their energy to phonons, causing the anode to heat up. Only  $\approx 1\%$  of the energy is actually emitted as

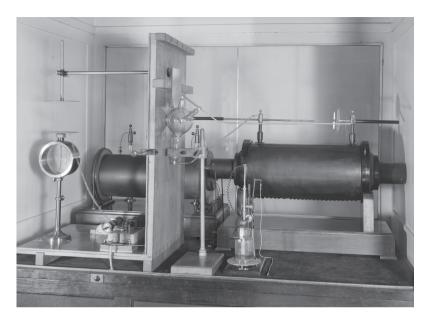

**Fig. 1.1:** X-ray tube (center) and high-voltage generator (right) used by Röntgen to investigate ionization of air by X-rays between two electrodes (left). (Photo: Deutsches Museum)

Bremsstrahlung which can be used for diagnostic and also for therapy purposes [5]. Since the vacuum tube only provides limited heat transfer to the ambient, the average power that can be supplied to the tube is given by the maximum temperature of the anode and its thermal resistance to the ambient and it typically amounts to less than 1 kW. The peak-power however is only limited by the internal thermal resistance of the anode which is typically a composite of tungsten and copper or molybdenum [8]. Therefore, the peak-power can be considerably higher reaching values up to 100 kW. The duration of such a full power pulse is limited by the total amount of energy which can be stored in the thermal capacitance of the anode at its maximum temperature, thus usually full-load pulses are limited to less than 10 s.

#### 1.1.2 High-Voltage Supply

Röntgen's *Ruhmkorff* shown in Fig. 1.1 is a high-voltage generator similar to a fly back converter. An accumulator provided current to the primary coil wound around an iron core, lacking the back iron. A switch interrupts the primary current as soon as it reaches a certain level, igniting an arc. The high arc voltage drives the current rapidly back to zero while a secondary winding provides a high-voltage to the tube [1]. Besides electro mechanical switches also versions using mercury and electrolytic (Wehnelt) contacts were in use [9]. Due to the high duty-cycle, i.e. the relative time the switch is closed, the negative voltage that is applied to the tube is much lower than the positive voltage. Therefore, no rectifier is necessary and X-rays are primarily emitted at one electrode of the tube only.

With the upcoming electrification and AC grids transformers started to replace these early induction coils. The at that time commonly used Coolidge tube exhibits self-rectifying behaviour. It could therefore be directly supplied with AC and acted as half-wave rectifier. However, the self-rectifying property of the tube is lost as soon as the anode heats up to a point where thermionic emission starts and electrons are conducted in both ways. Two-way conduction must be avoided since two X-ray sources would lead to blurred images and destruction of the cathode due to overheating. Therefore, self-rectifying tubes are only found in dental and low power portable units. Early high power X-ray systems employed contacts rotated by a synchronous machine and later rectifier tubes to provide full-wave high-voltage rectification.

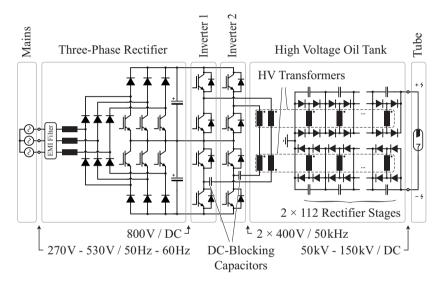

Nowadays X-ray high-voltage supplies mainly use full-wave rectification using series connected diode strings, although there are still a few dental systems employing self-rectification. The high-voltage transformer is usually supplied by an Insulated Gate Field Effect Transistor (IGBT) based inverter switching in the tens of Kilohertz range in order to reduce its size and weight [6]. The high switching frequency also allows to reduce the size of the high-voltage DC-link capacitors. Therefore, Cockcroft-Walton voltage multipliers, which employ a large number of capacitors, are a cost effective solution because they reduce the voltage stress on the transformer's secondary winding, allowing a small and simple construction. However, due to their slow dynamic response their application is limited [10].

#### 1.2 Applications

In medicine, apart from radiation therapy which typically employs linear accelerators, X-rays are mainly used for diagnostic purposes. The classic two-dimensional whole body multi-purpose radiography devices are complemented with specialised equipment for diagnosis of breast cancer (mammography), dental X-ray systems and portable units for use during surgery. Additionally to bones and cavities, such as the lung, also blood vessels can be visualised (angiography) by injecting a contrast medium [11].

Other than single-shot radiography fluoroscopy provides a live X-ray video. The term comes from the fluorescent screens used in early days, nowadays digital detectors capture the video. Fluoroscopy is used to view the functioning of inner organs in motion and also to provide a live view to the surgeon during operations. Due to the long exposure time during fluoroscopy the patient dose is relatively high ranging between 1 mSv to 5 mSv, which is the equivalent of up to two years of natural background radiation exposure (2.4 mSv/y) [12]. Compared to that the dose from a single extremity or intra-oral X-ray image equals the natural radiation exposure of merely one day. In order to limit the patient dose the beam is typically pulsed at an adjustable rate of usually around ten pulses per second (pulsed fluoroscopy) [13].

Following the work of Godfrey Hounsfield the first Computer Tomography (CT) was carried out in 1971 [14]. Since then X-rays can be used to obtain three-dimensional images as well. In principle a CT consists of an X-ray tube with a digital detector which is rotating around the patient to capture one slice, while the patient is moved laterally through the machine to obtain slices of all body parts of interest [15]. For each slice images are taken at evenly spaced angular intervals. The one-dimensional Fast Fourier Transform (FFT) of each projection at a certain angle equals one row through the center of the two-dimensional Fourier transform of the image of the slice at the same angle. The density, or more accurately attenuation coefficient image of the slice, is finally reconstructed by carrying out the inverse FFT [16]. Due to the high number of X-ray images taken during a CT scan, the effective dose to the patient ranges from 2 mSv to 12 mSv which is equivalent to two to five years of natural background ration exposure [12].

#### **1.3** Recent Developments

One recent advancement in X-ray technology is the use of two energy levels (dual energy). The attenuation of the X-ray beam for a specific element shows a spike at the energy corresponding to the binding energy of the K-shell [17]. Since the K-shell energy depends on the atomic number, dual energy scans provide better contrast. Dual energy images are already widely used for bone densitometry but also Dual Energy CT (DECT) is employed more often due to the better soft tissue contrast. There are still three competing DECT technologies [18]. Dual source DECT uses two tubes and two detectors working at different voltages, typically 80 kV and 140 kV. Single source DECTs use only one tube which is either switching between two voltage levels at approximately 1 kHz (rapid kVp switching) or which uses two detectors sensitive to different parts of the spectrum (dual detector layer).

Another development aims at the reduction of the patient dose by reducing the rise times and fall times of the tube voltage caused by the charging and discharging of the high-voltage capacitors. This is of particular concern with pulsed fluoroscopy which exhibits relatively high dose per treatment and high pulse frequency [13]. Although the relative duration of the rising and falling voltage edges is short, during that time low energy X-rays are emitted which is, compared with higher energy X-rays, mostly absorbed by the patient and therefore contributes a significant share of the dose. Most nowadays systems use an additional anode control grid to rapidly pulse the beam since the high-voltage risetimes and fall-times are too long. By increasing the bandwidth of the high-voltage generator the control grid on the tube could be eliminated.

#### 1.4 Objective and Contributions

The objective of this work is to optimize an X-ray power supply providing  $60 \,\mathrm{kW}$  to the tube at up to  $150 \,\mathrm{kV}$  DC voltage with rise-times and fall-times of less than  $500 \,\mathrm{\mu s}$  from a three-phase mains with line-to-line RMS input voltage range of  $290 \,\mathrm{V}$  to  $530 \,\mathrm{V}$ . The specified voltage range results from the requirement to deal with  $400 \,\mathrm{V}$  and  $480 \,\mathrm{V}$  mains voltages with  $10 \,\%$  over- and  $20 \,\%$  under-voltage tolerance. Nowadays X-ray power supplies are using six-pulse passive diode rectifiers supplying a DC voltage which is depending on the mains voltage. high-voltage generators connected to passive rectifiers therefore either have to be

able to cope with a wide input voltage range, while also providing a wide output voltage range of typically  $50 \,\text{kV}$  to  $150 \,\text{kV}$  to the tube, or are equipped with a mains frequency transformers stepping down the  $480 \,\text{V}$  mains to  $400 \,\text{V}$ . Furthermore, six-pulse diode rectifiers exhibit considerable harmonic current emissions which may require additional low-frequency harmonic filtering depending on the utility grid regulations [19]. This work presents an active mains interface which provides a stable DC-link voltage to the high-voltage generator and sinusoidal currents to the mains.

#### 1.4.1 Three-Phase PFC Rectifier

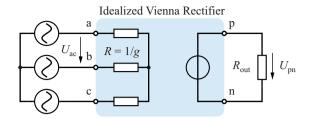

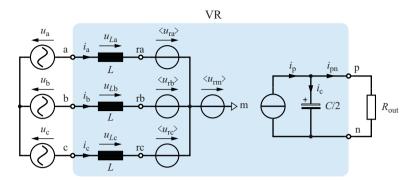

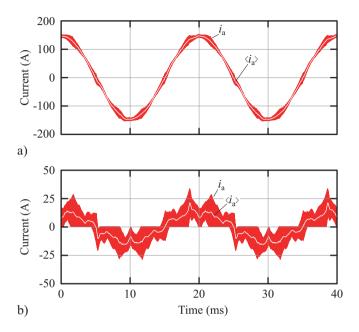

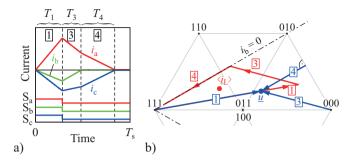

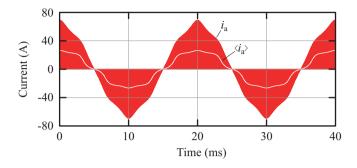

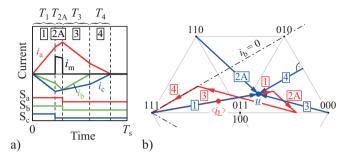

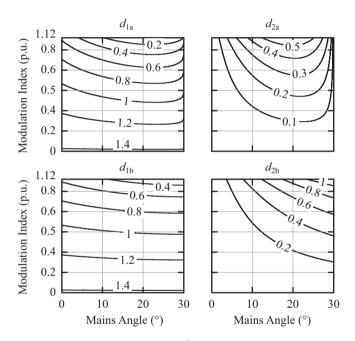

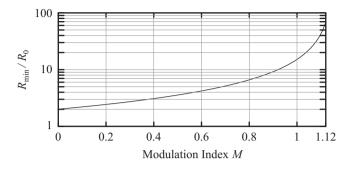

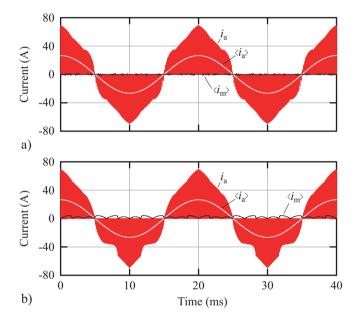

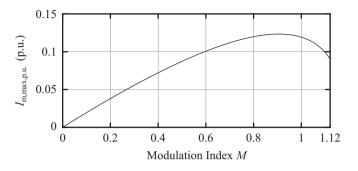

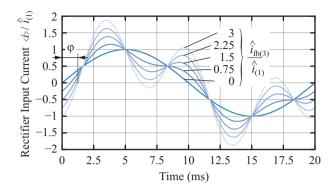

While highly efficient active three-phase Power Factor Correction (PFC) rectifiers are common for Uninterruptible Power Supply (UPS) and telecommunication supplies, a design optimized for use with X-ray systems faces different challenges. Because of the high peak-to-average load ratio and the low amount of full-load operating hours, one can take advantage of the relatively low average power. The primary objective is to reach lowest material cost instead of highest efficiency, while maintaining high reliability despite the thermal cycling of the components [20]. Optimizing the trade-off between material cost and loss energy cost during operation, i.e. minimizing the total cost of ownership, results in relatively small boost inductors of the rectifier, exhibiting high current ripple. The Vienna rectifier, a unidirectional three-phase three-level rectifier, provides stable DC-link voltage and sinusoidal input currents and compared to the two-level six-switch rectifier [21] the power semiconductors only need to block half of the DC-link voltage which can be as low as the line-to-line peak voltage. Therefore, low switching loss 650 V IGBTs in combination with low reverse recovery charge 650 Vfree-wheeling diodes can be employed which match the low-cost, high reliability design target. However, due to its unidirectional structure the Vienna rectifier exhibits a Discontinuous Conduction Mode (DCM) which occurs when the current ripple is in the range of the amplitude of the input current fundamental. For light load, which would be a common use case for fluoroscopy, the Vienna rectifier mainly operates in DCM. However, due to the different duty-cycle to voltage relationship conventional Continuous Conduction Mode (CCM) current control schemes in DCM result in distorted input currents. The main scientific contribution, resulting from the design of the rectifier, is the derivation

of a control scheme that allows to maintain sinusoidal currents in DCM which is presented in Chapter 3.

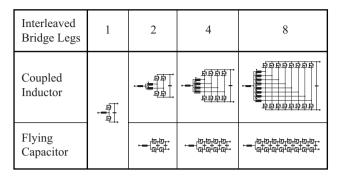

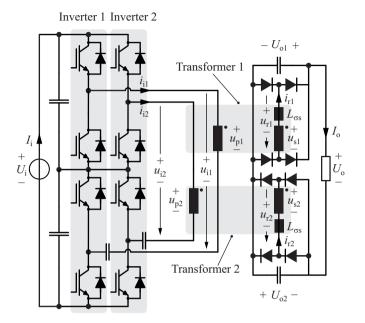

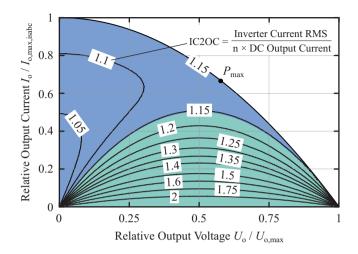

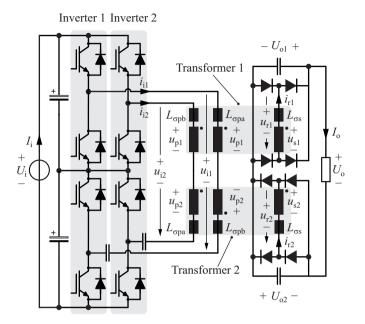

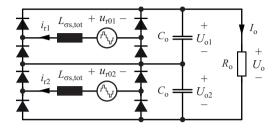

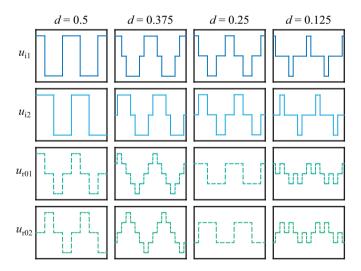

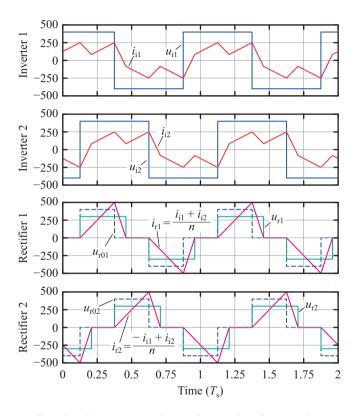

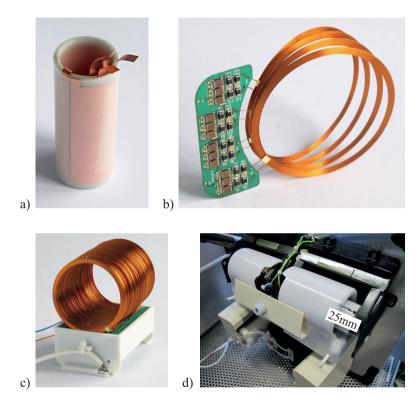

#### 1.4.2 High-Voltage Generator

On the output side the primary challenge, apart from the high-voltage and power demand, is to reach low-voltage rise-times and fall-times. Most nowadays high-voltage generators for X-ray systems use a resonant converter, allowing to integrate the high stray inductance and winding capacitance of the high-voltage transformer into the resonant tank and achieve either zero current or zero voltage switching on the inverter. However, the two main drawbacks of resonant converters are the variable switching frequency which is required to maintain zero voltage switching for all operating conditions and the slow dynamic response of the resonant tank which slows down the output voltage control. Therefore, a non-resonant interleaved approach is proposed which features zero voltage switching with constant switching frequency and fast output voltage control employing two low winding capacitance multi-rectifier high-voltage transformers. The main contribution to the high-voltage generator is the invention of an interleaved circuit which employs two coupled transformers, allowing to reduce the inverter RMS current compared to an uncoupled variant which is presented in Chapter 4.

#### 1.5 List of Publications

Different parts of the research findings presented in this thesis have already been published or will be published in international scientific journals, conference proceedings and tutorials, or have been protected by multi-national patents. The publications and patents developed in the course of this thesis are listed below.

#### Journal Papers

▶ M. Leibl, G. Ortiz, and J. W. Kolar, "Design and Experimental Analysis of a Medium Frequency Transformer for Solid-State Transformer Applications," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 5, no. 1, pp. 110–123, March 2017. DOI: 10.1109/JESTPE.2016.2623679

- M. Leibl, J. W. Kolar, and J. Deuringer, "Sinusoidal Input Current Discontinuous Conduction Mode Control of the VIENNA Rectifier," *IEEE Transactions on Power Electronics*, vol. 32, no. 11, pp. 8800–8812, November 2017. DOI: 10.1109/TPEL.2016.-2641502

- M. Leibl, O. Knecht, and J. W. Kolar, "Inductive Power Transfer Efficiency Limit of a Flat Half-Filled Disc Coil Pair," accepted for publication in *IEEE Transactions on Power Electronics*, 2018. DOI: 10.1109/TPEL.2018.2797366

- M. Leibl, J. W. Kolar, and J. Deuringer, "High Bandwidth Non-Resonant High Voltage Generator for X-Ray Systems," under review at CPSS Transactions on Power Electronics and Applications, 2018.

#### **Conference** Papers

- M. Leibl, and J. W. Kolar, "Comparative Analysis of Inductor Concepts for High Peak Load Low Duty Cycle Operation," in *Proceedings of the International Power Electronics Conference (IPEC* - *ECCE Asia)*, Hiroshima, Japan, May 2014, pp. 899–906. DOI: 10.1109/IPEC.2014.6869694

- ▶ M. Leibl, M. Darani, J. Deuringer, and J. W. Kolar, "New Boundary Mode Sinusoidal Input Current Control of the VIENNA Rectifier," in *Proceedings of the IEEE Energy Conversion Congress* and Exposition (ECCE USA), Pittsburgh, PA, USA, September 2015, pp. 1240–1247. DOI: 10.1109/ECCE.2014.6953543

- ▶ M. Leibl, J. Deuringer, and J. W. Kolar, "New Current Control Scheme for the Vienna Rectifier in Discontinuous Conduction Mode," in *Proceedings of the IEEE Energy Conversion Congress* and Exposition (ECCE USA), Pittsburgh, PA, USA, September 2014, pp. 201–209. DOI: 10.1109/ECCE.2015.7309689

#### Patents

M. Leibl, "Verfahren zur Steuerung eines Mehrpunkt-Gleichrichters," German Patent Application No. DE102014214276A1, Filed Jul. 22, 2014, published Jan. 28, 2016.  M. Leibl, "Hochspannungsgenerator f

ür ein R

öntgenger

ät," German Patent Application No. DE102016215765, filed Aug. 23, 2016.

#### **Further Scientific Contributions**

- G. Ortiz, M. Leibl, J. W. Kolar, and O. Apeldoorn "Medium Frequency Transformers for Solid-State-Transformer Applications -Design and Experimental Verification," in *Proceedings of the 10th IEEE International Conference on Power Electronics and Drive Systems (PEDS)*, Kitakyushu, Japan, April 2013, pp. 1285–1290. DOI: 10.1109/PEDS.2013.6527217

- G. Ortiz, M. Leibl, J. Huber, and J. W. Kolar, "Design and Experimental Testing of a Resonant DC-DC Converter for Solid-State Transformers," in *IEEE Transactions on Power Electronics*, vol. 32, no. 10, pp. 7534–7542, October 2017. DOI: 10.1109/TPEL-2016.2637827

- L. Schrittwieser, M. Leibl, M. Haider, F. Thöny, J. W. Kolar, and T. Soeiro "99.3% Efficient Three-Phase Buck-Type All-SiC SWISS Rectifier for DC Distribution Systems" in *Proceedings of the 32nd Applied Power Electronics Conference and Exposition* (APEC), Tampa, FL, USA, March 2017, pp. 2173–2178. DOI: 10.1109/APEC.2017.7931000

- ▶ J. Azurza Anderson, L. Schrittwieser, M. Leibl, and J. W. Kolar, "Multi-Level Topology Evaluation for Ultra-Efficient Three-Phase Inverters" in *Proceedings of the IEEE International Telecommunications Energy Conference (INTELEC)*, Broadbeach, QLD, Australia, October 2017, pp. 456–463. DOI: 10.1109/INTLEC.2017.-8214178

# Optimized Design of Inductive Components

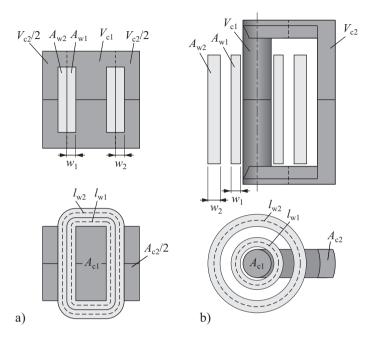

**O** PTIMIZATION of transformers and inductors, referred to as inductive components, can be time consuming due to the multitude of available parameters. First, the designer can choose between different core topologies, such as shell-type, core-type, toroidal and pot cores. Second, the geometric dimensions have to be specified which alone amount to four variables: width and height of core area and winding area. In case of an inductor also the air gap needs to be determined. Third, the structure of the winding needs to be specified as well by setting the number of turns, the conductor profile (rectangular or round), the type of conductor (solid or stranded) and if stranded the number of strands. Finally, the core material needs to be selected from different kinds of ferrite and iron powder materials, amorphous and nanocrystalline tapes and laminated silicon steel. Together all this parameters form the so-called design space. In practice this design space is heavily reduced by the limited availability of cores and conductors.

The core component of the optimization process is the model which maps the design space to the so-called performance space. The losses of an inductive component is the dimension of the performance space which is always present. Additionally a binary dimension is often used which indicates if the maximum values of winding and core temperature, core flux density and isolation electric field are within the limits given by the material. Volume, weight and material cost are also common dimensions of the performance space.

In order to find the best design, a cost function has to be applied to the performance space which assigns a price to each member of the design space. A simple example of a cost function evaluates, for a given number of operating hours and energy cost, the sum of the energy cost during the component life and its initial material cost. This is known as Total Cost of Ownership (TCO) optimization. Depending on the application other dimensions can be taken into account as well. In case of inductive components for aircraft for example one may want to add a price for the weight of the device. Finally, the design with the lowest cost can be considered optimal with respect to the given cost function.

Prior to applying the cost function, the performance space can be reduced to the Pareto front which always includes the best design. The Pareto front consists of all elements of the performance space which are *better* in at least one dimension than all the other elements of the performance space. Implicitly the relation *better* assumes a part of the cost function which is usually possible. For example, lower values of loss, weight, volume and material cost are always better than higher ones. Often the Pareto front is used to illustrate trade-offs and when a cost function cannot be specified due to the lack of reliable prices.

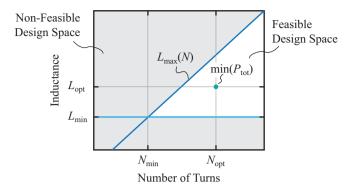

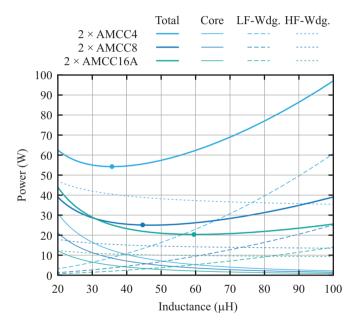

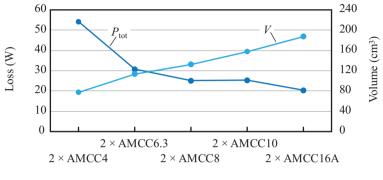

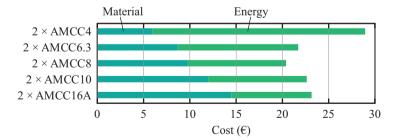

Applying the cost function only to the Pareto front reduces the computational effort for evaluating the cost function. However, the additional effort for finding the Pareto front usually outweighs this benefit. Instead, in order to reduce the computational effort the design space can be confined to include only *optimized designs* using analytically found optimality criteria, such as the optimum number of turns of a transformer.

#### 2.1 High-Frequency Winding Losses

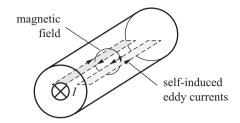

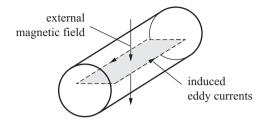

One essential part of the loss model of an inductive component is the winding loss model which needs to take into account the eddy current losses within the winding. Often the eddy current loss in a single conductor of the winding is separated into two parts, the skin effect losses and the proximity effect losses. While the skin effect describes the eddy current loss due to the magnetic field of the current in the conductor itself, the proximity effect describes the extra losses due to eddy currents induced by an external magnetic field, i.e. the magnetic field of all other conductors constituting the winding. For the two common cases of windings consisting of foil and round conductors analytic solutions for the eddy current losses due to skin and proximity effect are known. This Section provides an overview of the existing analytic solu-

Fig. 2.1: Skin effect in a round conductor.

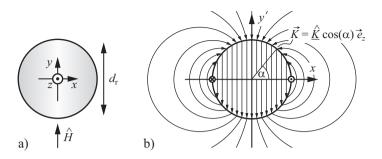

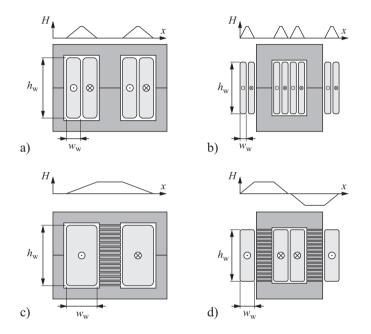

tions for the calculation of skin and proximity effect and a comparison to Finite Element Method (FEM) simulations. Furthermore, simplified approximations of the exact solutions for conductor dimensions much smaller or much larger than skin depth are derived. Finally, the loss expressions for foil and round conductors are used to derive the losses in typical winding arrangements and the results are again compared to FEM simulations.

#### 2.1.1 Skin Effect

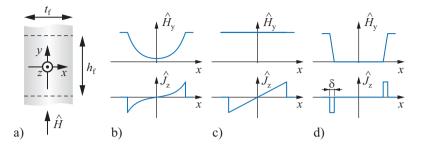

A current flowing in a conductor also creates a magnetic field within the conductor. If the current is varying over time (AC) this magnetic field induces a voltage that causes eddy currents inside the conductor itself. The direction of these eddy currents is such that they counteract the current density in the interior of the conductor and add to the current density at the surface of the conductor as shown in Fig. 2.1. Therefore, High-Frequency (HF) currents are concentrated mainly within a layer beneath the conductor surface called the skin depth. In the following the skin effect for a half-space boundary and for foil conductors is derived and the solution for round conductors is reviewed. It is shown that the simple result of the half-space boundary can be used to approximate the skin effect for the cases of foil- and round conductor as well.

#### Skin Effect at Half-Space Boundary

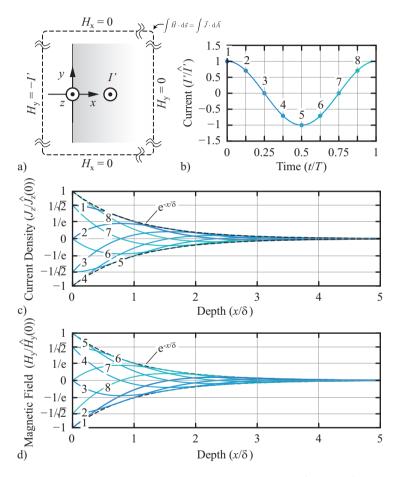

It is assumed that a current per unit length (in y-direction) I' flows distributed within a conductor filling the half-space x > 0. The current is oriented in z-direction. The half-space x < 0 is electrically isolating. The situation is shown in Fig. 2.2a. If the current is sinusoidal with am-

Fig. 2.2: One-dimensional skin effect at the boundary (yz plane) between an isolating half-space and a conductive half-space.

plitude  $\hat{I}'$  and frequency  $\omega=2\pi f,$  it is distributed such that Ampère's law

$$\vec{\nabla} \times \vec{H} = \vec{J} \tag{2.1}$$

and Faraday's law

$$\vec{\nabla} \times \vec{E} = -\frac{\mathrm{d}\vec{B}}{\mathrm{dt}} \tag{2.2}$$

are fulfilled. Because of the infinite extension in y- and z-direction there are only current density components in z-direction and magnetic field components in y-direction. Furthermore, since the current is sinusoidal complex analysis can be used. Therefore, (2.1) and (2.2) simplify to

$$\frac{\mathrm{d}\hat{H}_y}{\mathrm{dx}} = \hat{J}_z \tag{2.3}$$

and

$$\frac{\mathrm{d}\underline{\hat{E}}_z}{\mathrm{dx}} = j\omega\underline{\hat{B}}_y. \tag{2.4}$$

Using the material relationships  $E = \frac{J}{\sigma}$  and  $B = \mu H$  (2.3) and (2.4) can be combined to obtain the homogeneous second order differential equation for the magnetic field inside the conductor

$$\frac{\mathrm{d}^2 \underline{\hat{H}}_y}{\mathrm{dx}^2} = j\omega\mu\sigma\underline{\hat{H}}_y.$$

(2.5)

The fundamental solution of this kind of differential equation is any constant multiple of  $e^{\lambda x}$ , which leads to the characteristic equation  $\lambda^2 = j\omega\mu\sigma$  and it's solutions

$$\lambda = \pm \sqrt{\omega\mu\sigma} = \pm \frac{1+j}{\delta} \tag{2.6}$$

with the skin depth

$$\delta = \frac{1}{\sqrt{\pi f \sigma \mu}}.\tag{2.7}$$

Using both possible values of  $\lambda$  leads to the general solution for the magnetic field inside the conductor

$$\underline{\hat{H}}_y = C_1 \mathrm{e}^{\frac{1+j}{\delta}x} + C_2 \mathrm{e}^{-\frac{1+j}{\delta}x} \tag{2.8}$$

with the constants  $C_1$  and  $C_2$  still to be determined by boundary conditions. For the half-space boundary it is assumed that deep inside the

conductor, i.e. for  $x \to \infty$ , the magnetic field and the current density approach zero, thus

$$\underline{\hat{H}}_{y}(\infty) \to 0 \Rightarrow C_{1} = 0.$$

(2.9)

Applying Ampère's law in the integral form on a loop as shown in Fig. 2.2a shows that the magnetic field at the conductor surface equals the total current flow per unit length in y-direction but with opposite sign, therefore

$$\underline{\hat{H}}_{y}(0) = -\underline{\hat{I}}' \Rightarrow C_2 = -\underline{\hat{I}}.$$

(2.10)

The magnetic field inside the conductive half-space is finally found to be

$$\underline{\hat{H}}_{y}(x) = -\underline{\hat{I}}' \mathrm{e}^{-\frac{1+j}{\delta}x}.$$

(2.11)

Using (2.3), the current density can be derived from the magnetic field as

$$\underline{\hat{J}}_{z}(x) = \underline{\hat{I}}' \frac{1+j}{\delta} \mathrm{e}^{-\frac{1+j}{\delta}x}.$$

(2.12)

The solutions show, that current density and magnetic field are attenuated in amplitude by a factor e and phase-shifted by  $-90^{\circ}$  per skin-depth  $\delta$ . For different times during the current period marked in Fig. 2.2b the instantaneous values of current density and magnetic field are shown in Fig. 2.2c and d. The instantaneous ohmic loss per unit area of the yz-plane inside the conductive half-space is calculated as

$$p'' = \vec{S}(0) \cdot \vec{e}_x = -E_z(0)H_y(0) \tag{2.13}$$

using the Poynting vector  $\vec{S} = \vec{E} \times \vec{H}$ . Therefore, the time average ohmic loss per unit area is

$$P'' = \frac{1}{2} \Re\{-\underline{\hat{E}}_z(0)\underline{\hat{H}}_y(0)^*\} = \frac{1}{2} \frac{\hat{I}'^2}{\sigma\delta}.$$

(2.14)

According to (2.14) in terms of losses it is equivalent to assume that instead of the actual current density distribution shown in Fig. 2.2c the current I' flows uniformly distributed in a layer of thickness  $\delta$ . This result, although only exact for the case of a conductor filling one halfspace, can be used with good accuracy also in situations of practical interest as will be shown in the following.

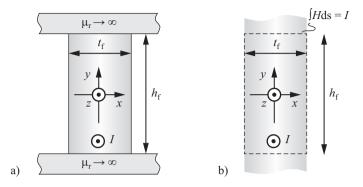

**Fig. 2.3:** Dimensions and coordinate systems for derivation of skin effect in a piece of foil terminated by two highly permeable parts (a) and equivalent piece of a foil conductor, extending infinitely in *y*- and *z*-direction (b).

#### Skin Effect in Foil Conductors

In order to obtain a simple closed form expression, the skin effect for foil conductors is described for the special case of the foil conductor being terminated by two infinitely permeable pieces as shown in Fig. 2.3a. This situation is equivalent to the one of a (finite) piece of a foil conductor, infinitely extending in y-direction (Fig. 2.3b) and can therefore be described one-dimensionally, with the magnetic field oriented in yand the current density in z-direction. These are exactly the assumptions that resulted in (2.8), which will be used as a starting point for the derivation of the skin effect loss in a foil conductor. In order to determine the constants  $C_1$  and  $C_2$ , Ampère's law is applied at the integration path indicated in Fig. 2.3b. With the origin of the coordinate system placed at the center of the conductor, the boundary conditions for the magnetic field,

$$\underline{\hat{H}}_{y}(\frac{t_{\rm f}}{2}) = \frac{\hat{I}}{2h_{\rm f}} \quad \text{and} \quad \underline{\hat{H}}_{y}(-\frac{t_{\rm f}}{2}) = -\frac{\hat{I}}{2h_{\rm f}}, \tag{2.15}$$

are obtained. Because of the odd symmetry  $\underline{\hat{H}}_{y}(\frac{t_{f}}{2}) = -\underline{\hat{H}}_{y}(-\frac{t_{f}}{2}), C_{2} = -C_{1}$ , and thus

$$C_1 = \frac{\hat{I}}{2h_{\rm f}} \frac{1}{\mathrm{e}^{\frac{1+j}{\delta} \frac{t_{\rm f}}{2}} - \mathrm{e}^{-\frac{1+j}{\delta} \frac{t_{\rm f}}{2}}}$$

(2.16)

is valid. Therefore, the magnetic field within the foil conductor is

$$\underline{\hat{H}}_{y}(x) = \frac{\underline{\hat{I}}}{2h_{\rm f}} \frac{\mathrm{e}^{\frac{1+j}{\delta}x} - \mathrm{e}^{-\frac{1+j}{\delta}x}}{\mathrm{e}^{\frac{1+j}{\delta}\frac{t_{\rm f}}{2}} - \mathrm{e}^{-\frac{1+j}{\delta}\frac{t_{\rm f}}{2}}}.$$

(2.17)

From that the current density is derived using (2.3) as

$$\underline{\hat{J}}_{z}(x) = \frac{\underline{\hat{I}}}{2h_{\rm f}} \frac{1+j}{\delta} \frac{\mathrm{e}^{\frac{1+j}{\delta}x} + \mathrm{e}^{-\frac{1+j}{\delta}x}}{\mathrm{e}^{\frac{1+j}{\delta}\frac{t_{\rm f}}{2}} - \mathrm{e}^{-\frac{1+j}{\delta}\frac{t_{\rm f}}{2}}}.$$

(2.18)

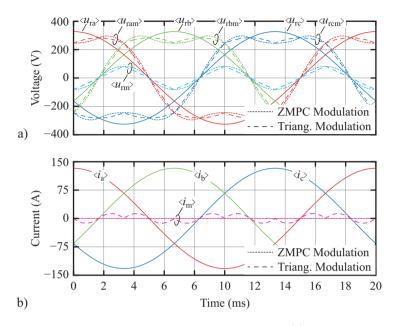

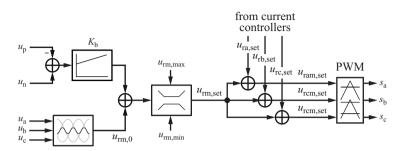

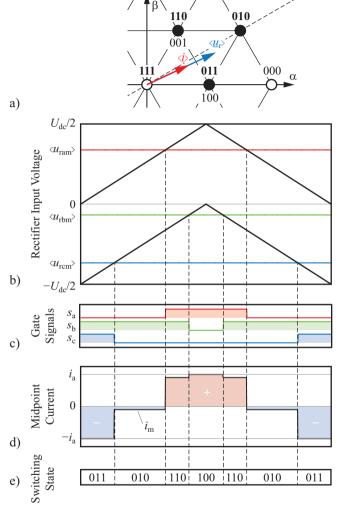

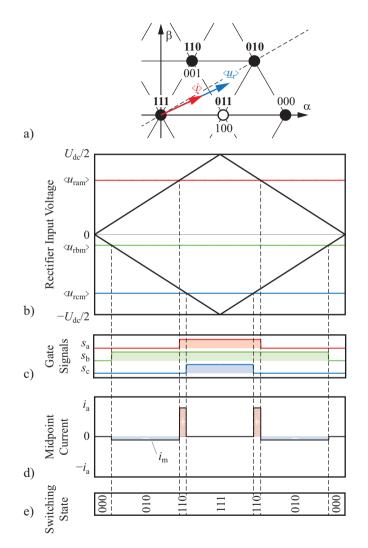

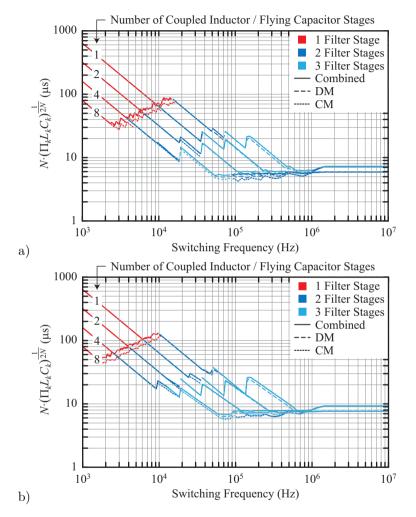

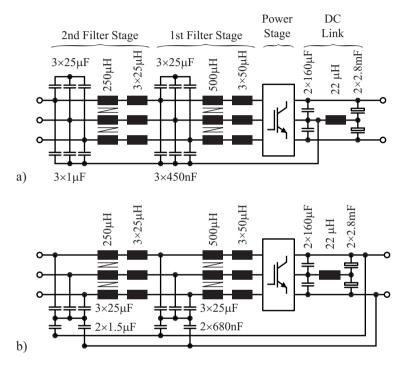

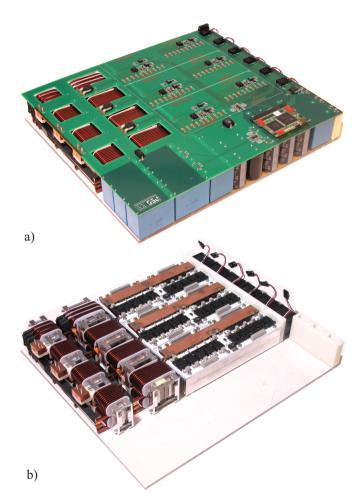

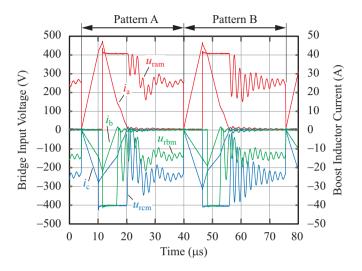

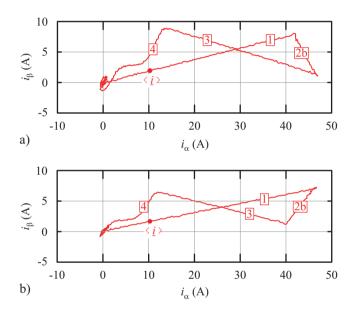

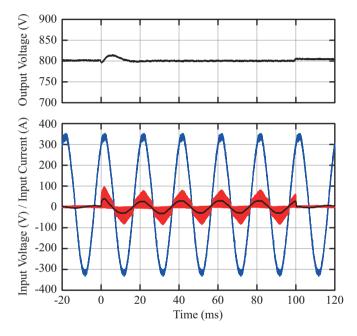

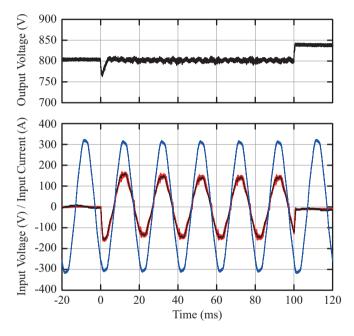

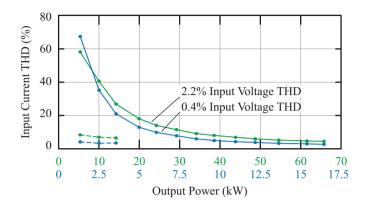

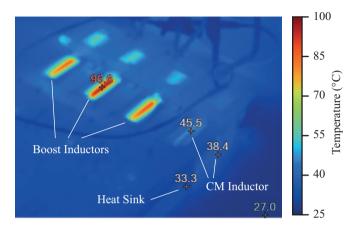

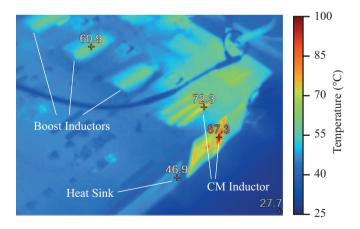

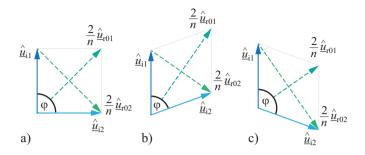

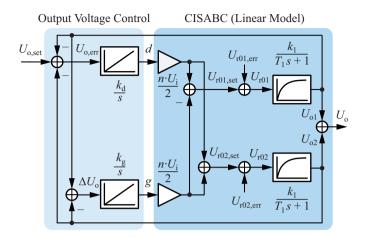

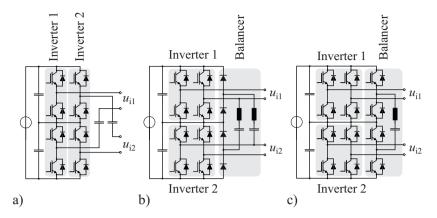

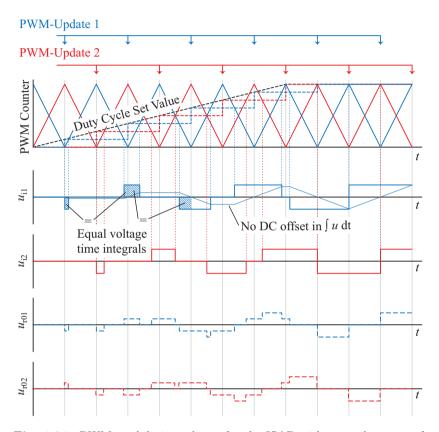

The time average ohmic loss in a piece of unit area of the foil conductor is obtained by evaluating the Poynting vector at both conductor surfaces. Due to symmetry it is sufficient to multiply the result obtained for one surface by two. Therefore, the average ohmic loss within a piece of unit area of a foil conductor due to skin effect is