# How to Achieve 200W/in3 & Beyond? Concepts - Evaluation - Barriers - Future

#### **Educational Material**

Author(s):

Kolar, Johann W. (D); Neumayr, Dominik; Bortis, Dominik (D)

**Publication date:**

2017-03

Permanent link:

https://doi.org/10.3929/ethz-b-000187218

Rights / license:

In Copyright - Non-Commercial Use Permitted

#### Google Little Box Reloaded

# How to Achieve 200W/in³ & Beyond? Concepts - Evaluation - Barriers - Future

J. W. Kolar, D. Neumayr, D. Bortis

Swiss Federal Institute of Technology (ETH) Zurich

Power Electronic Systems Laboratory

www.pes.ee.ethz.ch

#### **Outline**

- ► The Google Little Box Challenge

- ► Little Box 1.0

- Concepts & Performances of Other Finalists

Analysis of Advanced Concepts

- Optimization of Little Box 1.0

- ► Little Box 2.0

- ► *Little Box 3.0* / Conclusions

E. Hoene / FH IZM St. Hoffmann / FH IZM F. Zajc / Fraza F. Krismer M. Guacci L. Camurca Acknowledgement M. Kasper

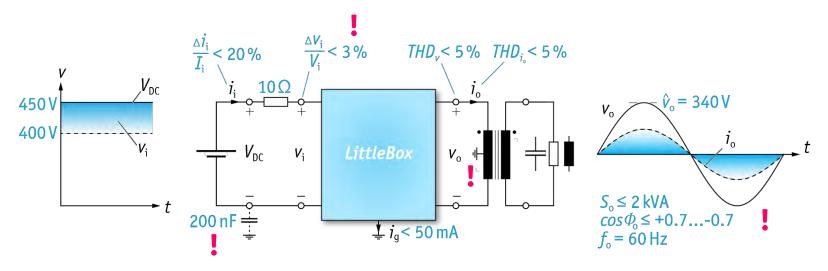

Requirements The Grand Prize Finalists & Finals

- Design / Build the 2kW 1-ΦSolar Inverter with the Highest Power Density in the World

- Power Density > 3kW/dm<sup>3</sup> (> 50W/in<sup>3</sup>, multiply kW/dm<sup>3</sup> by Factor 16)

- Efficiency > 95%

- Case Temp. < 60°C</li>

- EMI FCC Part 15 B

■ Push the Forefront of New Technologies in R&D of High Power Density Inverters

- Highest Power Density (> 50W/in³)

Highest Level of Innovation

\$1,000,000

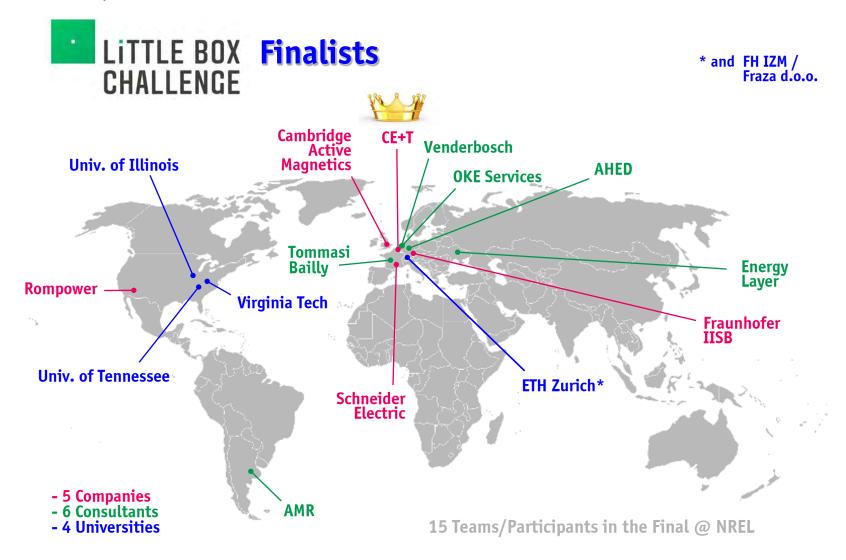

- **■** Timeline

- Challenge Announced in Summer 2014

2000+ Teams Registered Worldwide

100+ Teams Submitted a Technical Description until July 22, 2015

- 18 Finalists (3 No-Shows)

# LITTLE BOX Final Presentations CHALLENGE

- Finalists Invited to NREL / USA

Presentations on Oct. 21, 2015

Subsequent Testing by NREL

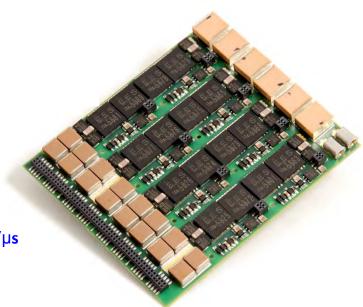

#### Little Box 1.0

Converter Topology Modulation & Control Technologies /Components Mechanical Concept Exp. Analysis

Acknowledgement

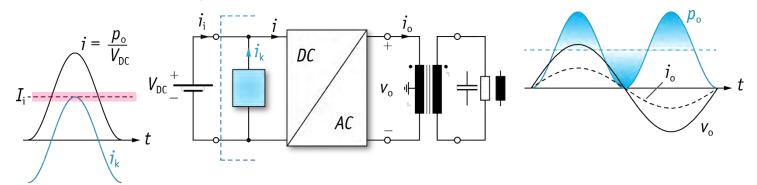

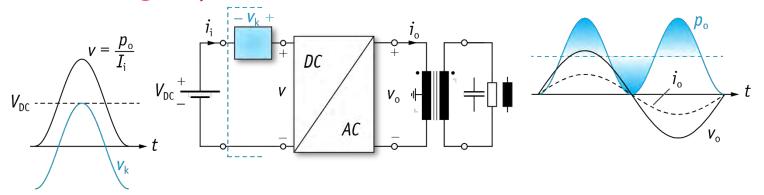

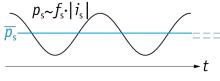

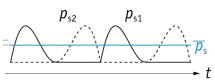

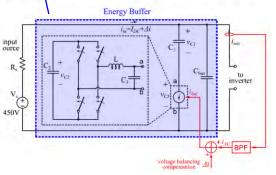

\_ 1-Φ Output Power Pulsation Buffer

#### **Power Pulsation Buffer**

• Parallel Buffer @ DC Input

• Series Buffer @ DC Input

■ Parallel Approach for Limiting Voltage Stress on Converter Stage Semiconductors

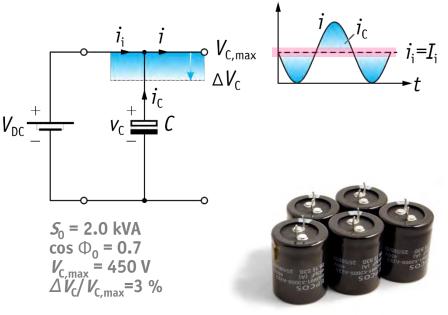

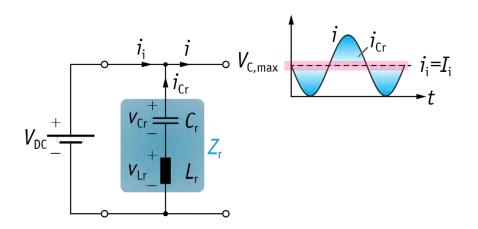

## **Passive Power Pulsation Buffer (1)**

• Electrolytic Capacitor

■  $C > 2.2 \text{mF} / 166 \text{ cm}^3 \rightarrow \text{Consumes } 1/4 \text{ of Allowed Total Volume } !$

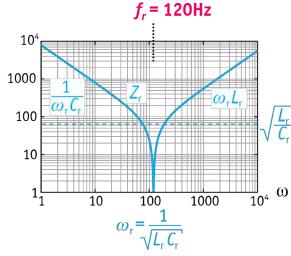

## **Passive Power Pulsation Buffer (2)**

• Series Resonant Circuit / Used in Rectifier Input Stage of Locomotives

\*  $C_r = 20 \mu F$ \*  $L_r = 127 \text{ mH } @ \nu_{Lr} = 400 \text{ V}$

■ Unacceptably Large Inductor Volume!

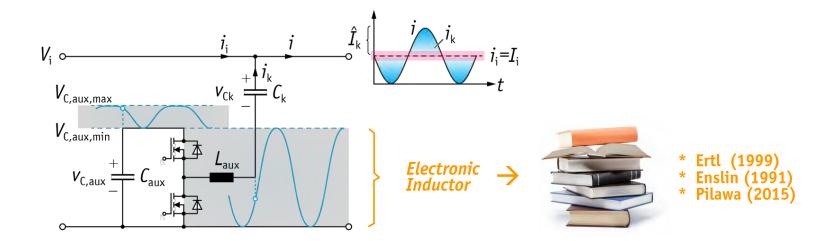

**→ Electronic Inductor**

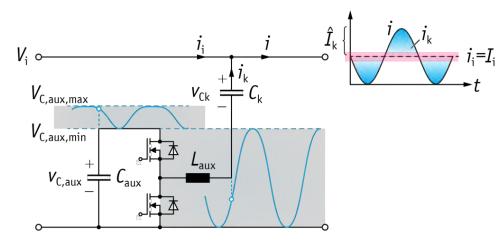

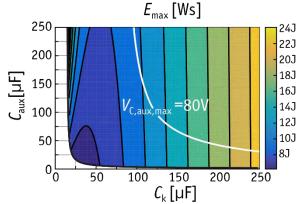

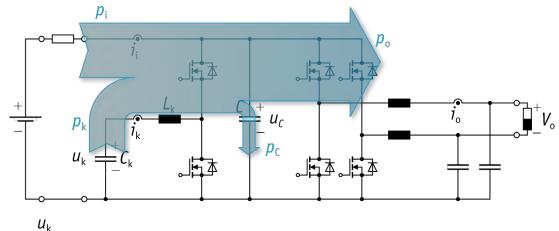

#### **Partial Active Power Pulsation Buffer**

• Coupling Capacitor & "Electronic Inductor" Processing Only Partial Power

- Low U<sub>C,aux</sub> → Low Converter Losses

High Values of C<sub>K</sub>, C<sub>aux</sub> Required for Low U<sub>C,aux</sub>

Full-Bridge Aux. Converter Allows Lower U<sub>C,aux</sub>

#### **Partial Active Power Pulsation Buffer**

• Coupling Capacitor & "Electronic Inductor"

■ Low U<sub>C,aux</sub> → Low Converter Losses

■ High Values of C<sub>K</sub>, C<sub>aux</sub> Required for Low U<sub>C,aux</sub>

■ Full-Bridge Aux. Converter Allows Lower U<sub>C,aux</sub>

Properties of Full-Bridge Aux. Conv.

#### **Full Active Power Pulsation Buffer**

Kyritsis (2007)

- Large Voltage Fluctuation Foil or Ceramic Capacitor Buck- or Boost-Type DC/DC Interface Converter Buck-Type allows Utilizing 600V Technology

■ Significantly Lower Overall Volume Compared to Electrolytic Capacitor

Output Stage - Topology / Modulation ———

## **Derivation of Output Stage Topology (1)**

• Inversion of Basic 1-⊕ PFC Rectifier Topology

- Boost-Type 1-⊕ PFC Rectifier

DC/|AC| Buck Converter & Mains Frequency "Unfolder"

\* Erickson (2009)  $\rightarrow$  Analysis Only for  $\cos \Phi = -1$

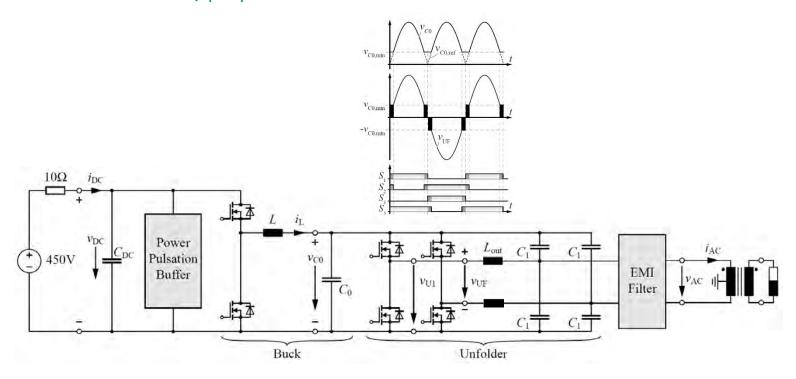

# DC/ | AC | -Buck Conv. & Unfolder

- Only Single Bridge Leg for Current Shaping

- Distortion @ Voltage Zero Crossing

■ For ZVS TCM Operation of Buck-Stage Bridge Leg | AC | Voltage Cannot be Controlled Down to Zero

# Advanced DC/ | AC | -Buck Conv. & Unfolder

• Temporary PWM Operation of Unfolder @  $U < U_{min}$  to Avoid AC Current Distortion

- CM Component of Output Voltage  $v_o$

- Larger EMI Filtering Requirement Due to Temporary High-Frequ. Switching of Unfolder

# **Full-Bridge AC/DC Conv. Topology**

- Example of (Bidirectional) 1-⊕ Telecom Boost-Type PFC Rectifier

- Low-Frequency Operation of One Bridge Leg Interleaving for High Part Load Efficiency Si Superjunction MOSFETs

72W/in³ (4.5kW/dm³) incl. Holdup Capacitors @ 98.6%

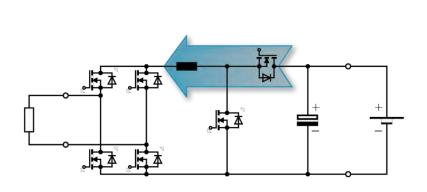

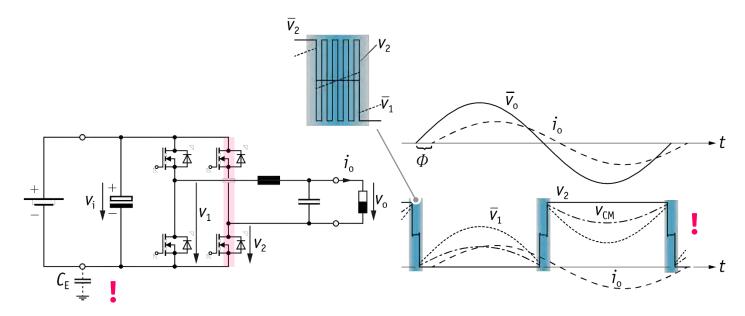

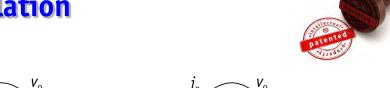

# **Advanced Full-Bridge DC/AC Conv. Topology**

• New Control Concept - PWM Operation of Mains Freq. Bridge Leg @  $|u| < u_{0,min}$

- CM Component u<sub>CM</sub> of Generated Output Voltage

Potentially Larger EMI Filtering Requirement

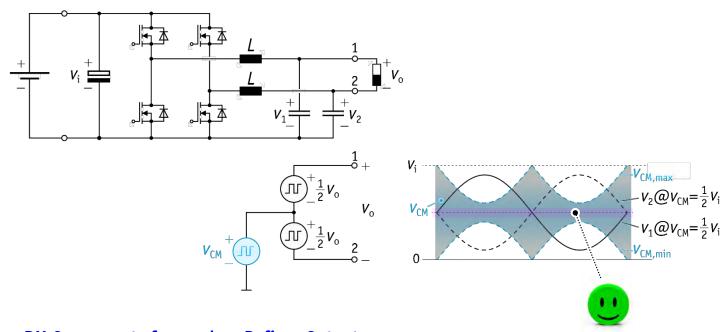

# Symmetric PWM Full-Bridge AC/DC Conv. Topology

- Symmetric PWM Operation of Both Bridge Legs

- No Low-Frequency CM Output Voltage Component

- DM Component of  $u_1$  and  $u_2$  Defines Output  $u_0$  CM Component of  $u_1$  and  $u_2$  Represents Degree of Freedom of the Modulation (!)

#### **Remark: AC Side Power Pulsation Buffer**

- Full Bridge Output Stage / Full PWM Operation

- CM Reactive Power of Output Filter Capacitors used for Comp. of Load Power Pulsation

- CM Reactive Power prop. 2 C DM Reactive Power prop. ½ C

# **ZVS** of Output Stage / TCM Operation

Henze (1988)

• TCM Operation for Resonant Voltage Transition @ Turn-On/Turn-Off

- Requires Only Measurement of Current Zero Crossings, i = 0 Variable Switching Frequency Lowers EMI

# **CM-Enhanced TCM Modulation**

- CM Comp. of u<sub>1</sub>, u<sub>2</sub> Changes Sw. Frequency

Limits Sw. Frequency Variation

Lower Sw. Losses

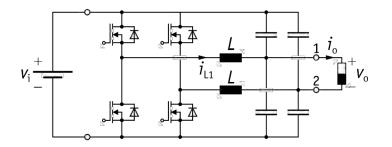

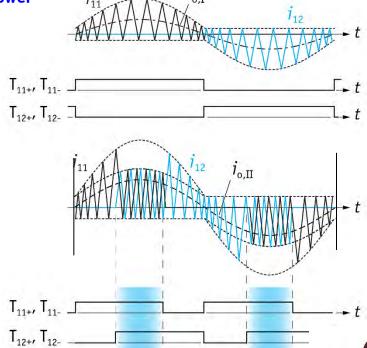

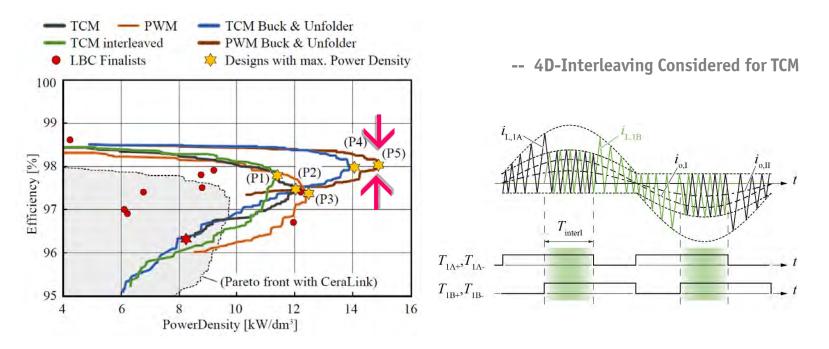

# **4D-Interleaving**

- Interleaving of 2 Bridge Legs per Phase Volume / Filtering / Efficiency Optimum

- Interleaving in Space & Time Within Output Period

Alternate Operation of Bridge Legs @ Low Power

Overlapping Operation @ High Power

Opt. Trade-Off of Conduction & Switching Losses / Opt. Distribution of Losses

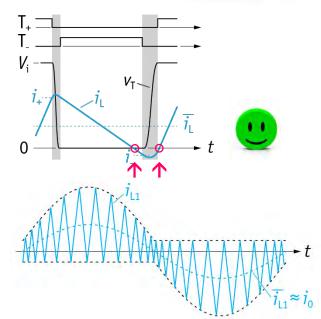

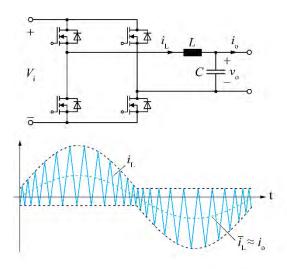

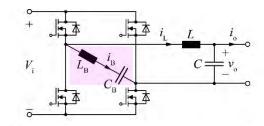

#### **Remark: iTCM Inverter Topology**

- TCM: Challenging Inductor Design → Superposition of HF & LF Currents

- iTCM: Adding LC-Circuit between Bridge Legs  $\rightarrow$  Separation of LF & HF Currents  $\rightarrow L >> L_{\rm R}$

#### - TCM

#### - iTCM

- **Low Output Current Ripple**

- **PWM Modulation Applicable**

- **Dedicated LF and HF Inductor Designs Possible** → **Improved Converter Efficiency**

- → Reduced Filtering Effort

- → Simple Control Strategy

# **Selection of Switching Frequency**

• Significant Reduction in EMI Filter Volume for Increasing Sw. Frequency

- Doubling Sw. Fequ.  $f_s$  Cuts Filter Volume in Half Upper Limit due to Digital Signal Processing Delays / Inductor & Sw. Losses Heatsink Volume

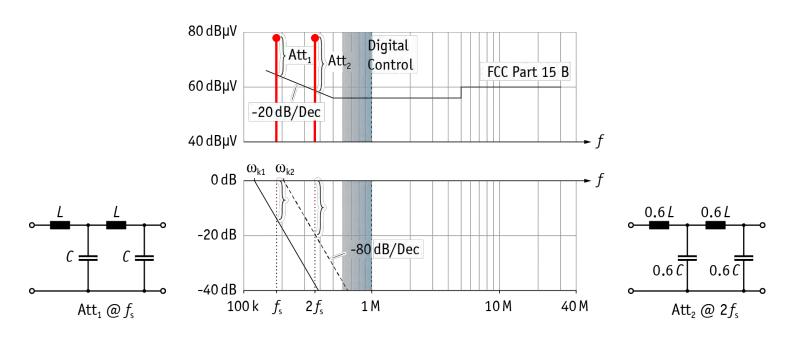

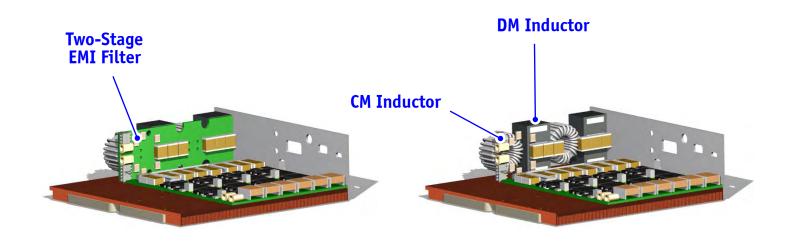

# **EMI Filter Topology (1)**

- Conventional Filter Structure

- DM Filtering Between the Phases

- CM Filtering Between Phases and PE

- CM Cap. Limited by Earth Current Limit Typ. 3.5mA for PFC Rectifiers (GLBC: 5mA then 50mA!)

- Large CM Inductor Needed Filter Volume Mainly Defined by CM Inductors

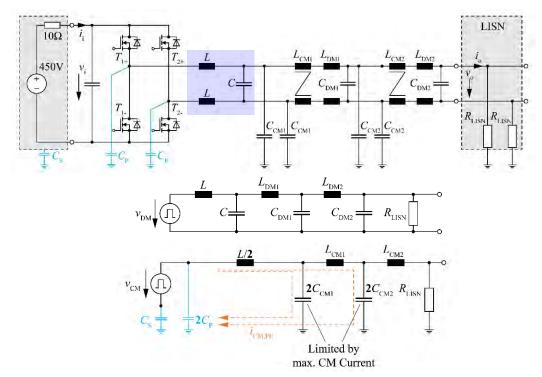

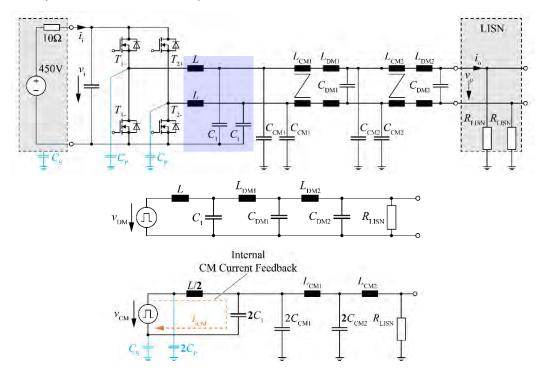

# **EMI Filter Topology (2)**

- Filter Structure with Internal CM Capacitor Feedback

- Filtering to DC- (and optional to DC+)

- No Limitation of CM Capacitor  $C_1$  Due to Earth Current Limit  $\rightarrow \mu F$  Instead of nF Can be Employed Allows Downsizing of CM Inductor and/or Total Filter Volume

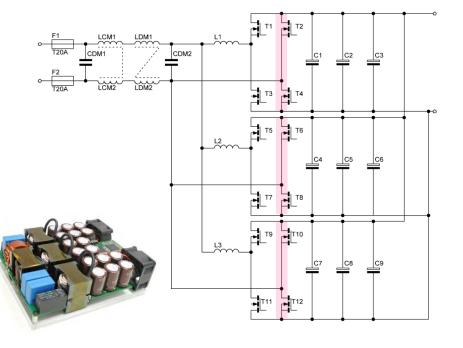

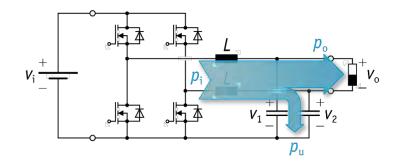

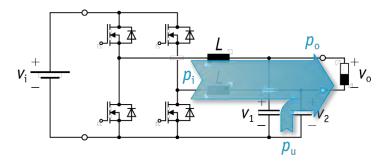

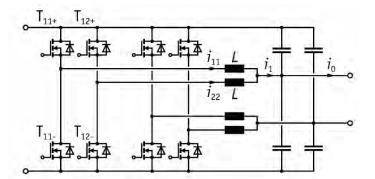

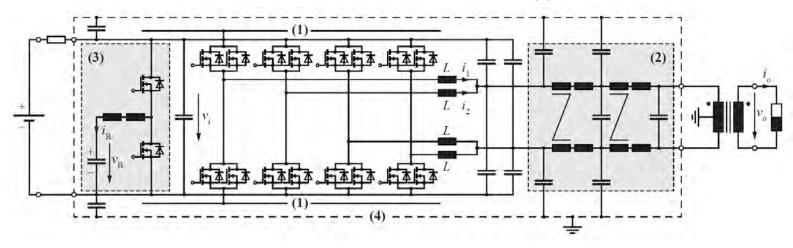

## **Final Converter Topology**

- Interleaving of 2 Bridge Legs per Phase

- Active DC-Side Buck-Type Power Pulsation Buffer

- 2-Stage EMI AC Output Filter

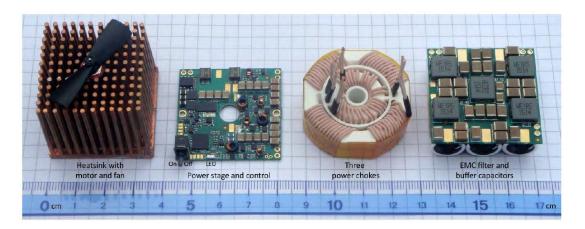

- (1) Heat Sink

- (2) EMI Filter

- (3) Power Pulsation Buffer

- (4) Enclosure

- ZVS of All Bridge Legs @ Turn-On/Turn-Off in Whole Operating Range (4D-TCM-Interleaving)

- Heatsinks Connected to DC Bus / Shield to Prevent Cap. Coupling to Grounded Enclosure

# **Technologies**

Power Semiconductors

Cooling

DSP/FPGA

Auxiliary

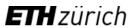

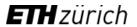

# **Evaluation of Power Semiconductors (1)**

- Accurate Measurement of ZVS Losses Using Calorimetric Approach

- High Sw. Frequency for Large Ratio of Sw. and Conduction Losses

- Direct Measurement of the Sum of Sw. and Conduction Losses

- Subtraction of the Conduction Losses Known from Calibration

- Fast Measurement by  $C_{th}$ . $\Delta T/\Delta t$  Evaluation

# **Evaluation of Power Semiconductors (2)**

- Comparison of Soft-Switching Performance of  $\sim$ 60m $\Omega$ , 600V/650V/900V GaN, SiC, Si MOSFETs

- Measurement of Energy Loss per Switch and Switching Period

- GaN MOSFETs Feature Highest Soft-Switching Performance

- Similar Soft-Switching Performance Achieved with Si and SiC

- Almost No Voltage-Dependency of Soft-Switching Losses for Si-MOSFET

#### **Selected Power Semiconductors**

- 600V IFX Normally-Off GaN GIT ThinPAK8x8

2 Parallel Transistors / Switch

- Antiparallel CREE SiC Schottky Diodes

- 1.2V typ. Gate Threshold Voltage 55 m $\Omega$   $R_{\rm DS,qn}$  @ 25°C, 120m $\Omega$  @ 150°C 5 $\Omega$  Internal Gate Resistance

$dv/dt = 500kV/\mu s$

**■** CeraLink Capacitors for DC Voltage Buffering

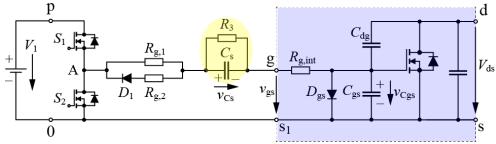

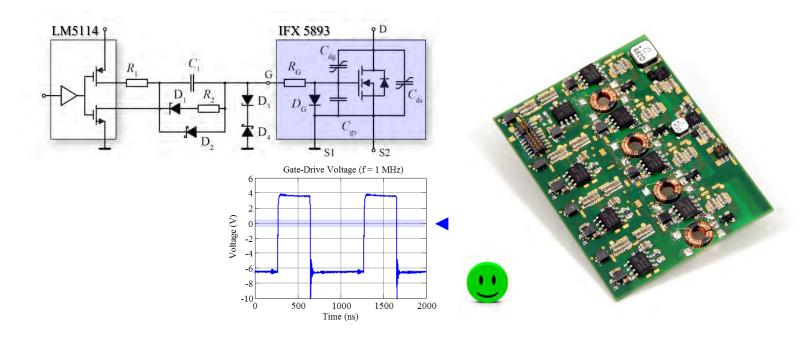

#### **High dv/dt-Immunity Gate Drive**

- Low Threshold-Voltage of GaN GIT Devices → Negative Gate Voltage During Off-State Needed

- Internal Diode Characteristic

- → Gate Current Limitation During On-State Needed

- State-of-the-Art Gate Drive with Additional RC-Circuit

-  $C_s$  Enables High Gate Current for Fast Turn-On

-  $R_3$  Discharges  $C_s$  During Off-State

- Duty Cycle and Frequency Dependent Gate Voltage

- Risk of Parasitic Turn-on Due to Switching of Complementary Switch

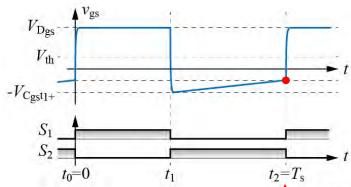

### **High dv/dt-Immunity Gate Drive**

- **Improved Gate Drive Circuit with RC-Circuit and Added Clamping Diodes**

- High Current for Fast Turn-On as Conventional Approach

- Diode **ZD**<sub>1</sub> Prevents **C**<sub>5</sub> from Complete Discharge **During Off-State**

#### Final Advanced Gate Drive

- Fixed Negative Turn-off Gate Voltage Independent of Sw. Frequency and Duty Cycle

- Extreme dv/dt Immunity (500 kV/µs) Due to CM Choke at Signal Isolator Input

■ Total Prop. Delay < 30ns incl. Signal Isolator, Gate Drive, and Switch Turn-On Delay

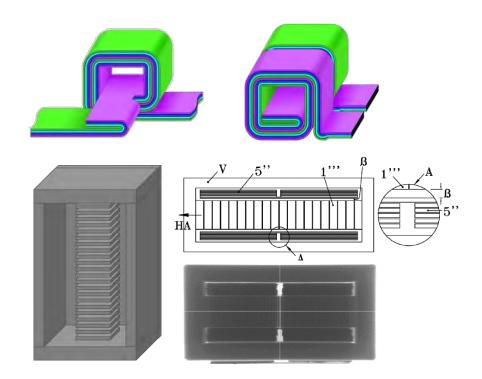

### **High Frequency Inductors (1)**

- Multi-Airgap Inductor with Multi-Layer Foil Winding Arrangement Minim. Prox. Effect

- Very High Filling Factor / Low High Frequency Losses Magnetically Shielded Construction Minimizing EMI Intellectual Property of F. Zajc / Fraza

- L= 10.5µH

- 2 x 8 Turns

- 24 x 80µm Airgaps Core Material DMR 51 / Hengdian 0.61mm Thick Stacked Plates

- 20 μm Copper Foil / 4 in Parallel

7 μm Kapton Layer Isolation

20mΩ Winding Resistance / Q≈600

Terminals in No-Leakage Flux Area

■ Dimensions - 14.5 x 14.5 x 22mm<sup>3</sup>

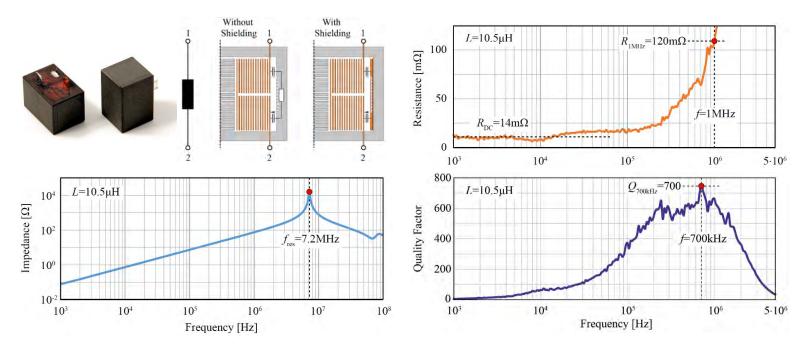

## **High Frequency Inductors (2)**

- High Resonance Frequency → Inductive Behavior up to High Frequencies

Extremely Low AC-Resistance → Low Conduction Losses up to High Frequencies

- High Quality Factor

- **Shielding** Eliminates HF Current through the Ferrite → Avoids High Core Losses

- Shielding Increases the Parasitic Capacitance

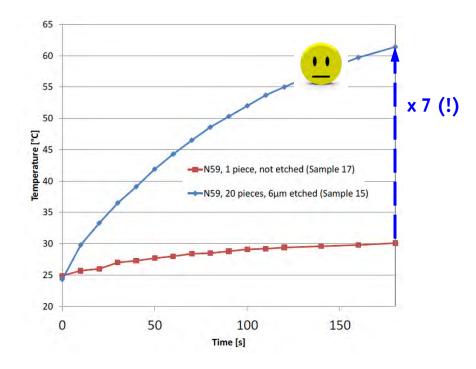

#### **High Frequency Inductors (3)**

**Knowles (1975!)**

- **Cutting of Ferrite Introduces Mech. Stress**

- Significant Increase of the Loss Factor Reduction by Polishing / Etching (5 μm)

■ Comparison of Temp. Increase of a Bulk and a Sliced Sample @ 70mT / 800kHz

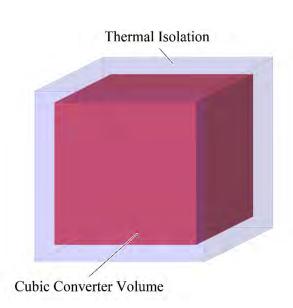

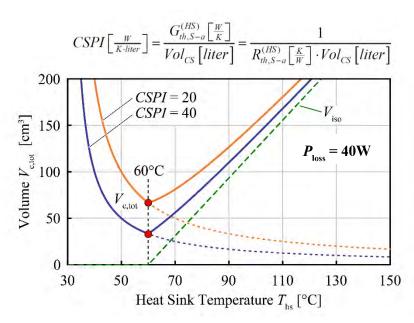

#### **Thermal Management**

- 30°C max. Ambient Temperature

60°C max. Allowed Surface and Air Outlet Temperature

- **Evaluation of Optimum Heatsink Temperature for Thermal Isolation of Converter**

Minimum Volume Achieved w/o Thermal Isolation with Heatsink @ max. Allowed Surface Temp.

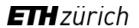

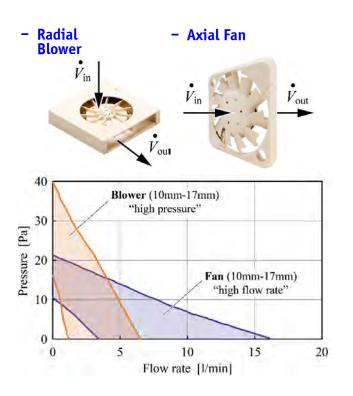

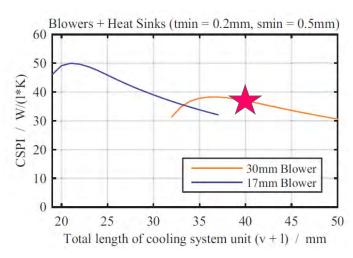

#### **Thermal Management**

• Overall Cooling Performance Defined by Selected Fan Type and Heatsink

- Optimal Fan and Heat Sink Configuration Defined by Total Cooling System Length

- Cooling Concept with Blower Selected → Higher CSPI for Larger Mounting Surface

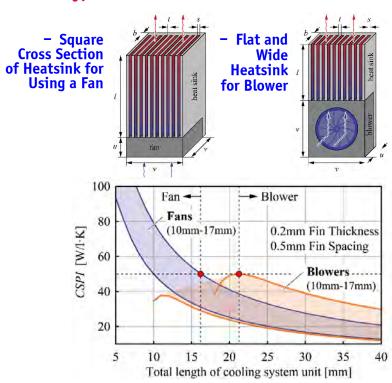

#### Final Thermal Management Concept (1)

- 30mm Blowers with Axial Air Intake / Radial Outlet

- **Full Optimization of the Heatsink Parameters**

- 200um Fin Thickness

- 500um Fin Spacing

- 3mm Fin Height

- 10mm Fin Length

- CSPI = 37 W/(dm<sup>3</sup>.K) 1.5mm Baseplate

- CSPI<sub>eff</sub>= 25 W/(dm³.K) Considering Heat Distribution Elements

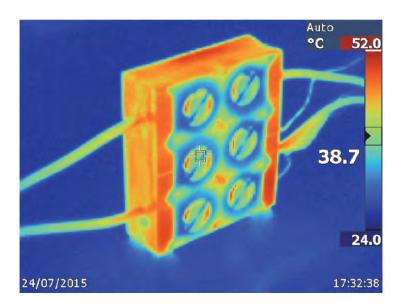

Two-Side Cooling → Heatsink Temperature = 52°C @ 80W (8W by Natural Convection)

#### Final Thermal Management Concept (2)

- CSPI = 37 W/(dm<sup>3</sup>.K) 30mm Blowers with Axial Air Intake / Radial Outlet Full Optimization of the Heatsink Parameters CSPI<sub>eff</sub>=25 W/(dm<sup>3</sup>.K) incl. Heat Cond. Layers

- CSPI<sub>eff</sub> = 25 W/(dm³.K) Considering Heat Distribution Elements

Two-Side Cooling → Heatsink Temperature = 52°C @ 80W (8W by Natural Convection)

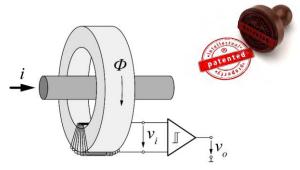

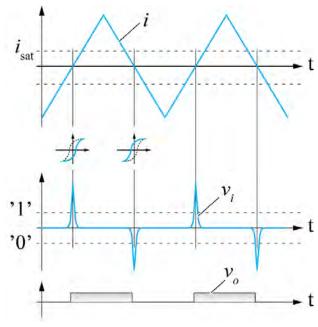

#### i=0 Detection

- **Analyzed Methods**

- Shunt Current Measurement

- Measurement of the R<sub>ds,on</sub>

Two Antiparallel Diodes

- Giant Magneto-Resistive Sensor

- Hall Element

- Saturable Inductor

#### **Various Drawbacks**

**Losses, No Galvanic Isolation,** Low Signal-to-Noise Ratio (SNR), Size, Bandwidth, Realization **Effort**

- Saturable Inductor Toroidal Core R4 x 2.4 x 1.6, EPCOS (4mm Diameter)

Core Material N30, EPCOS

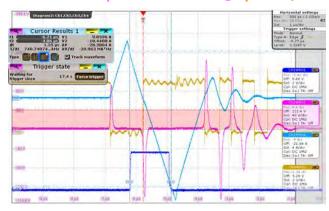

- Res: 500 ps / 2 GSa/s 1 µs/div Trigger settings de: Normal Φ Type-A: Edge

Ch1

Offset: -7.36 µs

Level: 1.2966 V Auto °C 109.0 Off: 12.8 V Cpl: DC 1MΩ Dec: Sa | TA: Off 96.4 Digital Signal  $\nu_{o}$ Pos: -1.44 div Off: -244 mA Induced Voltage Vi Scl: 2 A/div Cpl: DC 1MΩ Dec:Sa | TA: Off Current i Off: 64.8 V Scl: 40 V/div Cpl: DC 1MΩ Dec: Sa | TA: Off -120 V 21.0 -7 µs -4 µs -3 µs

■ Operation Tested up to 2.5MHz Switching Frequency

#### Control Board & i=0 Detection

- Fully Digital Control Overall Control Sampling Frequency of 25kHz TI DSC TMS320F28335 / 150MHz / 179-pin BGA / 12mm x 12mm Lattice FPGA LFXP2-5E / 200MHz / 86-pin BGA / 8mm x 8mm

- TCM Current / Induced Voltage / Comparator Output

- i=0 Detection of TCM Currents Using R4/N30 Saturable Inductors

Galv. Isolated / Operates up to 2.5MHz Switching Frequency / <10ns Delay</li>

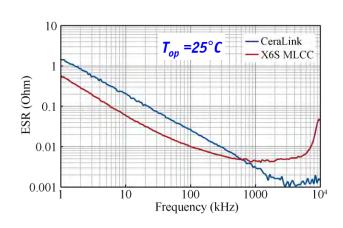

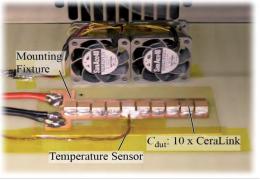

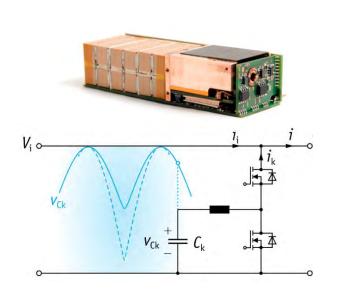

### **Active Power Pulsation Buffer Capacitor (1)**

- Electrolytic Capacitors Limited by Lifetime-Relevant Current Limit

2.2μF, 450 V Class II X6S MLCC Highest Energy Density but Cap. Decreases with DC Bias

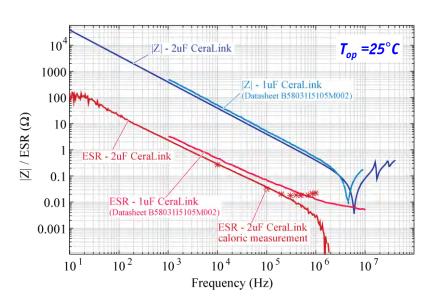

- Novel 1 μF /2 μF, 650 V CeraLink™ Cap. (PLZT Ceramic) Features High Cap. @ High DC Bias

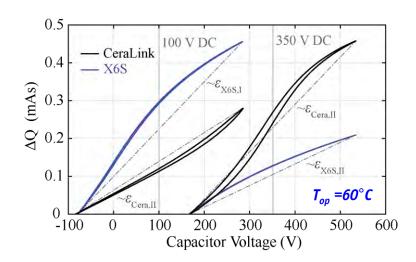

- Allows 125 C Operating Temp. & Shows Very Low ESR @ High Frequencies

- **CeraLink Resonance Frequency at Several MHz**

- Small-Signal ESR of CeraLink in MHz Frequ. Range Sign. Lower Comp. to X6S MLCC

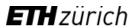

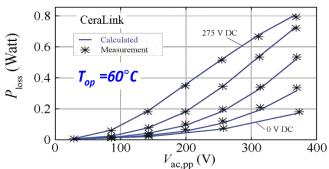

#### **Active Power Pulsation Buffer Capacitor (2)**

- CeraLink

- Large-Signal Excitation with 2xLine-Frequ. Reveals Large Hysteresis

- Significantly Higher Losses @ 2xLine-Frequ. Comp. to X6S MLCC

ESR Drops Significantly @ Higher Temperatures

36μF (27μF) Blocks of Prepackaged Single Chips

- Reliable Mech. Construction

- X6S MMLC

- Only Available as Single Chips

- Complicated Packaging

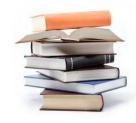

#### **Final Active Power Pulsation Buffer**

- High Energy Density 2<sup>nd</sup> Gen. 400VDC CeraLink Capacitors Utilized as Energy Storage

- Highly Non-Linear Behavior → Optimal DC Bias Voltage of 280VDC

- Losses of 6W @ 2kVA Output Power

- 108 x 1.2µF /400 V 23.7cm³ Capacitor Volume

■ Effective Large Signal Capacitance of C ≈160µF

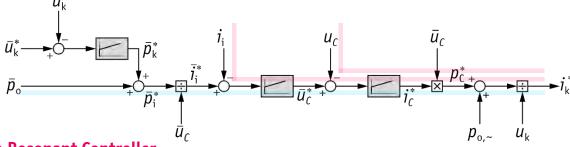

#### **Active Power Pulsation Buffer Control (1)**

New Cascaded Control Structure

- **P-Type Resonant Controller**

- **■** Feedforward of Output Power Fluctuation

- Underlying Input Current  $(i_i)$  / DC Link Voltage  $(u_c)$  Control

#### **Active Power Pulsation Buffer Control (2)**

Multiple Controller Outputs Combined in a Single Current Reference

- Regulation of Mean Buffer Voltage (Bias Voltage)

- Tight Control of Inverter DC Link Voltage also During Transients

- Active Power Decoupling Rejection of 2xLine-Frequ. Ripple in Inverter DC Input Voltage

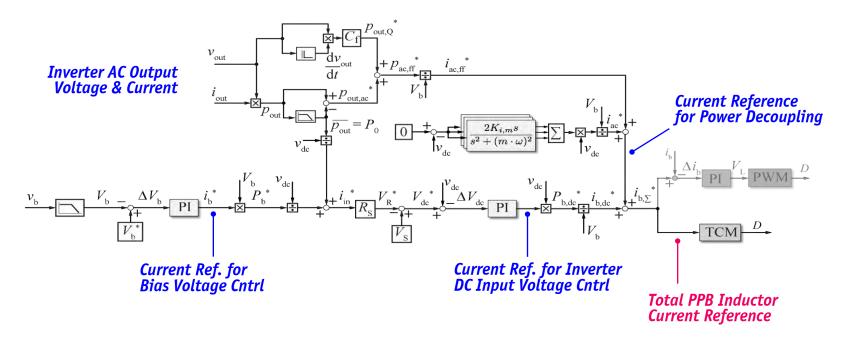

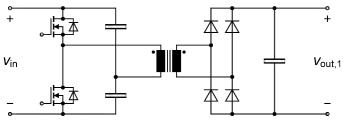

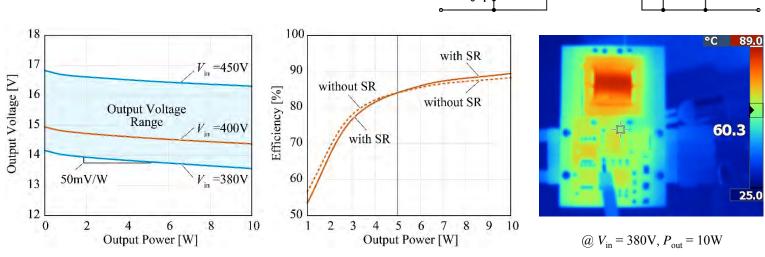

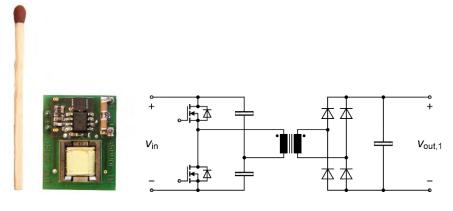

#### **Auxiliary Supply**

- Constant 50% Duty Cycle Half Bridge w. Diode Rect. or Synchr. Rectification (SR)

- ZVS → Compact / Efficient / Low EMI

■ Only Marginal Eff. Gain with Synchr. Rectification for Output Power Levels > 5W

### **Auxiliary Supply & Measurement Circuits**

- Constant 50% Duty Cycle Half Bridge with Synchr. Rectification

- ZVS  $\rightarrow$  Compact / Efficient / Low EMI ( $f_s$ =465 kHz)

- 10W Max. Output Power

390V...450V Input Operating Range

13.8V...16.8V DC Output in Full Inp. Voltage / Output Power Range

- 90% Efficiency @ P<sub>max</sub>

19mm x 24mm x 4.5mm (2cm<sup>3</sup> Volume)

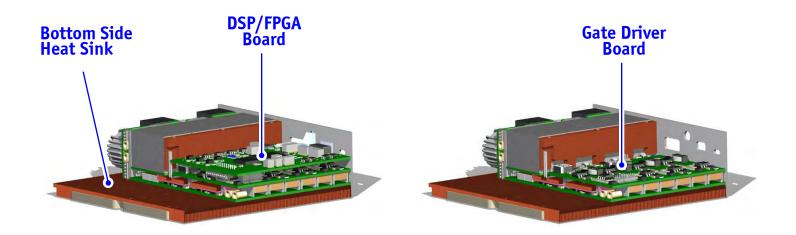

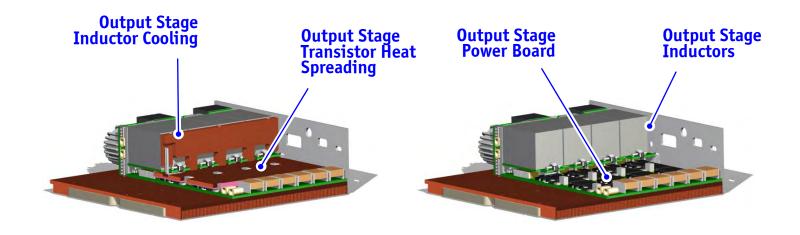

3D-CAD Construction \_\_\_\_\_

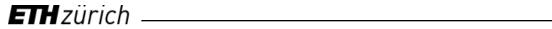

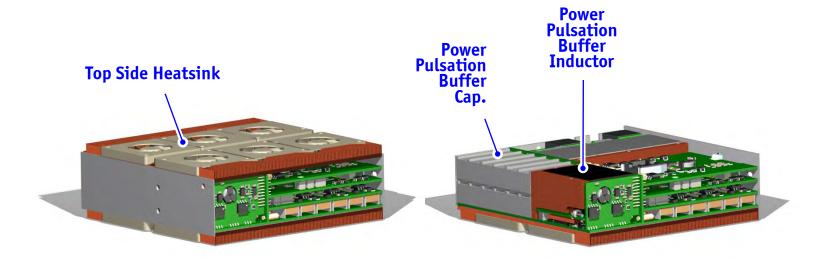

#### **Mechanical Construction (1)**

• Built to the Power Density Limit @  $\eta = 95\% / T_c < 60$ °C

#### **Mechanical Construction (2)**

• Built to the Power Density Limit @  $\eta$ = 95% /  $T_c$  < 60°C

#### **Mechanical Construction (3)**

• Built to the Power Density Limit @  $\eta$ = 95% /  $T_c$  < 60°C

#### **Mechanical Construction (4)**

• Built to the Power Density Limit @  $\eta$ = 95% /  $T_c$  < 60°C

■ 88.7mm x 88.4mm x 31mm = 243cm<sup>3</sup> (14.8in<sup>3</sup>) → 8.2 kW/dm<sup>3</sup>

## ٠

#### Mechanical Construction (5)

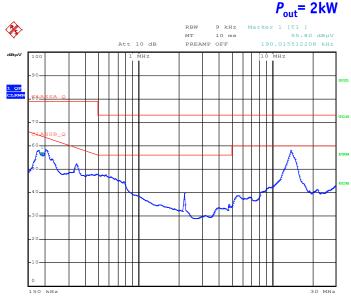

#### **Experimental Results**

Hardware

Output Voltage/Input Current Quality

Thermal Behavior

Efficiency

EMI

# Little Box 1.0 - Prototype I

• System Employing Electrolytic Capacitors as 1-⊕ Power Pulsation Buffer

```

273cm<sup>3</sup>

7.3 kW/dm<sup>3</sup>

97,5% Efficiency @ 2kW

T<sub>c</sub>=58°C @ 2kW

```

$\Delta u_{\rm DC} = 2.85\%$   $\Delta i_{\rm DC} = 15.4\%$   $THD + N_U = 2.6\%$  $THD + N_I = 1.9\%$

97mm x 90.8 mm x 31mm (16.6in<sup>3</sup>)

**■ Compliant to All Specifications**

## •

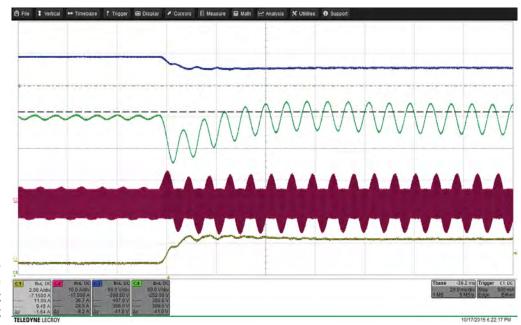

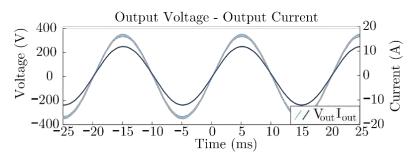

#### Little Box 1.0-I Measurement Results (1)

• System Employing Electrolytic Capacitors as 1-⊕ Power Pulsation Buffer

Ohmic Load / 2kW

DC Input Current DC Voltage Ripple Output Voltage Output Current

**■** Compliant to All Specifications

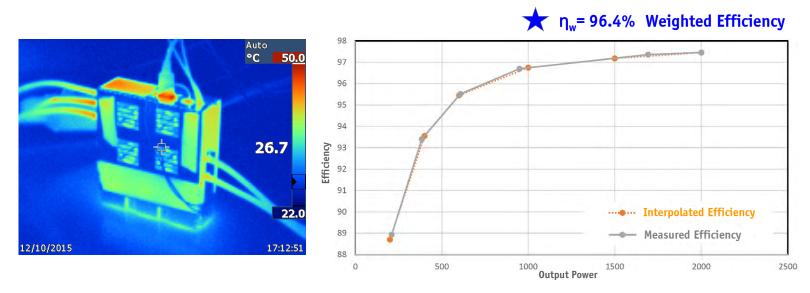

## Little Box 1.0-I Measurement Results (2)

• System Employing Electrolytic Capacitors as 1-⊕ Power Pulsation Buffer

■ Heating of System Lower than Specified Limit (T<sub>C,max</sub>= 60°C @ T<sub>amb</sub>= 30°C)

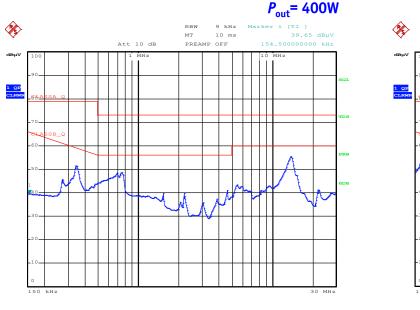

## Little Box 1.0-I Measurement Results (3)

• System Employing Electrolytic Capacitors as 1-⊕ Power Pulsation Buffer

1.JAN.2000 02:19:31

■ Compliant to All Specifications

**ETH** zürich

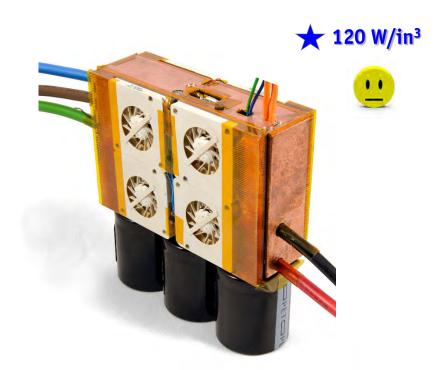

#### **Little Box 1.0 - Prototype II (Final)**

System Employing Active 1-Ф Power Pulsation Buffer

- 8.2 kW/dm<sup>3</sup>

- 8.9cm x 8.8cm x 3.1cm

- 96,3% Efficiency @ 2kW

- T<sub>c</sub>=58°C @ 2kW

- $\Delta u_{\rm DC} = 1.1\%$

- $-\Delta i_{DC} = 2.8\%$   $-THD+N_U = 2.6\%$   $-THD+N_I = 1.9\%$

- **Compliant to All** *Original* **Specifications** (!)

- No Low-Frequ. CM Output Voltage Component

- No Overstressing of Components

- All Own IP / Patents

#### **Little Box 1.0 - Prototype II (Final)**

System Employing Active 1-⊕ Power Pulsation Buffer

- 8.2 kW/dm<sup>3</sup>

- 8.9cm x 8.8cm x 3.1cm

- 96,3% Efficiency @ 2kW

- $-T_c=58^{\circ}$ C @ 2kW

- $\Delta u_{\rm DC}$ = 1.1%  $\Delta i_{\rm DC}$ = 2.8%  $THD+N_U$ = 2.6%  $THD+N_I$ = 1.9%

- **Compliant to All** *Original* **Specifications** (!)

- No Low-Frequ. CM Output Voltage Component

- No Overstressing of Components

- All Own IP / Patents

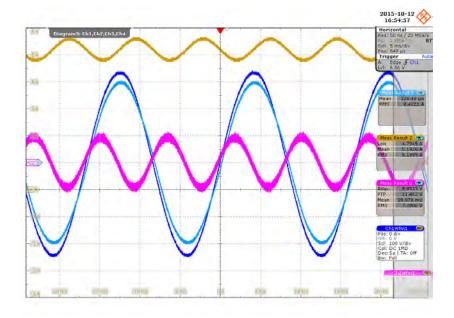

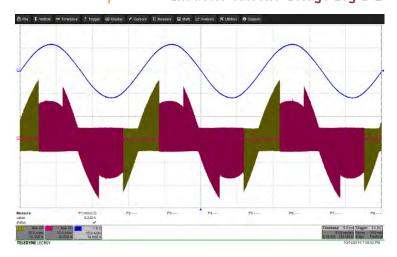

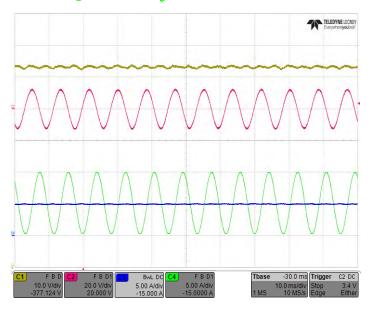

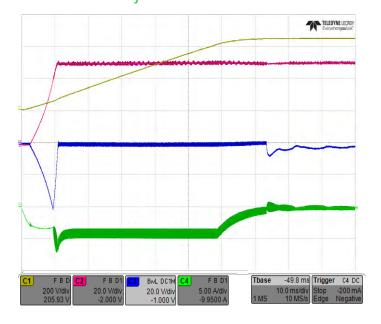

#### Little Box 1.0-II Measurement Results (1)

• System Employing Active 1-⊕ Power Pulsation Buffer

Output Current

Inductor Current Bridge Leg 1-1

- Ohmic Load / 2kW Inductor Current Bridge Leg 1-2

DC Link Voltage (AC-Coupl.)

Buffer Cap. Voltage

Buffer Cap. Current

Output Voltage

**■ Compliant to All Specifications**

## Little Box 1.0-II Measurement Results (2)

• System Employing Active 1-⊕ Power Pulsation Buffer

**■ Compliant to All Specifications**

# •

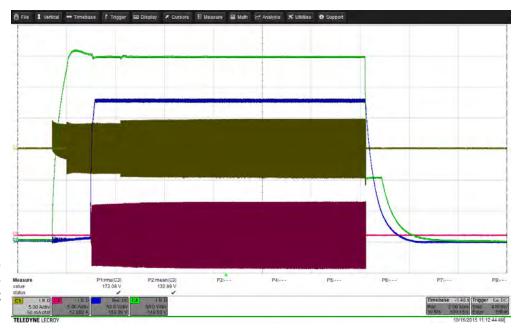

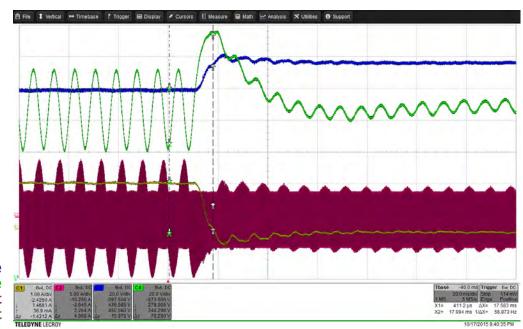

# Little Box 1.0-II Measurement Results (3)

• System Employing Active 1-⊕ Power Pulsation Buffer

DC Link Voltage Buffer Cap. Voltage Buffer Cap. Current Inductor Current Bridge Leg 1-1

■ Start-up and Shut-Down (No Load Operation)

# Little Box 1.0-II Measurement Results (4)

System Employing Active 1-⊕ Power Pulsation Buffer

Buffer Cap. Voltage Buffer Cap. Current Converter Input Current (AC Coupled) DC Link Voltage (AC Coupled)

■ Stationary Operation @ 2kW Output Power

# Little Box 1.0-II Measurement Results (5)

System Employing Active 1-⊕ Power Pulsation Buffer

DC Link Voltage Buffer Cap. Voltage Buffer Cap. Current Converter Input Current

■ Transient Response for Load-Step of 0 Watt → 700 Watt

# Little Box 1.0-II Measurement Results (6)

System Employing Active 1-⊕ Power Pulsation Buffer

DC Link Voltage Buffer Cap. Voltage Buffer Cap. Current Converter Input Current

■ Transient Response for Load-Step of 700 Watt → 0 Watt

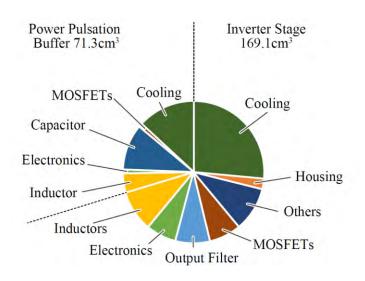

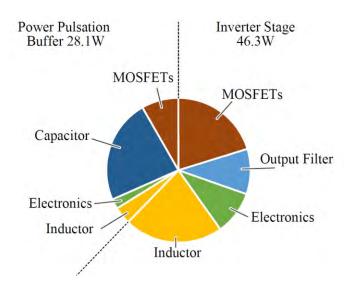

#### Little Box 1.0-II Volume and Loss Distribution

**Volume Distribution (240cm³)**

**Loss Distribution (75W)**

- Large Heatsink (incl. Heat Conduction Layers)

- Large Losses in Power Fluctuation Buffer Capacitor (!)

- TCM Causes Relatively High Conduction & Switching Losses @ Low Power

Relatively Low Switching Frequency @ High Power Determines EMI Filter Volume

#### Other Finalists

Topologies Switching Frequencies Power Density / Efficiency Comparison

Detailed Descriptions: www.littleBoxChallenge.com

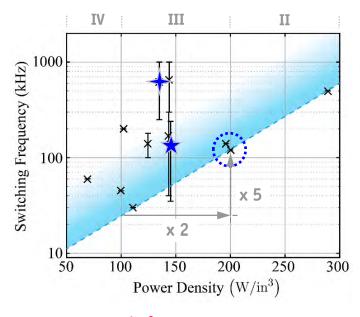

#### **Finalists - Performance Overview**

- 18 Finalists (3 No-Shows)

7 Groups of Consultants / 7 Companies / 4 Universities

- 70...300 W/in<sup>3</sup>

- 35 kHz...500kHz...1 MHz (up to 1MHz: 3 Teams)

- Full-Bridge or DC/|AC|Buck Converter + Unfolder

- Mostly Buck-Type Active Power Pulsation Filters (Ceramic Caps of Electrolytic Caps)

- GaN (11 Teams) / SiC (2 Teams) / Si (2 Teams)

#### **Finalists - Performance Overview**

- 18 Finalists (3 No-Shows)

7 Groups of Consultants / 7 Companies / 4 Universities

- 70...300 W/in<sup>3</sup>

- 35 kHz...500kHz...1 MHz (up to 1MHz: 3 Teams)

- Full-Bridge or DC/|AC|Buck Converter + Unfolder

- Mostly Buck-Type Active Power Pulsation Filters (Ceramic Caps of Electrolytic Caps)

- GaN (11 Teams) / SiC (2 Teams) / Si (2 Teams)

#### **Category I: 300 - 400 W/in³ (1 Team)**

- "Over the Edge"

- Hand-Wound Overstressed & Too Small Electrolytic Capacitors (210uF/400V)

- No Voltage Margin of Power Semiconductors (450V GaN, Hard Switching)

- 50V Voltage Source for Semicond. Voltage Stress Reduction

- Low-Frequ. CM AC Output Component

- Alternate Switching of Full-Bridge Legs

- Input Cap. of Full-Bridge Used for Power Pulsation Buffering

- 256 W/in<sup>3</sup> (400 W/in<sup>3</sup> Claimed) / 1MHz

- Multi-Airgap Toroidal Inductors (3F46,  $C_n \approx 1.5 \text{pF}$ )

- Bare Dies Directly Attached to Pin-Fin Heatsink

- High Speed Fan (Mini Drone Motor & Propeller)

#### **Category I: 300 - 400 W/in³ (1 Team)**

- "Over the Edge"

- Hand-Wound Overstressed Electrolytic Capacitors (210uF (?)/400V)

- No Voltage Margin of Power Semiconductors (450V GaN, Hard Switching)

- 50V Voltage Source for Semicond. Voltage Stress Reduction

- Alternate Switching of Full-Bridge Legs

- Input Cap. of Full-Bridge Used for Power Pulsation Buffering

- 256 W/in<sup>3</sup> (400 W/in<sup>3</sup> Claimed) / 1MHz

- Multi-Airgap Toroidal Inductors (3F46,  $C_p \approx 1.5 \text{pF}$ )

- Bare Dies Directly Attached to Pin-Fin Heatsink

- High Speed Fan (Mini Drone Motor & Propeller)

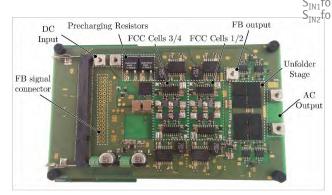

## Category II: 200 - 300 W/in<sup>3</sup> (4 Teams) - Example #1

- "At the Edge"

- High Complexity

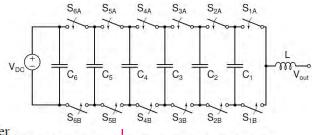

- 7-Level Flying Capacitor Converter

- Series-Stacked Active Power Buffer

- 216 W/in<sup>3</sup>

- 100V ĠaN

- Integrated Switching Cell

- 720kHz Eff. Sw. Frequ. (7 x 120kHz)

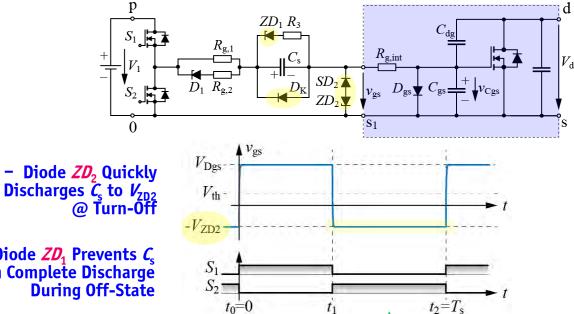

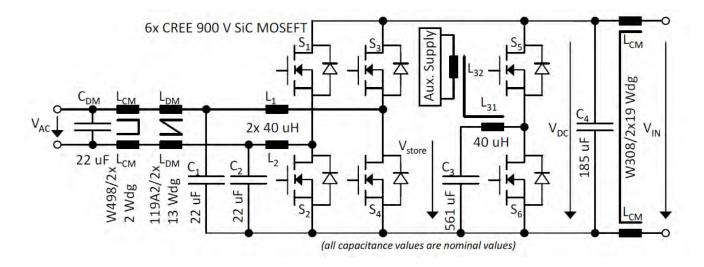

#### Category II: 200 - 300 W/in<sup>3</sup> (4 Teams) - Example #2

- "At the Edge"

- Very Well Engineered Assembly (e.g. 3D-Printed Heatsink w. Integr. Fans, 1 PCB Board, etc.)

- No Low-Frequ. Common-Mode AC Output Component

- 201W / in<sup>3</sup>

- Multi-Airgap (8 Gaps) Inductors

- 900V SiC @ 140kHz (PWM, Soft & Hard Switching)

- Buck-Type Active DC-Side Power Pulsation Filter / Ceramic Capacitors (X6S)

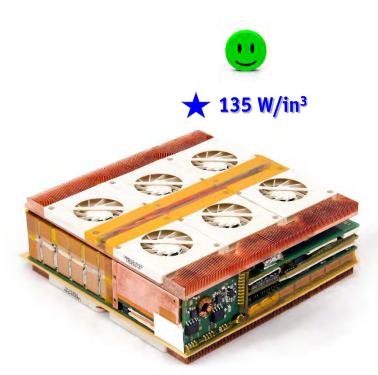

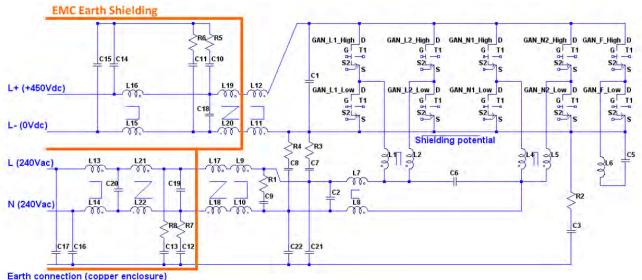

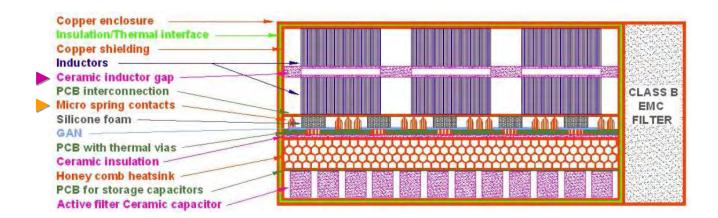

#### Category III: 100 - 200 W/in<sup>3</sup> (8 Teams) - Example

- "Advanced Industrial"

- Sophisticated 3D Sandwich Assembly incl. Cu Honeycomb Heatsink

- Shielded Multi-Stage EMI Filter @ DC Input and AC Output

- No Low-Frequ. Common-Mode AC Output Component

- 143 W/in³

- GaN @ ZVS (35kHz...240kHz)

- 2 x Interleaving for Full-Bridge Legs

- Buck-Type DC-Side Active Power Pulsation Filter (<150µF)

#### Category III: 100 - 200 W/in<sup>3</sup> (8 Teams) - Example

- "Advanced Industrial"

- Sophisticated 3D Sandwich Assembly incl. Cu Honeycomb Heatsink

- Shielded Multi-Stage EMI Filter @ DC Input and AC Output

- No Low-Frequ. Common-Mode AC Output Component

- 143 W/in<sup>3</sup>

- GaN @ ZVS (35kHz...240kHz)

- 2 x Interleaving for Full-Bridge Legs

Buck-Type DC-Side Active Power Pulsation Filter (<150µF)</li>

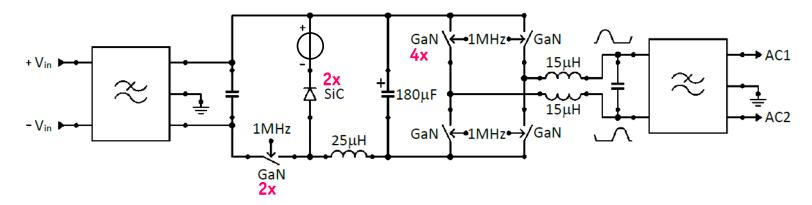

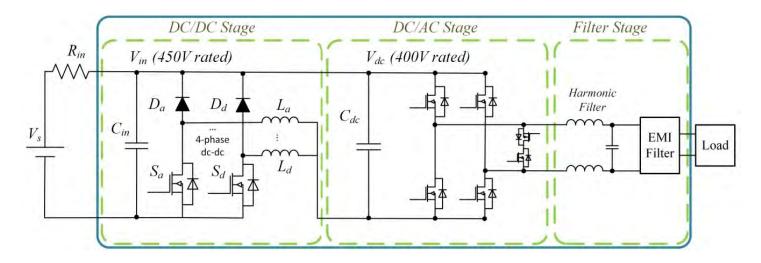

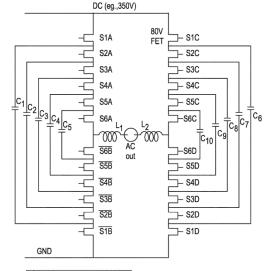

#### **Category IV:** 50 - 100 W/in<sup>3</sup> (1 Team)

- "Industrial"

- 400V<sub>max</sub> Full-Bridge Input Voltage

DC-Link Cap. Used as Power Pulsation Buffer (470uF)

- GaN Transistors / SiC Diodes (400kHz DC/DC, 60kHz DC/AC)

- Multi-Stage EMI Filter @ AC Output and  $L_{CM}$  + Feed-Trough  $C_{CM}$  @ DC Inp. (Not Shown)

- ≈70 W/ in<sup>3</sup>

- 98% CEC Efficiency

- 4.4% DC Input Current Ripple

- 54°C Surface Temp. / Cooling with 10 Mirco-Fans

# CompetitionConclusions

Key Technologies Power Density Limit

# Google Little Box Challenge Summary

#### Overall

- Engineering "Jewels"

- No (Fundamentally) New Approach / Topology

- Passives & 3D-Packaging are Finally Defining the Power Density

- Careful Heat Management (Adv. Heat Sink, Heat Distrib., 2-Side Integr. Cooling, etc.)

- Careful Mechanical Design (3D-CAD, Single PCB, Avoid Connectors, etc.)

- Clear Power Density / Efficiency Trade-Off

#### ■ 200W/in<sup>3</sup> (12kW/dm<sup>3</sup>) System

- f<sub>s</sub> < 150kHz (Constant)

- SiC (Not GaN)

- ZVS (Partial)

- Full-Bridge Output Stage

- Active Power Pulsation Buffer (Buck-Type, X6S Cap.)

- Conv. EMI Filter Structure

- Multi-Airgap Litz Wire Inductors

- DSP Only (No FPGA)

100+ Teams 3 Members / Team, 1 Year 300 Man-Years 3300 USD / Man-Year

# Analysis of Advanced Concepts & Technologies

X6S Capacitors Series Power Pulsation Buffer Optimal Frequency Modulation Flying Cap. Converter Topology Autotrafo-Based Inverter

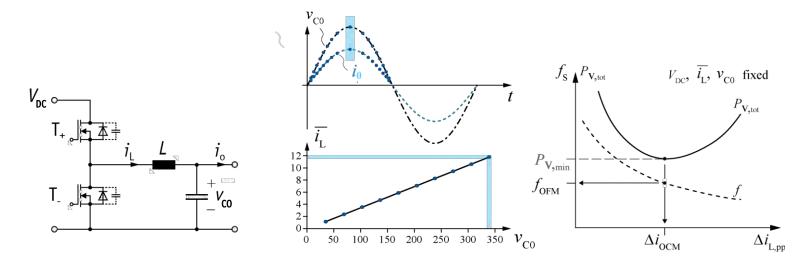

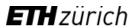

## Eff. Optimal Frequ. / Current-Ampl. Modulation (1)

- TCM -- Enables ZVS but Suffers From Large Current Ripple & Wide Frequency Variation

- PWM -- Const. Sw. Frequency but Hard Switching Around AC Current Maximum

- Optimal Combination of TCM and PWM  $\rightarrow$  Optim. Frequ. / Curr. Ripple Variation Over Mains Period

- Experimental Determination of Loss-Opt. Sw. Frequency  $f_{\rm OFM}$  Considering DC/DC Conv. Stage DC/AC Properties Calculated Assuming Corresponding Local DC/DC Operation

■ Loss-Optimal Local Sw. Frequ.  $f_{OEM}$  for Given  $V_{DC}$  & Local Avg. Value of  $i_1$  & Local Outp. Cap. Voltage  $v_{CO}$

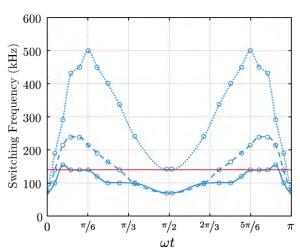

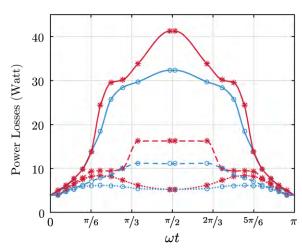

# Eff. Optimal Frequ. / Current-Ampl. Modulation (2)

- Calculated Optimal Sw. Frequ. & Power Loss as Function of the Position in a Mains Half Cycle

- Comparison with 140 kHz Const. Frequency PWM

- Higher Average Switching Frequency @ Light Loads

- **Reduction** of  $f_{sw}$  Around Peak of Mains Voltage (for Ohmic Load) in Order to Sustain ZVS

# •

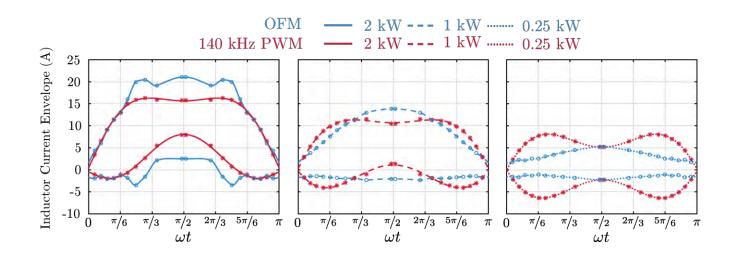

## Eff. Optimal Frequ. / Current-Ampl. Modulation (3)

Resulting Inductor Current Envelope for Different Output Power Levels

- Higher Average Switching Frequency @ Light Loads

- Reduction of  $f_{sw}$  Around Peak of Mains Voltage (for Ohmic Load) in Order to Sustain ZVS

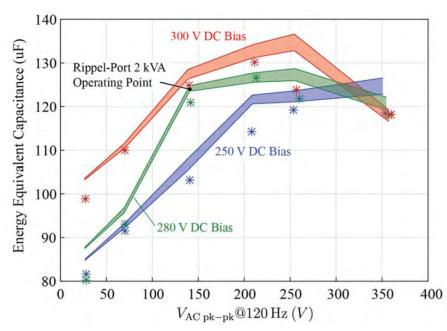

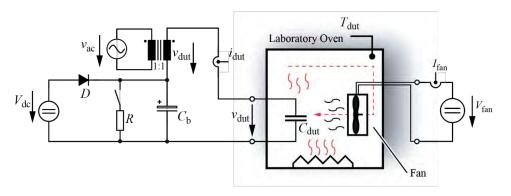

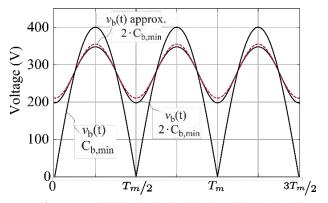

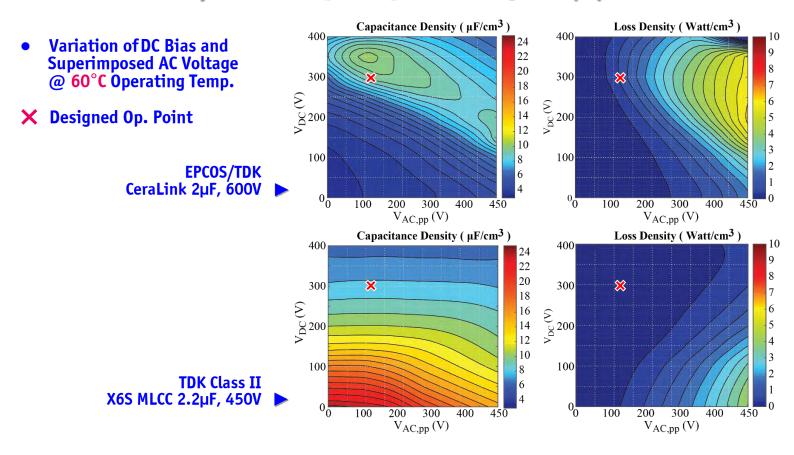

## CeraLink / X6S Large-Signal Analysis (1)

- 2.2 µF/450V Class II X6S MLCC (TDKs) Features Highest Energy Density Performance Comparison with Novel CeraLink Capacitor

Experimental Setup for Generation of **DC Bias & Superimposed AC Voltage**

PPB Design Optimiz. Requires Large-Signal Capacitance and Power Loss Data in All Operating Points

# ٠

## CeraLink / X6S Large-Signal Analysis (2)

■ PPB Design Optimiz. Requires Large-Signal Capacitance and Power Loss Data in All Operating Points

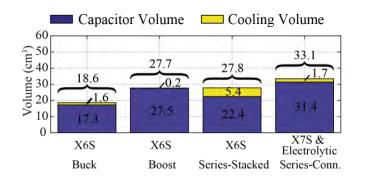

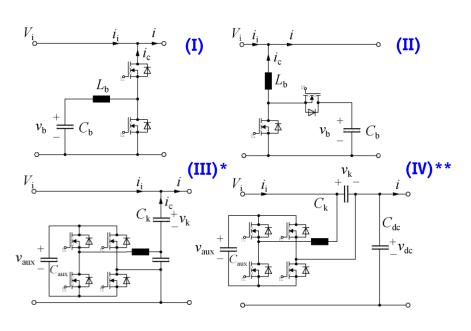

## Power Pulsation Buffer - Partial-Power Approach (1)

- Performance Comparison of Full-Power and Partial-Power Power Pulsation Buffer (PPB) Concepts

- Hybrid Approach (IV) Employs Red. Size Electrolytic DC-Link Cap. and Series-Conn. Partial-Power PPB

- Capacitor Volumes are Incl. Heatsink Vol. for Loss Dissipation ( $CSPI_{eff}$  = 25 W/(dm<sup>3</sup>.K))

- (IIÍ) Partial-Power Series-Stacked

- (IV) Partial-Power Series-Connected

■ Buck-Type PPB Realized with 2.2µF/450 V X6S MLCC Features Smallest Cap. Volume

\*Pilawa \*\* Schneider Electric

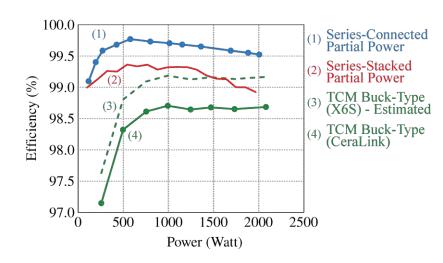

# **Power Pulsation Buffer – Partial-Power Approach (2)**

- Performance Comparison of Full-Power and Partial-Power Power Pulsation Buffer (PPB) Concepts

- Partial-Power Concepts Feature Higher Efficiency Especially @ Light Load

**Buck-Type** with CeraLink  $Vol. = 76.6 \text{ cm}^3$

Series-Conn. **Partial-Power**  $Vol. = 57.31 \text{ cm}^3$

$\eta = 99.5 \%$

■ Peak Efficiency of 99.75% Reached with Series-Connected PPB @ 600 Watt

■ Part-Load Efficiency of Buck-Type PPB **Expected to be Higher with PWM**

Series-Stacked **Partial-Power\*** Vol.= 80 cm<sup>3</sup>  $\eta = 98.9 \%$

\*Pilawa

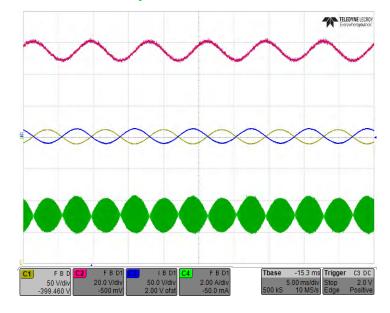

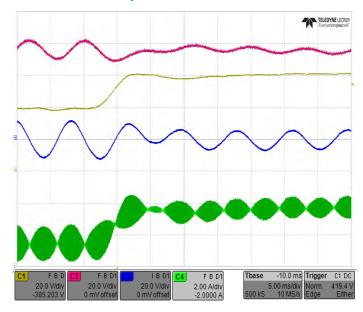

#### **Performance of Series-Type Partial-Power PPB (1)**

■ Stationary Operation @ Rated Power of 2 kW

```

Input Voltage, v_i

Filter Voltage, v_f

Input Current, i_i

Pulsating Current, i_o

```

Buffer Voltage,  $v_{buf}$  DC-Link Voltage,  $v_{dc}$  Filter Voltage,  $v_f$  Filter Current,  $i_f$

# Performance of Series-Type Partial-Power PPB (2)

Buffer Voltage,  $v_{buf}$  DC-Link Voltage,  $v_{dc}$  Filter Voltage,  $v_f$  Filter Current,  $i_f$

Startup of the Converter

■ Load Step 2kW → 1kW

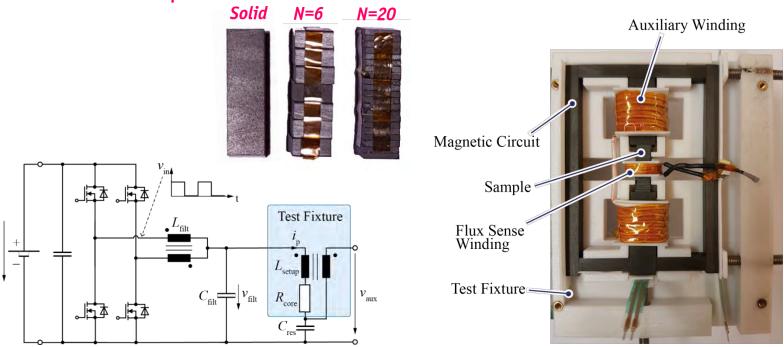

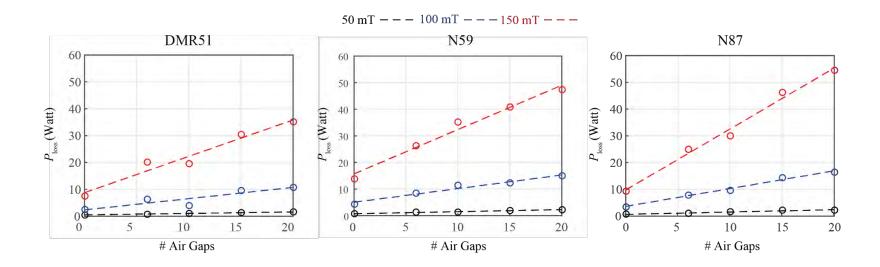

#### **Multi-Airgap Inductor Core Loss Measurements (1)**

- Investigated Materials DMR51, N87, N59

30 µm PET Foil with Double Sided Adhesive Between the Plates

Varying Number N of Air Gaps Assembled from Thin Ferrite Plates

- **Number of Air Gaps:**

Sinusoidal Excitation with Frequencies in the Range of 250 kHz ...1MHz

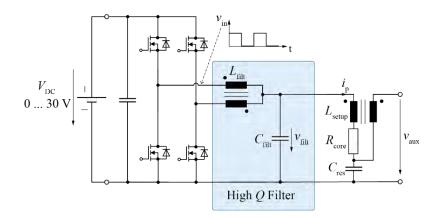

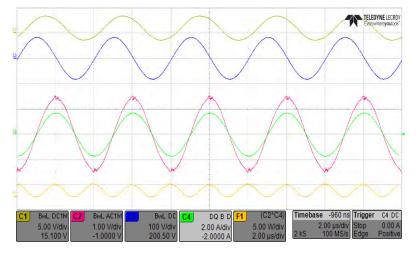

# **Multi-Airgap Inductor Core Loss Measurements (2)**

- High-Q Low-Pass Filtering of 50% Duty Cycle Volt. Ensures Sinus. Excitation

Operation @ Resonance for High Measurement Accuracy

No Phase Displacement of Sensed Voltage and Current

- Flux Density Adjusted by Input Voltage Level

\* Mu (2015)

# **Multi-Airgap Inductor Core Loss Measurements (3)**

- Total Core Loss in Sample with Varying Air Gaps and Test Fixture

- Excitation @ 500 kHz

- Losses Increase Linearly with the Number of Introduced Air Gaps

- Conclusion -- Surface Layers Deteriorated by Machining of Ferrite

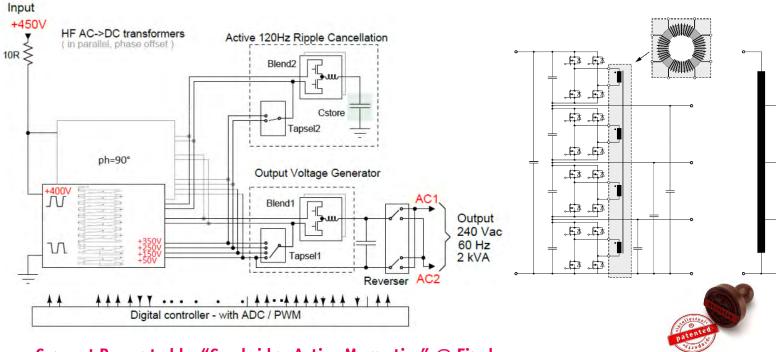

#### **Sw. Frequ. Auto-Transformer Approach**

- Multi-Tap Switching Frequ. Multi-Air-Gap Autotransformer Realizing a Multi-Tap Voltage Divider

- Tap Switch & Series Active Filter for Gen. of Sinus. Output Voltage from Multi-Step Waveform

- Low-Voltage Power Semiconductors

- Concept Presented by "Cambridge Active Magnetics" @ Final

- Power Density Unclear (Presentation @ Final: 159W/in³, 290W/in³ Shown as Target in Report)

- Efficiency Unclear (10W of Losses @ 2kW in Documentation, Equal to Only  $R = 150 \text{m}\Omega$  in Total?)

#### Multi-Tapped Sw. Frequ. Auto-Transformer (1)

DC-AC-DC

DC-AC

- (I) Resonant ZVS Half-Bridge

- (IÍ) Multi-Tapped Auto-Transf.

- (IIÍ) Voltage-Doubler Rectifier

- (IV) PWM Tap-Selector

- (V) Output Filter

- (VÍ) Full-Bridge Unfolder

#### Multi-Tapped Sw. Frequ. Auto-Transformer (2)

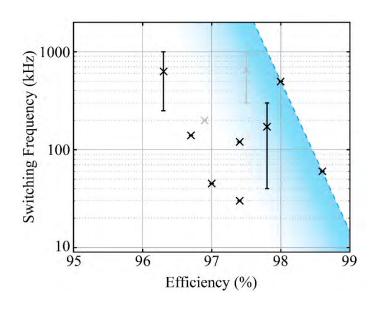

ηρ-Pareto Optimization of the Converter System

Efficiency

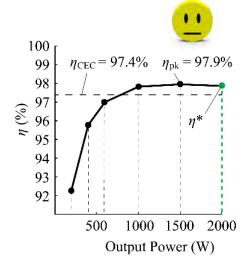

Power Density

97.7% @ 2kW (97.4% CEC)

120W/in³ (7.4kW/dm³)

99 \( \text{\gamma} \text{\*} \) 98 \( \text{\gamma} \text{\*} \) 97 \( \text{\gamma} \text{\gamma} \) 96 \( \text{\*} \text{\*} \) 96

$\rho$  (kW/dm<sup>3</sup>)

Efficiency of Resonant Multi-Level DC/DC Stage > 99%

7  $\rho^*$

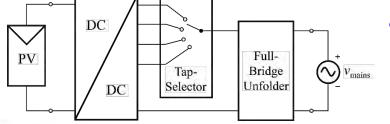

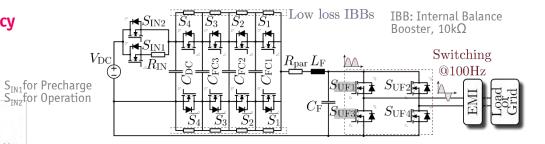

#### **Multi-Level Converter Approach**

- Multi-Level PWM Output Voltage Minimizes Ind. Volume Flying Cap. Conv. No Splitting of DC Inp. Voltage Required Low-Voltage GaN or Si Power Semiconductors

Multi-level inverter

(12)

EP 2 779 410 A2

**EUROPEAN PATENT APPLICATION**

(51) Int Cl.: 17.09.2014 Bulletin 2014/38 H02M 7/483 (2007.01) (21) Application number: 14159869.8 (22) Date of filing: 14.03.2014 (71) Applicant Solaredge Technologies Ltd. (84) Designated Contracting States: 45240 Hod Hasharon (IL) AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR (72) Inventor: Yoscovitch, Ilan Designated Extension States: 45240 Hod Hasharon (IL) BA ME (74) Representative: Jansen, Cornelis Marinus et al (30) Priority: 14.03.2013 US 201313826556 V.O. Johan de Wittlaan 7 2517 JR Den Haag (NL)

Full-Bridge Topology or DC/|AC|Buck-Type + Unfolder

FIG. 1

Basic Patent on FCC Converter – Th. Meynard (1991)! FIG. 4

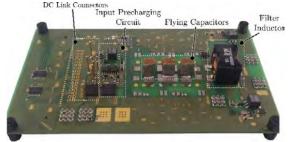

#### Multi-Level Conv. Approach - Flying Cap. Conv. (1)

- **5 Voltage Levels**

- 320 kHz Single-Cell Sw. Frequency

- 12µF Flying Capacitors Improved Phase-Shift PWM

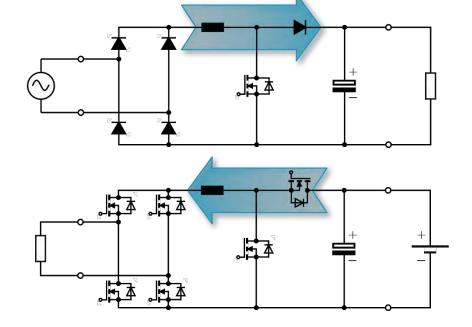

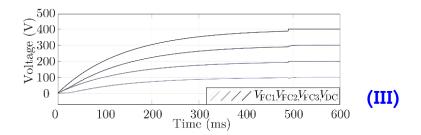

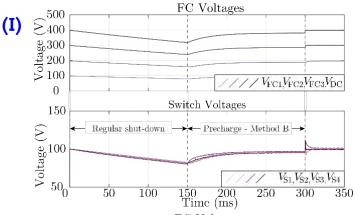

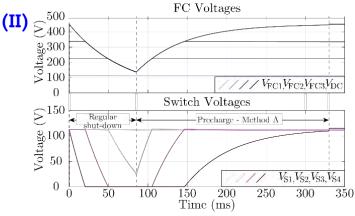

#### Multi-Level Conv. Approach - Flying Cap. Conv. (2)

- Analysis of Symmetry of FC Voltages During Start-Up, Shut-Down, Stand-By, Output S.C. Missing

- Inverter & Rectifier Operation

- (I) Rectifier Operation No Load, PWM Disabled @ t=0, FCs Discharging over Balance Resistors, Voltage Symmetry Maintained, PWM Re-Enabled @ t=150ms, U<sub>out</sub> Control @ t=300ms

- (II) Rectifier Operation Under Load, Loss of Mains or PWM Disabled (Load Still Present), FCs Discharging over Diodes Voltage Unbalance, Bridge Leg Re-Enabled @ t=150ms, Dedicated Control Procedure Requ. for Regaining FC Volt. Symmetry

- (III) Inverter Operation Start-Up form DC-Side, Pre-Charge Resistors Bridged @ t=500ms

# Optimization of Little-Box 1.0

ηρ-Pareto Front TCM vs. Large Ripple PMW The Ideal Switch is Not Enough (!) Design Space Diversity

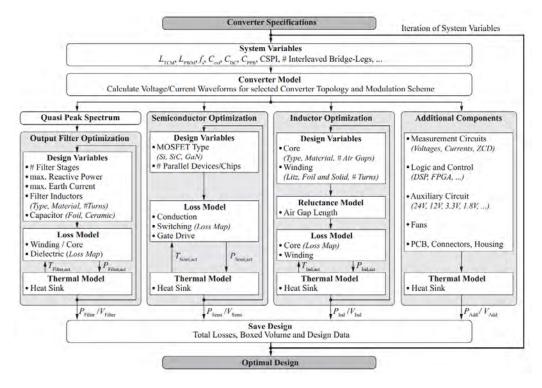

### **Multi-Objective Optimization**

- Detailed System Models Power Buffer/Output Stage/EMI Filter

Detailed Multi-Domain Component Models (incl. GaN & SiC)

Consideration of Very Large # of Degrees of Freedom

■ Pareto Optimization Shows Trade-Off Between Power Density and Efficiency

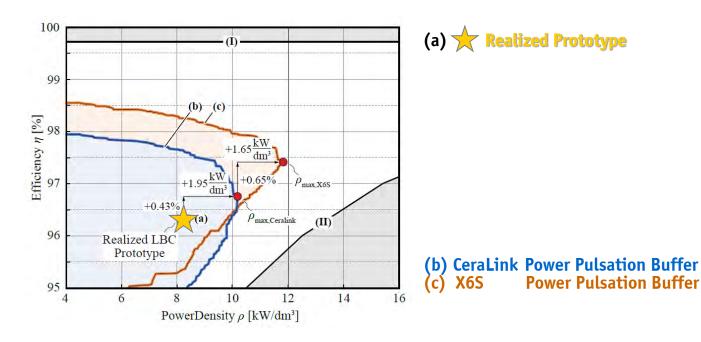

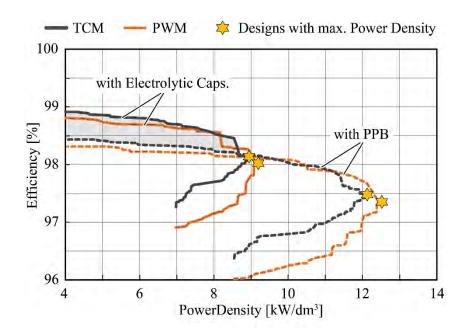

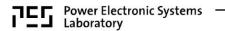

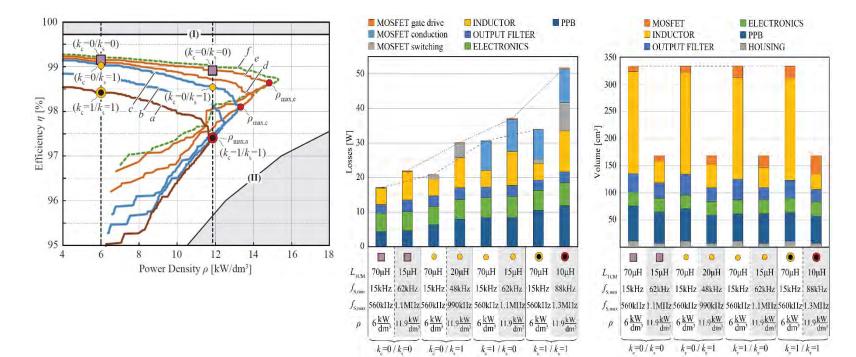

### **Little Box 1.0 ηρ-Performance Limits**

- Multi-Objective Optimization of Little-Box 1.0 (incl. CeraLink  $\rightarrow$  X6S) Absolute Performance Limits (I) DSP/FPGA Power Consumption (II) Heatsink Volume @ (1- $\eta$ )

■ Further Performance Improvement for Triangular Current Mode (TCM) → PWM

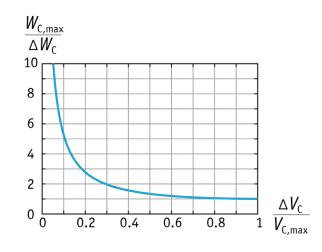

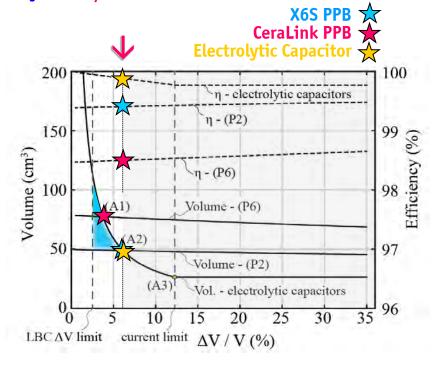

### Power Pulsation Buffer (PPB) vs. Electrolytic Capacitor (1)

• Lower Volume Comp. to Electrolytic Caps only for  $\Delta V/V < 6\%$

No Efficiency Benefit of PPB (!)

- Electrolytics Favorable for High Efficiency @ Moderate Power Density

- Electrolytics Show Lower Vol. & Lower Losses if Large  $\triangle V/V$  is Acceptable (e.g. for PFC Rectifiers)

## Power Pulsation Buffer (PPB) vs. Electrolytic Capacitor (2)

- Analysis for Google Little Box Challenge Specification ΔV/V < 3%</li>

Efficiency Benefit of PPB only for ρ > 9kW/dm³

- Electrolytics Favorable for High Efficiency @ Moderate Power Density ( $\Delta \eta$ = +0.5%)

- Electrolytics Show Lower Vol. & Lower Losses if Large △V/V is Acceptable (e.g. for PFC Rectifiers)

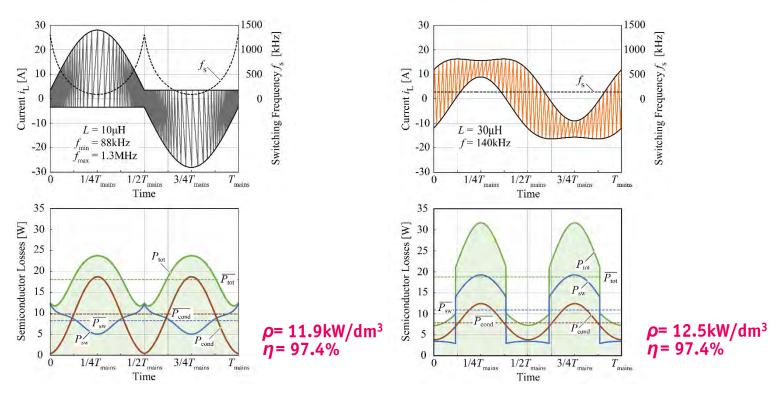

### Little Box 1.0 -- TCM $\rightarrow$ PWM

- Very High Sw. Frequency  $f_s$  of TCM Around Current Zero Crossings

- Efficiency Reduction due to Remaining TCM Sw. Losses & Gate Drive Losses Reduction

- Wide  $f_s$  -Variation Represents Adv. & Disadvantage for EMI Filter Design

- PWM -- Const. Sw. Frequency & Lower Conduction Losses

- PWM @ Large Current Rippel -- ZVS in Wide Intervals

### Little Box 1.0 -- TCM $\rightarrow$ PWM

- Optimization for GaN GIT & No Interleaving Resulting Opt. Inductance of Output Inductor  $L=10\mu H$  (TCM),  $L=30\mu H$  (PWM)

■ PWM vs. TCM -- Slightly Higher Max. Power Density @ Same Efficiency

The Ideal Switch is Not Enough (!)

### **Little Box 1.0 @ Ideal Switches**

- Multi-Objective Optimization of Little-Box 1.0 (X6S Power Pulsation Buffer)

- Step-by-Step Idealization of the Power Transistors

- Ideal Switches:  $k_c = 0$  (Zero Cond. Losses);  $k_s = 0$  (Zero Sw. Losses)

■ Analysis of Improvement of Efficiency @ Given Power Density & Maximum Power Density

### **Little Box 1.0 @ Ideal Switches -- TCM**

- $\Delta \eta$  = + 0.5% @  $\rho$  = 6kW/dm<sup>3</sup> Main Benefit from Zero Conduction Losses ( $k_c$ =0)  $\Delta \eta$  = +1.5% @  $\rho$  = 12kW/dm<sup>3</sup> Add. Benefit from Zero Sw. Losses ( $k_s$ = $k_c$ =0)

- Minor Improvement of Max. Power Density  $\rho$ = 12kW/dm³  $\rightarrow$  15kW/dm³ (PPB Cap. & Inductors) Finite Remaining Volume & Losses  $\rightarrow$  The Ideal Switch is Not Enough (!)

### Little Box 1.0 @ Ideal Switches -- PWM

- $\Delta \eta$  = + 1.0% @  $\rho$  = 6kW/dm<sup>3</sup> Benefit from Zero Cond. & Zero Sw. Losses ( $k_S$  =  $k_C$  = 0)  $\Delta \eta$  = +1.75% @  $\rho$  = 12kW/dm<sup>3</sup> Benefit from Zero Cond. & Zero Sw. Losses ( $k_S$  =  $k_C$  = 0)

- 50% Improvement of Max. Power Density ρ= 12kW/dm³ → 19kW/dm³ (PPB & Inductors)

Finite Remaining Volume & Losses → The Ideal Switch is Not Enough (!)

### Little Box 1.0 @ Ideal Switches -- PWM

- $L \& f_S$  are Independent Variables (Dependent for TCM)

Large Design Space Diversity (Mutual Compensation of HF and LF Loss Contributions)

# Little Box 2.0

DC/ AC Converter + Unfolder

PWM vs. TCM incl. Interleaving

ηρ-Pareto Limits for Non-Ideal Switches

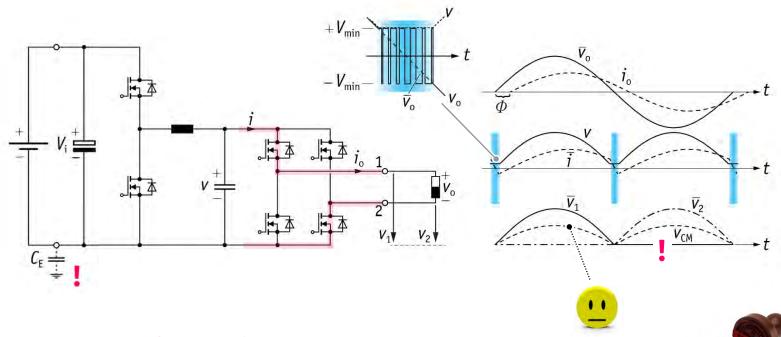

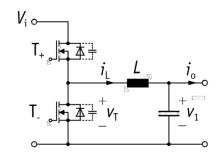

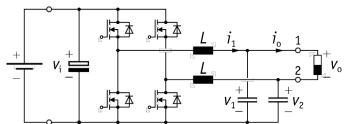

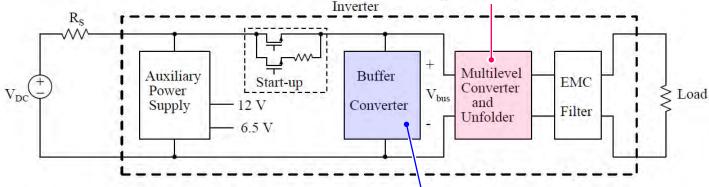

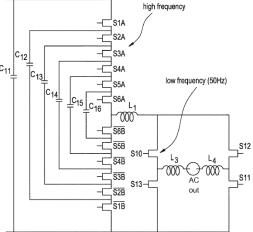

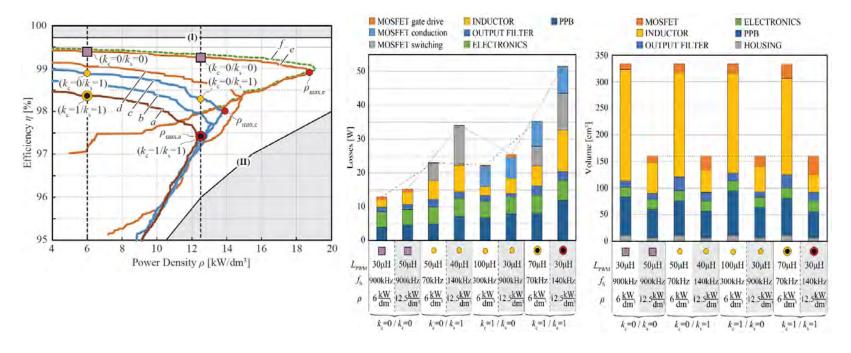

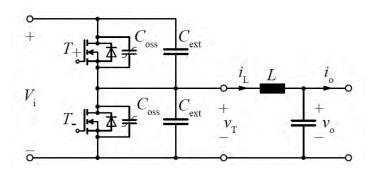

### **Little Box 2.0 – New Converter Topology**

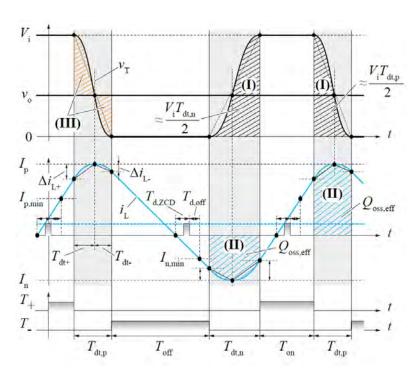

- Alternative Converter Topology DC/ | AC | Buck Converter + Unfolder 60Hz-Unfolder (Temporary PWM for Ensuring Continuous Current Control) TCM or PWM of DC/ | AC | Buck-Converter

■ Full Optimization of All Converter Options for Real Switches / X6S Power Pulsation Buffer

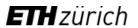

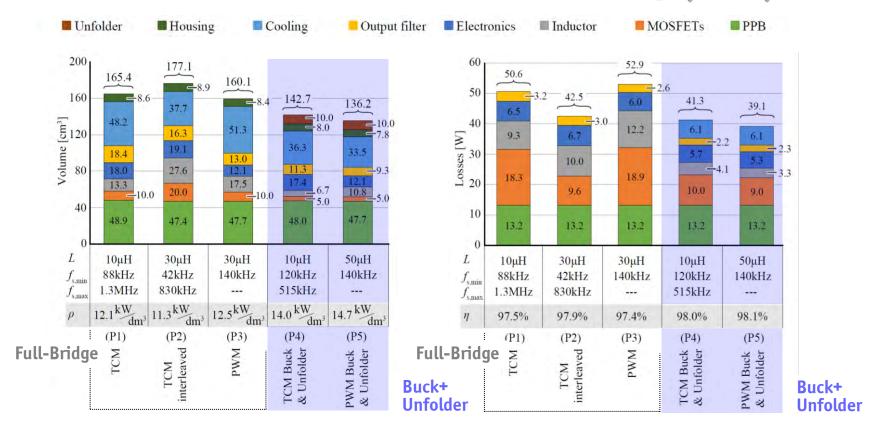

### **Little Box 2.0 – Multi-Objective Optimization**

- DC/ AC Buck Converter + Unfolder & PWM Shows Best Performance Full-Bridge Employs 2 Switching Bridge Legs Larger Volume & Losses

- **Interleaving Not Advantageous Lower Heatsink Vol. but Larger Total Vol. of Switches and Inductors**

■  $\rho$ = 250W/in<sup>3</sup> (15kW/dm<sup>3</sup>) @  $\eta$ = 98% Efficiency Achievable for Full Optimization

### **Little Box 2.0 – Volume & Loss Distribution @ (P1...5)**

- **Volume Dominated by Heatsink & PPB (Power Pulsation Buffer) Losses for Buck+Unfolder Dominated by Switches & PPB**

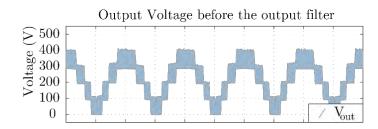

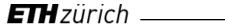

# **Experimental Results**

Control Block Diagram

Output Voltage/Input Current Quality

Efficiency

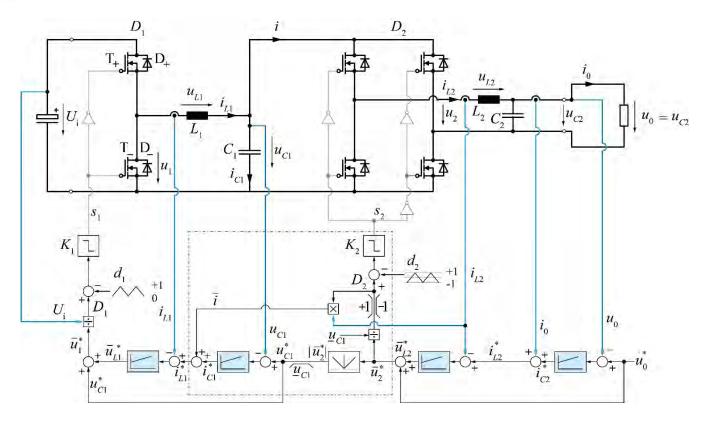

### **Little Box 2.0 - Control Structure**

- Each Stage (Buck & Unfolder) Controlled with Cascaded Current and Voltage Loop Without Switching of Unfolder Control Like for Conventional Boost PFC Rectifier

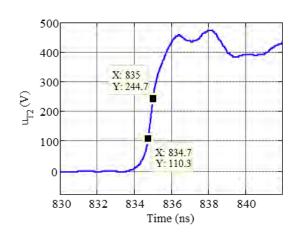

# Analysis of DC/ | AC | -Buck Converter & Unfolder

Voltage Zero Crossing Behavior With & Without Switching of Unfolder

- Output Voltage & Current Fully Controlled Around Voltage Zero Crossings

- Slope of Buck Conv. Outp. Current can be Decreased Adv. for React. Loads (Step-Change of DC Current)

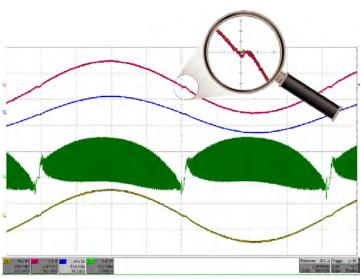

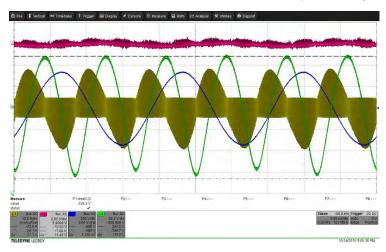

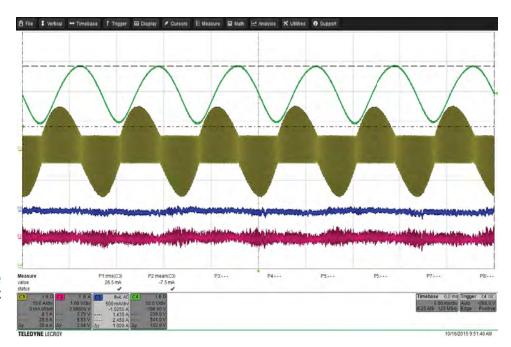

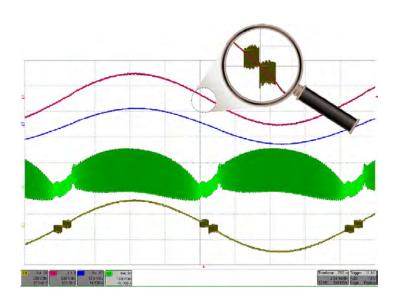

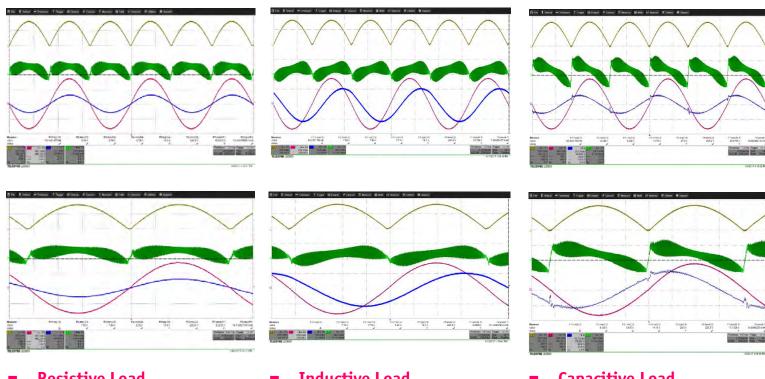

### Little Box 2.0 – Measured Waveforms

• DC/|AC| Buck-Stage Output Voltage & Inductor Current

**Resistive Load**

**Inductive Load**

**Capacitive Load**

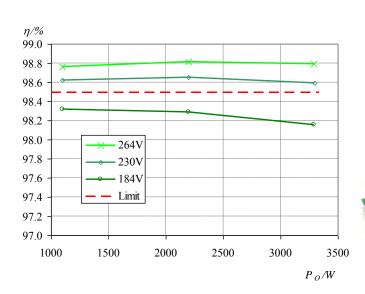

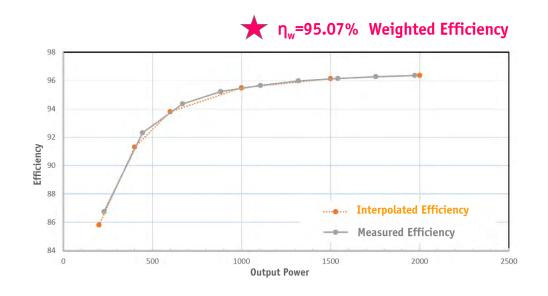

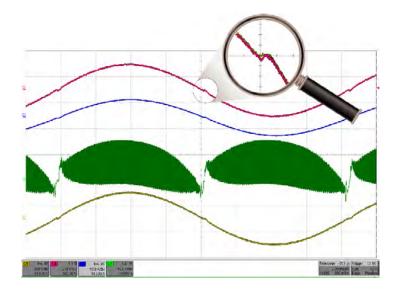

# **Little Box 2.0 – Preliminary Efficiency Measurements**

- Performance of First DC/ | AC | Buck Converter + Unfolder Prototype

- PWM Operation

- Without Power Pulsation Buffer

**98% for Res. Load Achievable for Red. of Cond. Losses of PCB (Copper Cross Sect.) & Unfolder (** $R_{ds,on}$ **)**

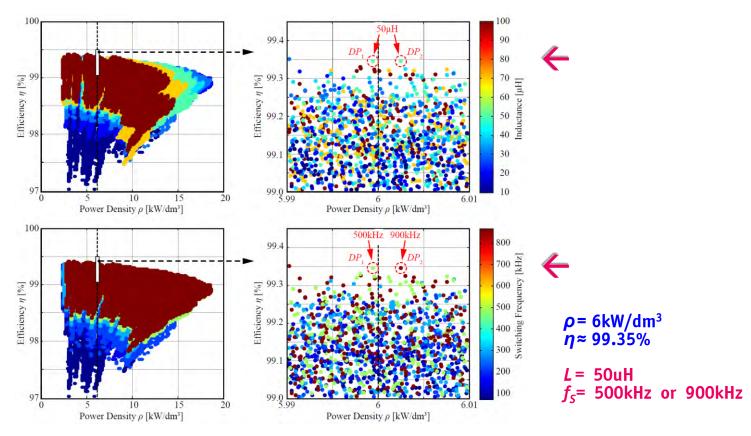

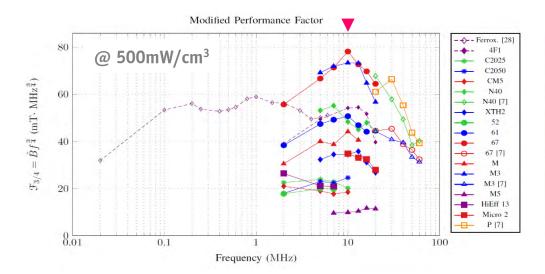

# Little Box 3.0

5...10MHz Switching Frequency Performance of Low-µ HF Magnetic Materials Electrolytic Caps vs. Power Pulsation Buffer

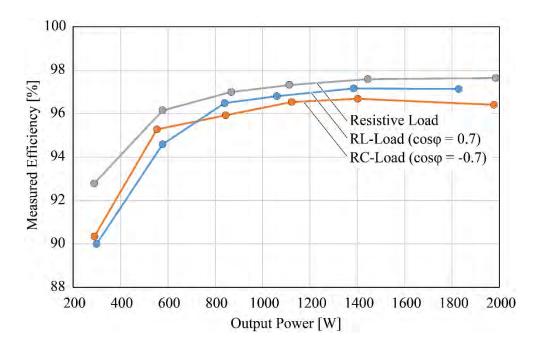

# **Magnetics Operation Frequency Limit (1)**

**Serious Limitation of Operating Frequency by HF Losses**

Source: Prof. Albach, 2011

- Core Losses (incr. @ High Frequ. & High Operating Temp.)

Temp. Dependent Lifetime of the Core

- **Skin-Effect Losses**

- **Proximity Effect Losses**

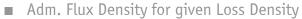

Skin-Factor F<sub>s</sub> for Litz Wires with N Strands

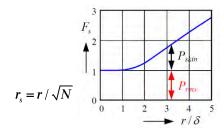

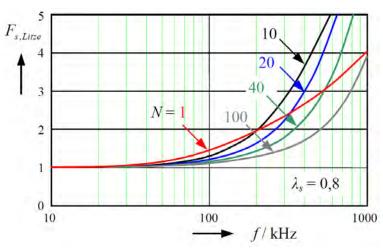

# **Magnetics Operating Frequency Limit (2)**

- (Modified) "Core Material Perform. Factor"  $F_{0.75} = B_{pk}$  . $f^{0.75}$  Defined for Def. Core Loss Performance Factor prop. to VA Handling Capability Min. Vol. @ Max. of  $F_{0.75}$  Little Benefit of Increased  $f_S$  for Conv. Ferrites in 200kHz...2MHz

- Peak Performance of Low-µ HF Core Materials @ 5-10 MHz

Source: Hanson et al. FCCF 2015

Fair-Rite 67 ( $\mu_r$ =40) All Inductors w. 0=200

$\blacksquare$   $f_s$  in the MHz-Range Results in Very Low EMI Filter Volume

# ► TCM Digital Control / Timing Challenges @ $f_S > 1$ MHz

- Dead Times Required for Res. Transition (ZVS)

- i = 0 Detection Time Delay

- Signal Isolator & Gate Drive Time Delays

- Rel. Large Cond. Losses @ Low Output Current

- New High Speed / Low-Volume / Low-Loss *i*= 0 Detection Concepts Required

- Integrated Gate Drive w. (Hysteresis) Current Control Functionality Required

Overall **Summary**

Source: whiskeybehavior.info

# **Performance Limits / Future Requirements**

- 220...250W/in<sup>3</sup> for Two-Level Bridge Leg + Unfolder

- 250...300W/in<sup>3</sup> for Highly Integrated Multi-Level Approach

- Isol. Distance Requirements Difficult to Fulfill

- Fulfilling Ind. Overvoltage Requirements would Signific. Reduce Power Density

- Low Frequency (20kHz...120kHz) SiC vs. HF (200kHz...1.2MHz) GaN

- Multi-Cell Concepts for LV Si (GaN) vs. Two-Level SiC (GaN)

- New Integr. Control Circuits and i=0 Detection for Sw. Frequency >1MHz

- Integrated Gate Drivers & Switching Cells

- High Frequency Low Loss Magnetic Materials

- High Bandwidth Low-Volume Current Sensors

- Low Loss Ceramic Capacitors Tolerating Large AC Ripple

- Passives w. Integr. Heat Management and Sensors

- 3D Packaging

- New U-I-Probes Required for Ultra-Compact Conv. R&D

- Spec. Testing Devices Equipped with Integr. Measurement Functions

- Convergence of Sim. & Measurem. Tools  $\rightarrow$  Next Gen. Oscilloscope

- New Multi-Obj. Multi-Domain Simulation/Optim. Tools

# References

ETH Zurich Other Finalists Non-Finalists General

### **▶** Publications of ETH Zurich

- D. Neumayr, D. Bortis, E. Hatipoglu, J. W. Kolar, G. Deboy, New Efficiency Optimal Frequency Modulation (OFM) for High Power Density DC/AC Converter Systems, to be published in Proc. of the International Future Energy Electronics Conference (IFEEC-ECCE Asia), Kaohsiung, Taiwan, June 3-7, 2017.

- **D. Neumayr, M. Guacci, D. Bortis, J. W. Kolar,** Novel Temperature-Gradient based Calorimetric Measurement Principle to Obtain Soft-Switching Benchmark of GaN and SiC Power Devices, Proceedings of the 29<sup>th</sup> IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD), Sapporo, Japan, May 28 June 1, 2017.

- **D. Rothmund, D. Bortis, J. Huber, D. Biadene, J. W. Kolar,** 10kV SiC-Based Bidirectional Soft-Switching Single-Phase AC/DC Converter for Medium-Voltage Solid-State Transformer Applications, Proceedings of the 8<sup>th</sup> International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Florianopolis, Brazil, April 17-20, 2017.

- M. Guacci, D. Neumayr, D. Bortis, J. W. Kolar, G. Deboy, Analysis and Design of a Multi-Tapped High-Frequency Auto-Transformer Based Inverter System, Proceedings of the 17<sup>th</sup> IEEE Workshop on Control and Modeling for Power Electronics (COMPEL), Trondheim, Norway, June 27-30, 2016.

- **D. Neumayr, D. Bortis, J. W. Kolar,** *Comprehensive Large-Signal Performance Analysis of Ceramic Capacitors for Power Pulsation Buffers*, Proceedings of the 17<sup>th</sup> IEEE Workshop on Control and Modeling for Power Electronics (COMPEL), Trondheim, Norway, June 27-30, 2016.

- **D. Bortis, D. Neumayr, J. W. Kolar,** ηρ-Pareto Optimization and Comparative Evaluation of Inverter Concepts considered for the GOOGLE Little Box Challenge, Proceedings of the 17<sup>th</sup> IEEE Workshop on Control and Modeling for Power Electronics (COMPEL), Trondheim, Norway, June 27-30, 2016.

- J. W. Kolar, D. Bortis, D. Neumayr, The Ideal Switch is Not Enough, Proceedings of the 28<sup>th</sup> IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech Republic, June 12-16, 2016.

- **D. Bortis, O. Knecht, D. Neumayr, J. W. Kolar,** Comprehensive Evaluation of GaN GIT in Low- and High-Frequency Bridge Leg Applications, Proceedings of the 8<sup>th</sup> International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, May 22-25, 2016.

- **D. Neumayr, D. Bortis, J. W. Kolar,** *Ultra-Compact Power Pulsation Buffer for Single-Phase DC/AC Converter Systems,* Proceedings of the 8<sup>th</sup> International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, May 22-25, 2016.

### **▶** Publications of Other Finalists

- F. Frebel, O. Bomboir, P. Bleus, D. Rixhon, Transformer-less 2kW Non-Isolated 400VDC/230VAC Single-Stage Micro-Inverter, Proc. of the IEEE Intern. Telecommunications Energy Conference (INTELEC), 2016.

- R. Ghosh, M. Srikanth, D. Klikic, M. Wang, R. Mitova, Novel Active Ripple Filtering Schemes used in the Little Box Inverter, to be published in Proc. of the Intern. Conf. on Power Conv. and Intelligent Motion (PCIM Europe), 2017.

- **L. Zhang, R. Born, X. Zhao, J.S. Lai,** A High Efficiency Inverter Design for Google Little Box Challenge, Proc. of the IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 2015.

- C. Zhao, B. Trento, L. Jiang, E. A. Jones, B. Liu, Z. Zhang, D. Costinett, F. Wang, L. M. Tolbert, J. F. Jansen, R. Kress, R. Langley, Design and Implementation of GaN-Based 100-kHz 102-W/in<sup>3</sup> Single-Phase Inverter, IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 4, no. 3, pp. 824–840.

- S. Qin, Y. Lei, C. Barth, W. C. Liu, R. C. N. Pilawa-Podgurski, A High Power Density Series-Stacked Energy Buffer for Power Pulsation Decoupling in Single-Phase Converters, to be published in the IEEE Transactions on Power Electronics.

- T. Menrath, S. Matlok, S. Endres, S. Zelter, B. Eckardt, Mechatronic Design of 2kW SiC DC/AC Converter with 200W/in<sup>3</sup>, to be published in Proc. of the Intern. Conf. on Power Conv. and Intelligent Motion (PCIM Europe), 2017.

### **▶** General Publications

Solaredge Technologies Ltd., Multi-level Inverter, European Patent Application EP 2779410A2 (Inventor: I. Yoscovitch), filed March 14, 2014, published Sept. 17, 2014.

- C. P. Henze, H. C. Martin, D. W. Parsley, Zero-voltage Switching in High Frequency Power Converters using Pulse Width Modulation, Proc. of the IEEE Applied Power Electronics Conference (APEC), 1988, pp. 33-40.

- R. W. Erickson, A. P. Rogers, A Microinverter for Building-Integrated Photovoltaics, Proc. of the IEEE Applied Power Electronics Conference (APEC), 2009, pp. 911-917.

- M. Pahlevaninezhad, P. Jain, Zero Voltage Switching interleaved Boost AC/DC Converter, US Patent US 8723487B2 (May 13, 2014), filed March 9, 2012.

- J. E. Knowles, The Origin of Increase in Magnetic Losses Induced by Machining Ferrites, IEEE Trans. on Magnetics, vol. 11, pp. 1 –5, 1975.

# **Biographies** of the Authors

kolar@lem.ee.ethz.ch neumayr@lem.ee.ethz.ch bortis@lem.ee.ethz.ch

**Johann W. Kolar** (F´10) received his Ph.D. degree (summa cum laude) from the Vienna University of Technology, Austria. He is currently a Full Professor and the Head of the Power Electronic Systems Laboratory at the Swiss Federal Institute of Technology (ETH) Zurich. He has proposed numerous novel PWM converter topologies, and modulation and control concepts and has supervised over 60 Ph.D. students. He has published over 750 scientific papers in international journals and conference proceedings, 3 book chapters, and has filed more than 140 patents. He has presented over 20 educational seminars at leading international conferences, has served as IEEE PELS Distinguished Lecturer from 2012 through 2016, and has received 25 IEEE Transactions and Conference Prize Paper Awards, the 2014 IEEE Power Electronics Society R. David Middlebrook Achievement Award, the 2016 IEEE William E. Newell Power Electronics Award, the 2016 IEEE PEMC Council Award, and the ETH Zurich Golden Owl Award for excellence in teaching. He has initiated and/or is the founder of 4 ETH Spin-off companies. The focus of his current research is on ultra-compact and ultra-efficient SiC and GaN converter systems, wireless power transfer, Solid-State Transformers, Power Supplies on Chip, as well as ultra-high speed and ultra-light weight drives, bearingless motors, and energy harvesting.

**Dominik Neumayr** (SM10) started his academic education at the University of Applied Sciences (FH) for Automation Engineering in Wels and received the Dipl.-Ing. (FH) degree in 2008. He was with the Center for Advanced Power Systems (CAPS) in Tallahassee/Florida working on Power/Controller Hardware-in-the-Loop simulations and control systems design for AC/DC/AC PEBB based converter systems from ABB. He continued his academic education at the Swiss Federal Institute of Technology in Zurich (ETH Zurich) and received the M.Sc. degrees in electrical engineering and information technology in 2015. Since spring 2015 he is a PhD student at the Power Electronic Systems (PES) Laboratory, ETH Zurich. His current research focuses on ultra-high power density converter systems.

**Dominik Bortis** (M'08) received the M.Sc. degree in electrical engineering and the Ph.D. degree from the Swiss Federal Institute of Technology (ETH) Zurich, Switzerland, in 2005 and 2008, respectively. In May 2005, he joined the Power Electronic Systems Laboratory (PES), ETH Zurich, as a Ph.D. student. From 2008 to 2011, he has been a Postdoctoral Fellow and from 2011 to 2016 a Research Associate with PES, co-supervising Ph.D. students and leading industry research projects. Since January 2016 Dr. Bortis is heading the newly established research group Advanced Mechatronic Systems at PES.

# **Thank You!**