#### **DISS. ETH NO. 24023**

# Design and Optimization of Mixed-Criticality Systems

A thesis submitted to attain the degree of

DOCTOR OF SCIENCES of ETH ZURICH (Dr. sc. ETH Zurich)

presented by

PENGCHENG HUANG

Master of Science,

Delft University of Technology

born on May 26, 1987 citizen of China

accepted on the recommendation of Prof. Dr. Lothar Thiele, examiner Prof. Dr. Alan Burns, co-examiner

TIK-SCHRIFTENREIHE NR. 168

Pengcheng Huang

# Design and Optimization of Mixed-Criticality Systems

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich A dissertation submitted to ETH Zurich for the degree of Doctor of Sciences

Diss. ETH No. 24023

Prof. Dr. Lothar Thiele, examiner Prof. Dr. Alan Burns, co-examiner

Examination date: December 13, 2016

致我的家人——一切爱皆始於家庭。

### **Abstract**

Mixed-Criticality is emerging as a significant trend for safety-critical systems, especially in automotive and avionics industries. Conventionally, those systems are designed as multiple sub-systems of *distinct* criticality or importance levels. With the ever-increasing demand of system functionalities and the shift of the semiconductor industry to more powerful (multi-core) platforms, consolidating/mixing functionalities of different criticality levels in a common hosting platform is appealing – system costs induced by size, weight and power consumptions could be potentially greatly reduced in the mixed-criticality setting.

The benefits brought by mixed-criticality systems are, however, accompanied by a multitude of new challenges. Most noticeably, due to resource sharing, functionalities of different criticality levels can interfere with each other, jeopardizing their guarantees made in isolation. To address this, new mixed-criticality models/protocols and corresponding scheduling techniques need to be developed to provide adequate isolation among criticality levels, and their limits (as well as potential extensions) need to be understood. Many traditional design issues for conventional embedded and/or safety-critical systems need to be rethought in the mixed-criticality era. For example, in addition to common timing threats considered for time-critical systems, hardware/software faults also need to be considered in the design of real-time mixed-safety-critical systems. In order to increase the system power efficiency, it is necessary to extend conventional energy minimization techniques to emerging mixed-criticality applications while considering the peculiarities of such systems.

As a step towards solving the above challenges, this thesis presents a whole stack of solutions to model, design and optimize mixedcriticality systems, in areas regarding real-time, fault-tolerance and energy-efficiency. Specifically, we make three main contributions:

1 We design the first mixed-criticality models to improve the service guarantee for less critical tasks in urgent scenarios – existing solutions commonly assume to drop all those tasks when any critical task overruns, which could be hardly acceptable in practice. In particular, we propose service adaptation, detailed modeling through interference constraint graphs, and processor over-clocking to adaptively degrade the system service in urgent scenarios. We show how common scheduling techniques like fixed-priority (FP)

and earliest deadline first (EDF) can be extended under those models and demonstrate considerable performance improvements compared to existing solutions. To further understand the limit of existing mixed-criticality models in line with industrial practices (i.e., with static temporal isolation among criticality levels), we present optimal scheduling techniques and we theoretically quantify the schedulability loss of those models.

- 2 We present the first mixed-criticality framework, where faulttolerance, real-time requirements and runtime adaptation are jointly considered to achieve a safe system design. hardware/software faults, we adopt task re-execution (singlecore) and replication (multi-core) as our fault-tolerance techniques and explicitly follow safety standards to model system safety requirements on different criticality levels. To further deal with urgent scenarios where critical tasks do not succeed after a certain number of trials, we propose runtime adaptations to reallocate system resources to critical tasks in such scenarios. Based on this, we present fault-tolerant mixed-criticality scheduling techniques and corresponding analysis techniques to meet both, safety and real-time requirements. Our solutions work on single-core and multi-core platforms, demonstrating the advantages of runtime adaptations and revealing important findings on the impact of commonly assumed mixed-criticality reconfigurations on the system feasibility.

- 3 We develop the first dynamic voltage and frequency scaling (DVFS) techniques to improve energy efficiency for mixed-criticality We show that fundamental trade-offs exist for this problem: DVFS can help the system to speedup in order to overcome the urgent scenarios where critical tasks overrun, which further allows the system to relax (slow down) and save dynamic energy in nominal scenarios where tasks do not overrun. Assuming EDF based scheduling, we present optimal and heuristic solutions in a general setting firstly on a single-core, considering both leakage and dynamic energy consumptions and all different system operation scenarios. We then develop energy-aware mixed-criticality task mapping techniques to extend our single-core solutions to multicore platforms. Our solutions demonstrate considerable energy savings for both synthetic task sets and a realistic industrial usecase, while revealing a rather surprising finding - the industrial best practice of spatially isolating different criticality levels almost has comparable energy savings to mixing them on each core.

## Zusammenfassung

Mixed-Criticality ist ein bedeutender Trend im Bereich sicherheitskritischer Systeme, allem voran in der Automobil- und Avionikindustrie. Konventionelle Systeme bestehen aus mehreren Teilsystemen, welche *unterschiedliche* Kritikalitäts-/Wichtigkeitsniveaus abdecken. Mit steigender Nachfrage nach erweiterter Systemfunktionalität und der Verlagerung der Prozessorindustrie auf leistungsfähigere (Multi-Core) Plattformen ist es vielversprechend die Funktionalitäten unterschiedlicher Kritikalitätsniveaus auf einer gemeinsamen Plattform zu konsolidieren. Durch Grösse, Gewicht und Energieverbrauch bedingte Systemkosten lassen sich in einem Mixed-Criticality Setting möglicherweise stark reduzieren.

Die Vorteile, welche Mixed-Criticality Systeme bieten, werden jedoch von einer Vielzahl neuer Herausforderungen begleitet. Besonders durch Ressourcen-Sharing können sich verschiedene Kritikalitätsniveaus gegenseitig stören, obwohl durch Isolation diese gegenseitige Beeinflussung ausgeschlossen werden soll. Um diese Probleme zu adressieren, müssen neue Mixed-Criticality Modelle und Protokolle, sowie entsprechende Scheduling-Techniken entwickelt und deren Grenzen (und mögliche Erweiterungen) verstanden werden um genügende Isolation zwischen den unterschiedlichen Kritikalitätsniveaus zu garantieren. Viele typischen Designfragen konventioneller eingebetteter und/oder sicherheitskritischer Systeme müssen in der Mixed-Criticality Ara überdacht werden. So müssen zum Beispiel zusätzlich zu den üblichen Tasküberlauf in zeitkritischen Systemen auch Hardware- und Software-Fehler in der Designphase von Echtzeit Mixed-Criticality Systemen bedacht werden. Um ebenfalls die Energieeffizienz solcher Systeme zu verbessern, ist es ebenso notwendig konventionelle Energiesparmechanismen für zukünftige Mixed-Criticality Systeme zu erweitern.

Diese Disseration stellt einen ersten Schritt zur Lösung dieser Probleme dar. Dabei werden eine Reihe von Lösungen zur Modellierung, dem Design und der Optimierung von Mixed-Criticality Systemen in den Bereichen Echtzeitverarbeitung, Fehlertoleranz und Energieeffizienz präsentiert. Im Einzelnen werden folgende Beiträge gemacht:

1 Wir entwerfen die ersten Mixed-Criticality Modelle welche die Servicegarantie weniger kritischer Tasks in dringenden Situationen verbessern. Im Gegensatz dazu gehen bestehende Lösungen davon aus, dass weniger kritische Tasks automatisch abgebrochen werden sobald ein kritischer Task überläuft, was in der Praxis kaum umsetzbar ist. Insbesondere schlagen wir dynamische Serviceadaptierung, detaillierterer Modellierung mittels Interferenz Bedingungsgraphen und Prozessorübertaktung vor, um den Systemservice in dringenden Situationen zu adaptieren. Wir zeigen auf wie bekannte Schedulingalgorithmen wie Fixed-Priority (FP) und Earliest-Deadline-First (EDF) mithilfe dieser Modelle erweitert werden können und demonstrieren dass diese die Performance gegenüber bestehenden Lösungen erheblich verbessern. Ebenso präsentieren wir optimale Schedulingtechniken und quantifizieren die Einbussen auf die Schedulability um die Einschränkungen bestehender Mixed-Criticality Modellen im Zusammenhang mit der Industriepraxis, wie zum Beispiel zeitliche Isolation der Kritikaliätsniveaus, zu verstehen.

- 2 Wir präsentieren das erste Mixed-Criticality Framework welches Echtzeit-Anforderungen und Serviceanpassung zur Laufzeit gemeinsam betrachtet um ein sicheres Systemdesign zu erzielen. Unter der Annahme von Hardware- und Softwarefehlern Übernehmen wir die Techniken Task-Wiederausführung (Single-Core) und Replikation (Multi-Core) um Fehlertoleranz zu garantieren und folgen den strikten Sicherheitsstandards um die Sicherheitsanforderungen der verschiedenen Kritikalitätsniveaus zu modellieren. Weiter behandeln wir dringende Situationen in welchen kritische Tasks auch nach einigen Wiederausführungen nicht erfolgreich abgearbeitet wurden. In diesen Fällen schlagen wir vor dynamisch weitere System-Ressourcen für diese kritischen Tasks zu allozieren. Darauf aufbauend präsentieren wir fehlertolerante Mixed-Cricicality Schedulingalgorithmen and entsprechende Analysetechniken um Sicherheits- und Echtzeitanforderungen zu erfüllen. Die gezeigte Lösung arbeitet sowohl auf Single-Core als auch Multi-Core Systemen und liefert wichtige Erkenntnisse über den Einfluss typischer Rekonfigurationsmassnahmen auf die Umsetzbarkeit von Mixed-Criticality Systemen.

- 3 Wir entwickeln die erste dynamische Spannungs- und Frequenzskalierung (Dynamic Voltage and Frequency Scaling, DVFS) Technik für Mixed-Criticality Systeme und zeigen auf, welche grundlegenden Kompromisse für dieses Problem getroffen werden müssen: DVFS kann helfen die Ausführung zu beschleunigen um dringende Situationen zu überwinden und hilft zudem das System zu verlangsamen um Energie einzusparen wenn kritische Tasks keine erhöhten Ausführungszeiten haben. Wir präsentieren eine optimale und heuristische Lösung für EDF basiertes Scheduling für Single-Core Architekturen unter Einbeziehung von Leakage und dynamischem Energieverbrauch und

allen möglichen Systemzuständen. Wir entwicklen energiebewusste Mixed-Criticality Task-Mapping Algorithmen zur Erweiterung der Single-Core Lösung auf Multi-Core Plattformen. Die Evaluation unserer Lösung zeigt signifikante Energieeinsparungen sowohl für synthetische Task-Sets, als auch realistische industrielle Anwendungen. Interessanterweise zeigt die Anwendung der gleichen Massnahmen auf die industrielle Best Practice räumlicher Isolation annähernd die gleichen Energieeinsparungen.

### Acknowledgments

I owe my growth as a researcher to Prof. Lothar Thiele, which would have been limited without the opportunity he offered and his support during my PhD. He set up a good example for me, not only as a top researcher, but also as an educator and a colleague. Looking back, I have benefited a lot from the working experiences with him. For this, I am highly indebted.

I would like to express my sincere thanks to Prof. Alan Burns for helping to review this thesis and for traveling to Zürich in the midst of pressing affairs to serve on the committee board.

I feel very lucky to have many colleagues/friends supporting me both at work and in private lives. I would like to thank Georgia Giannopoulou, for sharing the office room with me in the past years, for her encouragement at the beginning of my PhD and her great kindness offered on an almost daily basis. I would also like to thank Pratyush Kumar, Hoeseok Yang, Lukas Sigrist, Andres Gomez, Stefan Draskovic, Rehan Ahmed, Balz Maag, Romain Jacob, Zimu Zhou, and other current and former TEC members – for a lot of discussions we had on both research and random topics – they were really rewarding experiences.

Beyond collaborators on the papers in this thesis, I would like to thank Lukas Sigrist for translating the thesis abstract into German, Andres Gomez for his suggestions on English writing and Luyuan Zeng for conducting the experiments in Chapter 3.

I would also take this chance to thank Beat Futterknecht, Federico Ferrari and Jan Beutel – without all their help, settling down in Zurich would have been much harder. My thanks extend to Brütsch Friederike for organizing the travel of my co-examiner.

Last but not least, I would like to express my gratitude to my family – I am indebted and grateful to my grandparents Songming and Guifang, my parents Zhi and Xinfang, and my sister Shengnan. My most special thanks go to Herma, Shan and Jing – for offering me a place called home.

The work presented in this thesis was supported in part by the EU FP7 project CERTAINTY. This support is gratefully acknowledged.

## **Contents**

| Al | ostrac                                                                            | rt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | İ                                                                  |

|----|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Zι | ısamı                                                                             | menfassung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ii                                                                 |

| A  | knov                                                                              | vledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | vi                                                                 |

| Li | st of l                                                                           | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | X                                                                  |

| Li | st of [                                                                           | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | X                                                                  |

| 1  | Intr                                                                              | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                  |

| 3  | <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li><li>2.5</li><li>2.6</li></ul> | State-of-the-art Mixed-Criticality Models  Mixed-Criticality Service Adaptation  The Interference-Constraint Graph Model  Run and Be Safe: Mixed-Criticality Scheduling with Temporary  Processor Speedup  A New Isolation Scheduling Model for Mixed-Criticality Systems  Summary  **Red-Criticality Fault-Tolerance – Methods, Analysis and Findings  Background & Problem Statement  Safety Analysis Under Global Switching  Safety Analysis Under Local Switching  Evaluation  Summary | \$12<br>28<br>43<br>60<br>80<br><b>81</b><br>84<br>92<br>99<br>102 |

| 4  | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7                                     | rgy-Aware Mixed-Criticality – Concepts, Methods and Implication System Model                                                                                                                                                                                                                                                                                                                                                                                                               | 114<br>116                                                         |

| 5  | Con                                                                               | aclusion and Outlook                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 145                                                                |

|   | $\sim$   |  |

|---|----------|--|

| v | Contents |  |

|   |          |  |

| į                    | 5.2 | Possible Future Directions | 147 |

|----------------------|-----|----------------------------|-----|

| Bibliography         |     | 149                        |     |

| List of Publications |     |                            | 159 |

| Curriculum Vitæ      |     |                            | 163 |

# **List of Figures**

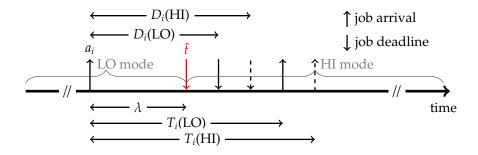

| 2.1  | A mo                                                  | ode transition triggered by task overrun                                                                                         | 15 |

|------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----|

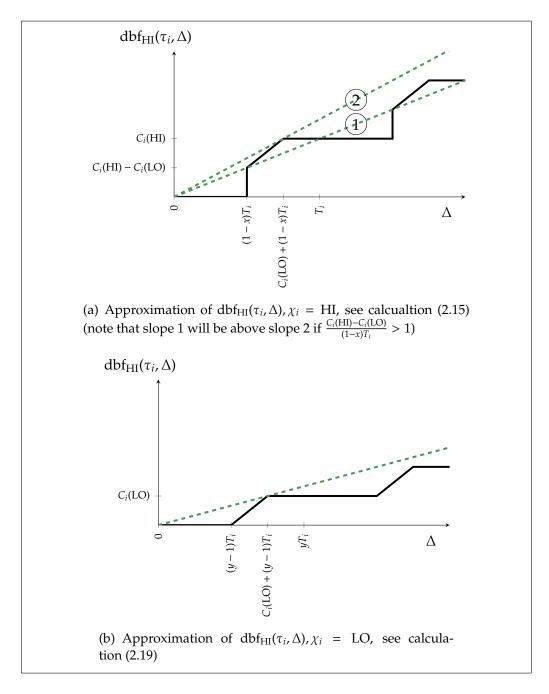

| 2.2  | Approximation of HI mode system demand bound function |                                                                                                                                  | 20 |

|      | (a)                                                   | Approximation of $dbf_{HI}(\tau_i, \Delta)$ , $\chi_i = HI$ , see calcualtion (2.15) (note that slope 1 will be above slope 2 if |    |

|      |                                                       | $\frac{C_i(HI)-C_i(LO)}{(1-x)T_i} > 1) \dots \dots \dots \dots \dots \dots \dots \dots$                                          | 20 |

|      | (b)                                                   | Approximation of $dbf_{HI}(\tau_i, \Delta), \chi_i = LO$ , see calcula-                                                          |    |

|      |                                                       | tion (2.19)                                                                                                                      | 20 |

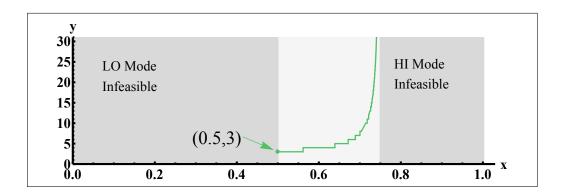

| 2.3  | Trad                                                  | e off between x and y                                                                                                            | 22 |

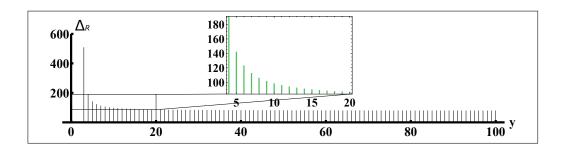

| 2.4  | Trad                                                  | e off between $\Delta_R$ and $y$                                                                                                 | 25 |

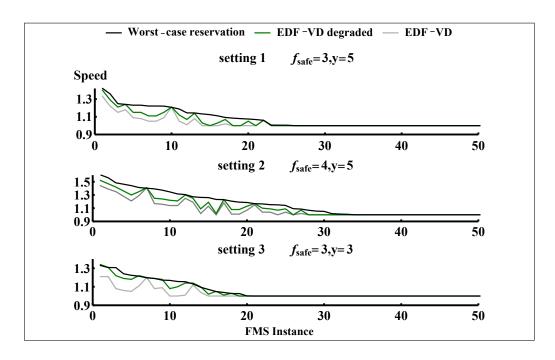

| 2.5  | Proc                                                  | essor speedup factors comparison - y-axis represents the                                                                         |    |

|      | -                                                     | essor speedup factor, x-axis represents FMS instances                                                                            | 26 |

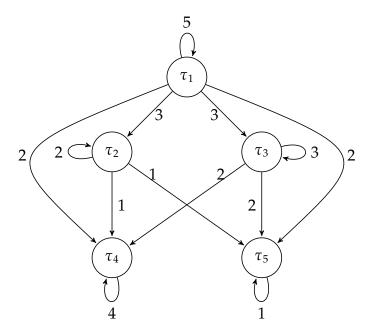

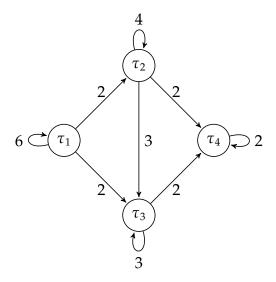

| 2.6  | ICG                                                   | representation for Example 2.4                                                                                                   | 33 |

| 2.7  | ICG                                                   | for the task set in Example 2.5                                                                                                  | 37 |

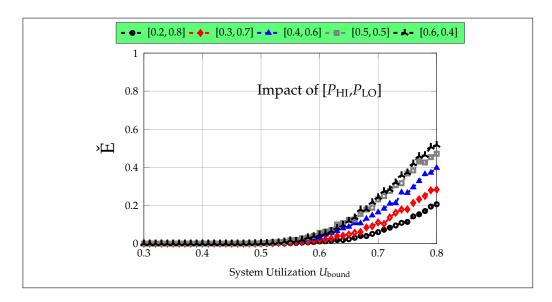

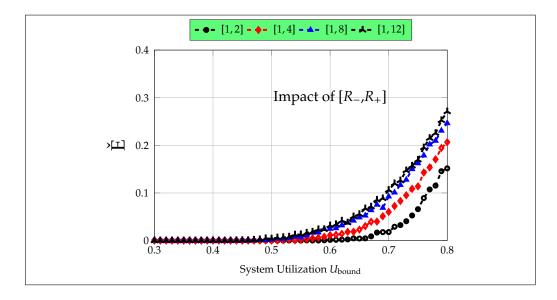

| 2.8  | Ě wi                                                  | th $T = 4$ , $T_+ = 16$ , $U = 0.02$ , $U_+ = 0.2$ , $R = 1$ , $R_+ = 4$                                                         | 41 |

| 2.9  | Ě wi                                                  | th $T_{-} = 4$ , $T_{+} = 16$ , $U_{-} = 0.02$ , $U_{+} = 0.2$ , $P_{HI} = 0.2$ , $P_{LO} = 0.8$ .                               | 42 |

| 2.10 | Ě wi                                                  | th $T = 4$ , $T_+ = 16$ , $U = 0.02$ , $U_+ = 0.2$ , $R = 1$ , $R_+ = 4$                                                         | 43 |

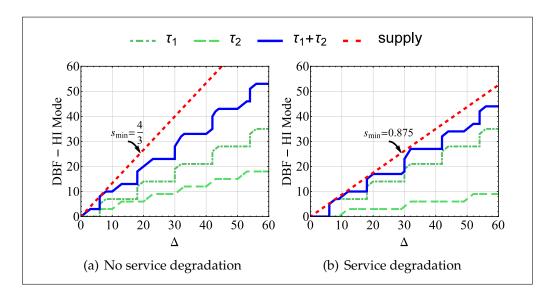

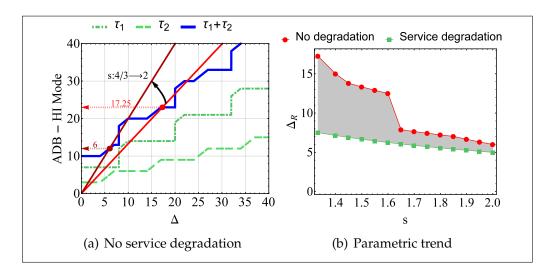

| 2.11 | Mini                                                  | mum speedup and demand bound functions                                                                                           | 46 |

|      | (a)                                                   | No service degradation                                                                                                           | 46 |

|      | (b)                                                   | Service degradation                                                                                                              | 46 |

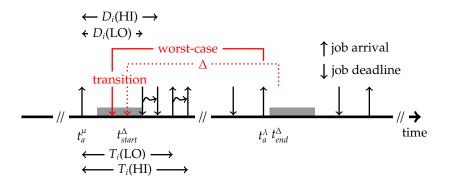

| 2.12 | Wors                                                  | st-case scenario for arrived demand                                                                                              | 49 |

| 2.13 | Serv                                                  | ice resetting time under dynamic processor speedup                                                                               | 52 |

|      | (a)                                                   | No service degradation                                                                                                           | 52 |

|      | (b)                                                   | Parametric trend                                                                                                                 | 52 |

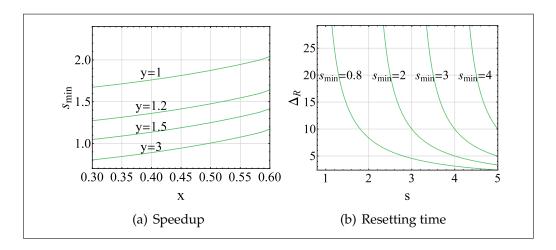

| 2.14 | Vario                                                 | ous tradeoffs: Impact of overrun preparation <i>x</i> and service                                                                |    |

|      | degr                                                  | adation $y$ on required speedup and service resetting time $\ \ .$                                                               | 56 |

|      | (a)                                                   | Speedup                                                                                                                          | 56 |

|      | (b)                                                   | Resetting time                                                                                                                   | 56 |

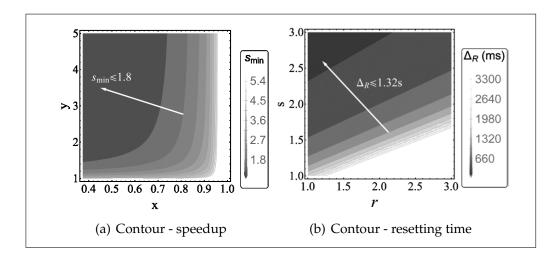

| 2.15 | Expe                                                  | rimental results on FMS                                                                                                          | 57 |

|      | (a)                                                   | Contour - speedup                                                                                                                | 57 |

|      | (b)                                                   | Contour - resetting time                                                                                                         | 57 |

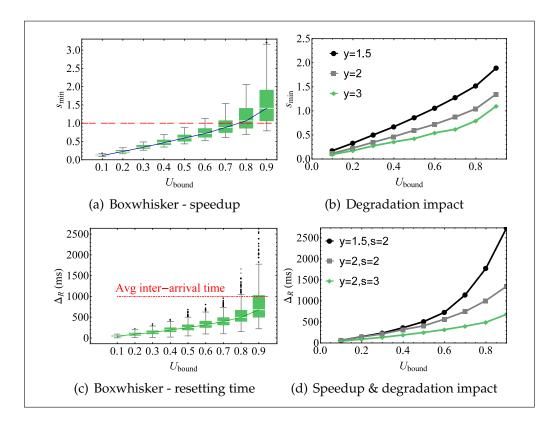

| 2.16 | inter-<br>critic<br>to $0.2$<br>1 to<br>the o<br>y =<br>and 1<br>differ                                                                               | riments using synthesized task sets, with task minimum arrival times randomly chosen from 2ms to 2s, task LO rality utilization $C_i(LO)/T_i(LO)$ randomly chosen from 0.01 2 and $r = C_i(HI)/C_i(LO)$ ( $\forall \tau_i \in \tau_{HI}$ ) randomly chosen from 3. Figure 2.16(a) is obtained assuming $y = 2$ and shows distribution of $s_{min}$ . Figure 2.16(c) is obtained assuming $2, s = 3$ and shows the distribution of $\Delta_R$ . Figure 2.16(b) Figure 2.16(d) show the median values of our results across rent system utilizations. $x$ in all cases is set to the minimum tarantee LO mode schedulability [HGST14] | 58 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | (a)                                                                                                                                                   | Boxwhisker - speedup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58 |

|      | (b)                                                                                                                                                   | Degradation impact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 58 |

|      | (c)                                                                                                                                                   | Boxwhisker - resetting time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58 |

|      | (d)                                                                                                                                                   | Speedup & degradation impact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58 |

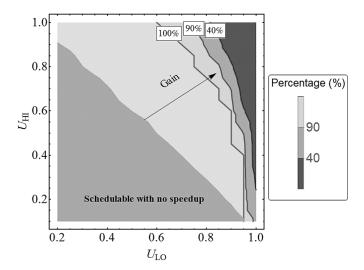

| 2.17 | speed $r$ (degeneral $\sum_{\chi_i \geq \chi} C_{\chi_i \geq \chi}$                                                                                   | dulability region under temporary processor speedup: $2x$ dup for no longer than $5s$ . For this set of experiments, efined in Figure 2.16) is set to $10$ . All other task ration parameters are the same as in Figure 2.16. $U_{\chi} = C_i(\chi)/T_i(\chi), \chi \in \{\text{HI}, \text{LO}\}.$ Marked numbers represent entages of schedulable task sets                                                                                                                                                                                                                                                                        | 59 |

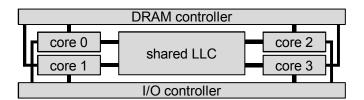

| 2.18 | -                                                                                                                                                     | ple typical multi-core architecture with $m=4$ cores that a last-level cache, DRAM controller and I/O controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61 |

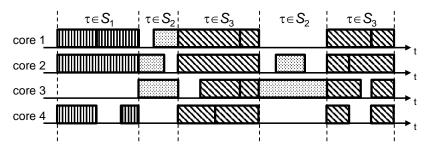

| 2.19 | Example IS schedule with three task classes $S_1$ , $S_2$ and $S_3$ . Vertical lines mark the synchronous switching between task classes on all cores |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63 |

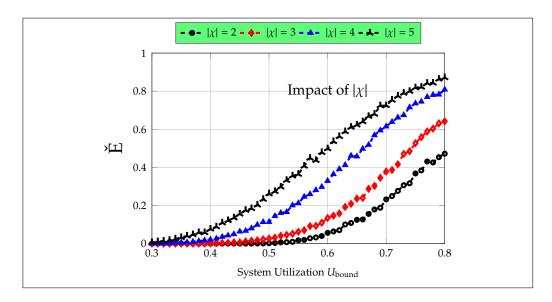

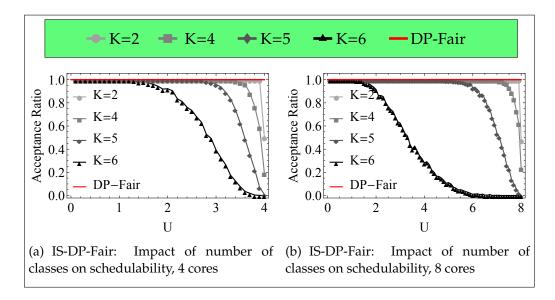

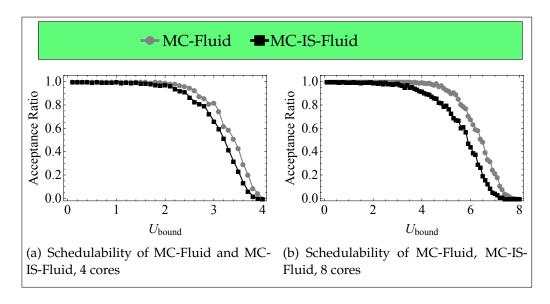

| 2.20 |                                                                                                                                                       | tion Scheduling: Fraction of schedulable task sets vs. system ration. Red lines in plots correspond to DP-Fair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 78 |

|      | (a)                                                                                                                                                   | IS-DP-Fair: Impact of number of classes on schedulability, 4 cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 78 |

|      | (b)                                                                                                                                                   | IS-DP-Fair: Impact of number of classes on schedulability, 8 cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 78 |

| 2.21 | Isola                                                                                                                                                 | tion Scheduling integrated with AIS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79 |

|      | (a)                                                                                                                                                   | Schedulability of MC-Fluid and MC-IS-Fluid, 4 cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 79 |

|      | (b)                                                                                                                                                   | Schedulability of MC-Fluid, MC-IS-Fluid, 8 cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79 |

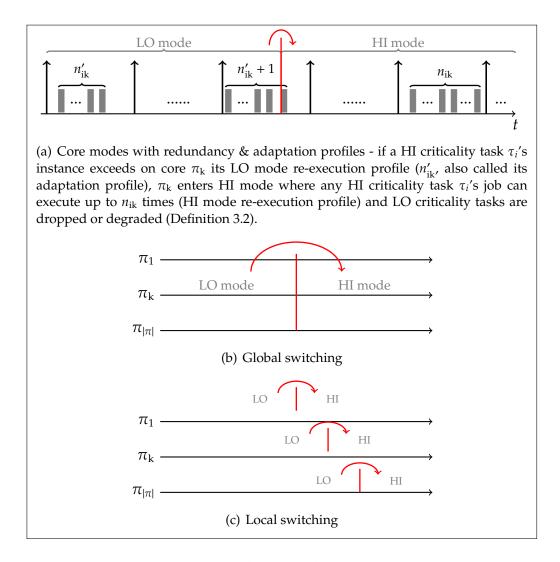

| 3.1  | Core                                                                                                                                                  | modes, global & local switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 89 |

|     | (a)        | Core modes with redundancy & adaptation profiles -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |            | if a HI criticality task $\tau_i$ 's instance exceeds on core $\pi_k$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|     |            | its LO mode re-execution profile ( $n'_{ik'}$ also called its                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|     |            | adaptation profile), $\pi_k$ enters HI mode where any HI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|     |            | criticality task $\tau_i$ 's job can execute up to $n_{ik}$ times (HI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|     |            | mode re-execution profile) and LO criticality tasks are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|     |            | dropped or degraded (Definition 3.2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89  |

|     | (b)        | Global switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 89  |

|     | (c)        | Local switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 89  |

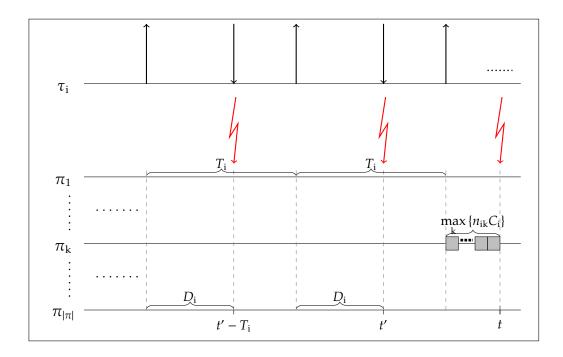

| 3.2 | Indu       | action process for Lemma 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 93  |

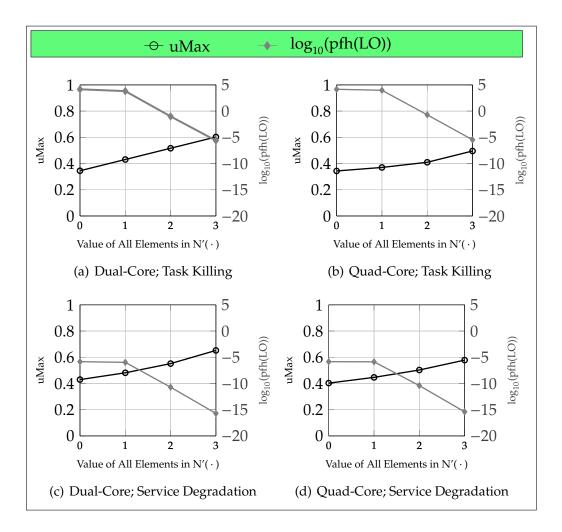

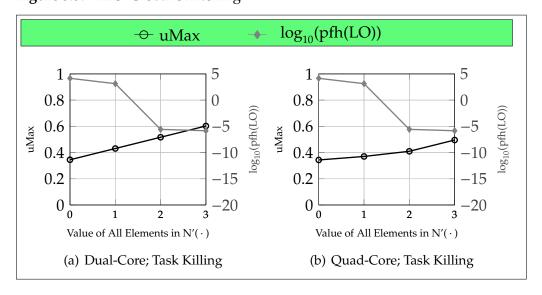

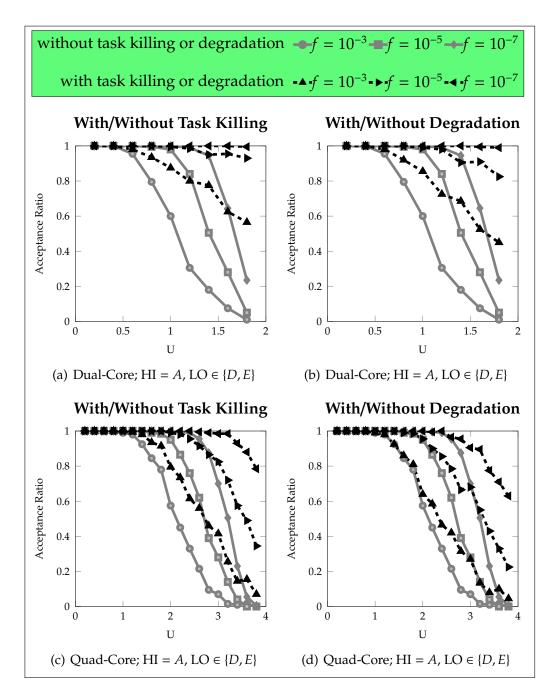

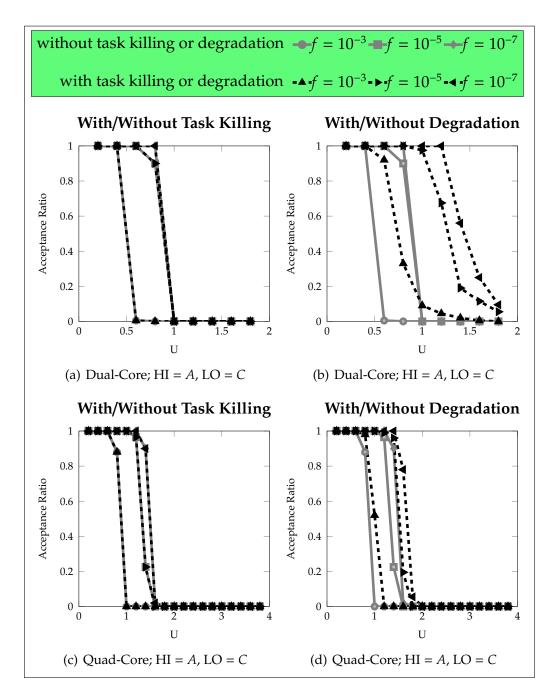

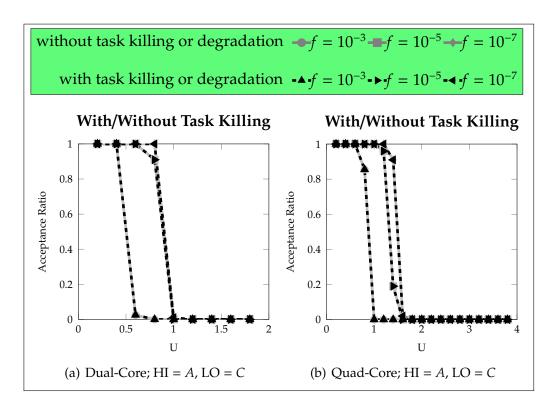

| 3.3 |            | : Global Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 104 |

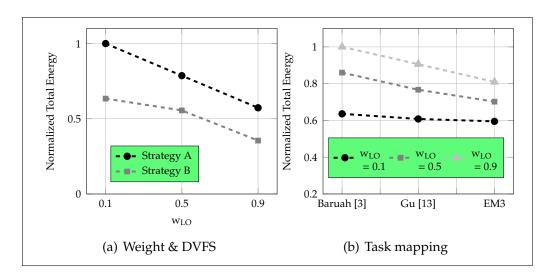

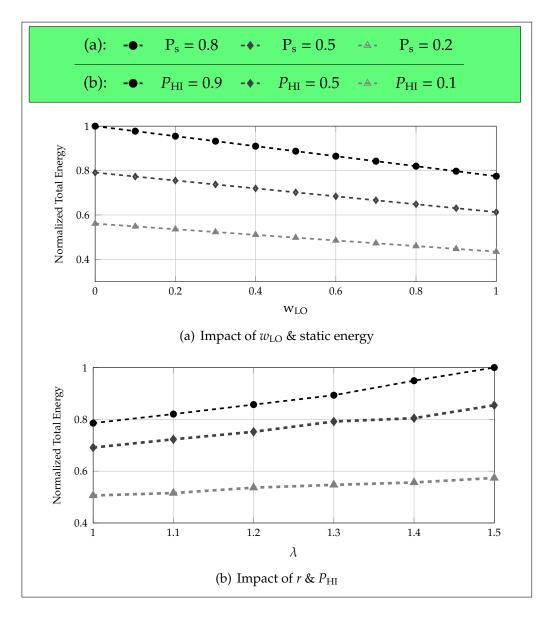

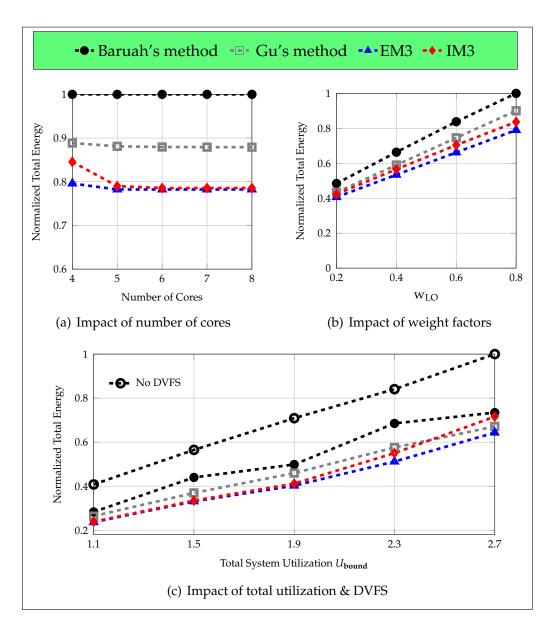

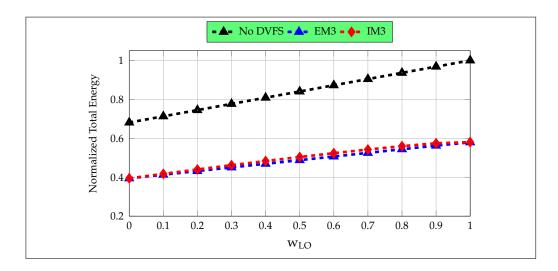

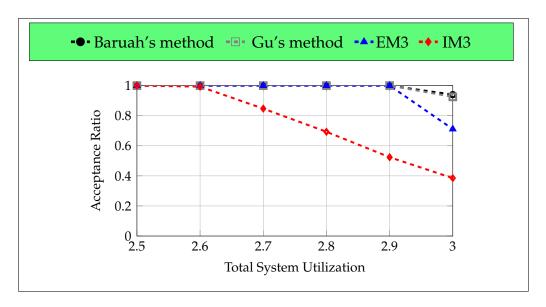

|     | (a)        | Dual-Core; Task Killing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 104 |