DISS. ETH NO. 23929

# Security Considerations for VLSI-Based Symmetric Encryption Devices

A thesis submitted to attain the degree of DOCTOR OF SCIENCES of ETH ZURICH (Dr. sc. ETH Zurich)

> presented by MICHAEL MÜHLBERGHUBER

Dipl.-Ing., Graz University of Technology

> born on 23.10.1984 citizen of Austria

accepted on the recommendation of

Prof. Dr. Hubert Kaeslin, examiner Prof. Dr. Srdjan Capkun, co-examiner Prof. Dr. Ir. Ingrid Verbauwhede, co-examiner

# Acknowledgments

Writing down a document like the present Ph.D. thesis is mainly a *one-man show*. However, the more important part—the actual content of it—is the result of a four year journey working on projects with many different people. I would like to take this opportunity to highlight several of them who deserve to be mentioned, as they significantly influenced this thesis in one way or the other.

First and foremost I thank Prof. Hubert Kaeslin from the Microelectronics Design Center for supervising my work and his support throughout the previous years. I am also grateful to my co-examiners, Prof. Srdjan Capkun and Prof. Ingrid Verbauwhede. This work was carried out as part of a collaboration between industry and academia and would not have been possible without the financial support from the Commission for Technology and Innovation (CTI). The regular and fruitful discussions with Dr. Richard De Moliner from Omnisec AG provided me an insight into the requirements for industrial products. Thanks a lot to Dr. Michael Hutter and Dr. Thomas Korak from the Institute of Applied Information Processing and Communication (IAIK) at Graz University of Technology for our collaborations.

Many colleagues at the Integrated Systems Laboratory (IIS) influenced my work significantly. I would like to express my deepest gratitude to Dr. Frank K. Gürkaynak and Dr. Norbert Felber. Without their help I would have most-likely never joined the IIS and would have missed a great opportunity. Furthermore, I appreciated working together with Dr. Patrick Maechler, Christoph Keller, Michael Gautschi, and Beat Muheim at the IIS. The output from many interesting discussions with the following people regularly inspired my daily work: Michael Schaffner, David Bellasi, Pirmin Vogel, Andreas Traber, and Dr. Pierre Greisen. Administrative tasks and infrastructure support are often overlooked. Thanks Christoph Wicki for the smoothly working IT systems and Christine Haller for keeping away most of the office work, letting me focus on my research. Hansjörg Gisler constantly supported me with shipments and component procurements. I had the opportunity to supervise many brilliant students as part of master theses and semester projects. Many thanks to all of them for their great work and commitment. In particular I would like to emphasize the work done by Philipp Dunst, Cyril Arnould, Marco Eppenberger, and Stefan Mach.

Ultimately I would like to thank my family and friends, including some of my co-workers, who became more than colleagues during the time of my Ph.D. Mum and dad, you shaped my personality and attitude more than anybody else and made me the person I am today. Thank you so much for always guiding me into the right direction. The previous years were not the easiest ones for my girlfriend Magdalena. Often little spare time gave our relationship a hurdle to be overcome. We managed to do so and I am looking forward to a common future with her.

# Abstract

The development and fabrication of secure, trustworthy, and efficient technical devices becomes an increasingly difficult task because of the high complexity of today's systems. Dedicated hardware solutions based on Application-Specific Integrated Circuits (ASICs) or Field-Programmable Gate Arrays (FPGAs) are generally preferred over their software counterparts to achieve ambitious throughput, power, or energy goals. Similar to their software equivalents, these hardwareoriented approaches suffer from several vulnerabilities that might be exploited by an attacker during the life cycle of a device.

As part of this thesis, we investigate risks and performance aspects, immanent in the development and fabrication of any VLSIbased symmetric encryption device. We consider ASICs and FPGAs as the lowest hierarchy level where an attacker may intrude the system. Therefore, we implant a hardware Trojan into an ASIC just prior to fabrication in a 180 nm CMOS technology by UMC. Both the genuine and the malicious design have actually been manufactured. Subsequently, we apply Trojan detection techniques based on side-channel fingerprinting. Despite the comparatively small size of the Trojan (0.5% of the original design), we successfully distinguish malicious from genuine ASICs.

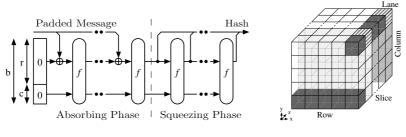

Since FPGAs are of particular interest for high-throughput designs of cryptographic algorithms, we also analyze Trojans on reconfigurable hardware. More specifically, we insert a malicious circuitry into a bitstream after placement and routing. Thereafter, we show how to use electromagnetic radiation as a side-channel to successfully detect the Trojan and experimentally demonstrate a method to actually localize it on the FPGA. Symmetric encryption devices need to share a common cipherkey prior to their communication. This exchange is often accomplished with the use of small hardware tokens like USB sticks or smart cards. Because such items are widely accessible by the general public, they need to be secured against implementation attacks like Differential Power Analysis (DPA). For that reason, we have developed and manufactured ZORRO, an ASIC to assess DPA countermeasures on a real chip. Based on measurements acquired from the fabricated ASIC, we show that 100 000 traces or less are sufficient to successfully attack ZORRO with standard DPA. ZORRO does not merely constitute an evaluation platform for DPA countermeasures, but also represents the smallest, DPA-secured ASIC implementation of a KECCAK-based Authenticated Encryption (AE) scheme available to date.

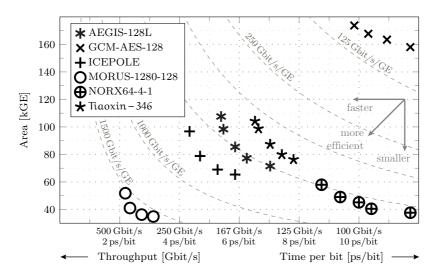

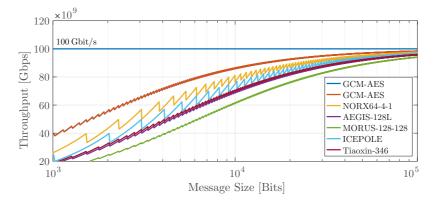

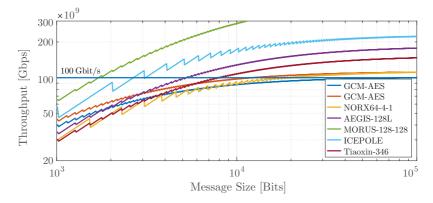

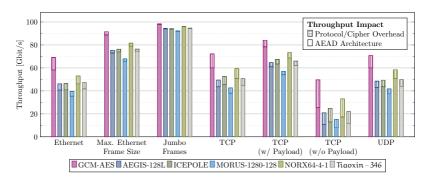

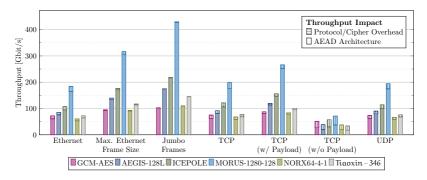

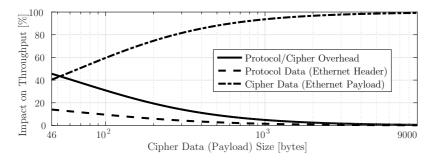

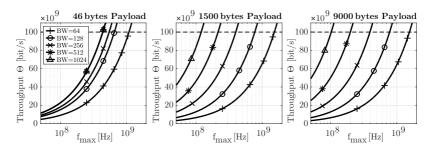

Eventually, we analyze the efficiency in terms of throughput-perarea of emerging AE algorithms. We aim at ASIC architectures with throughputs of 100 Gbit/s and even beyond. To do so, we create a GCM-AES reference architecture, targeting a 65 nm CMOS technology by UMC. This design serves as a basis for a comparison between several candidates from the CAESAR competition. We show that all of the CAESAR algorithms investigated outperform GCM-AES when looking at the asymptotic use case. However, we point out that when more realistic scenarios are considered, for instance, communication protocols like Ethernet, this advantage diminishes substantially.

# Zusammenfassung

Die Komplexität technischer Produkte ist in den vergangenen Jahren kontinuierlich gewachsen. Immer mehr Software- und Hardwarekomponenten werden zu grösseren Gesamtsystemen kombiniert um den Ansprüchen der Kunden gerecht zu werden. Aus diesem Grund wird die Entwicklung und Herstellung von hochperformanten sowie gleichzeitig als sicher und vertrauenswürdig geltenden Geräten stets schwieriger. Um den Anforderungen nach hohem Durchsatz und geringem Energieverbrauch nachkommen zu können, werden oftmals hardwarebasierte Lösungen ihren Software-Alternativen vorgezogen. Sowohl anwendungsspezifische integrierte Schaltungen (ASICs) als auch programmierbare Hardwarekomponenten (FPGAs) werden dafür häufig eingesetzt. Leider können im Zuge der Entwicklung und Fabrikation dieser Komponenten zahlreiche Schwachstellen dazu genützt werden, um die Sicherheit der Geräte zu unterwandern.

Die vorliegende Arbeit behandelt Risiken und Performanceaspekte, die während des Lebenszyklus eines VLSI-basierten symmetrischen Verschlüsselungsgerätes nicht vernachlässigt werden dürfen. ASICs und FPGAs werden dabei als unterste Hierarchieebene eines solchen Produktes angesehen. Aus diesem Grund untersuchen wir zunächst Hardware Trojaner. Dazu wurde ein bösartiger Schaltkreis in ein existierendes ASIC Design eingeschleust. Der unverfälschte sowie der leicht abgeänderte Chip wurden in einer 180 nm CMOS Technologie fabriziert und im Anschluss daran mittels Seitenkanalanalysen untersucht. Obgleich der implantierte Trojaner nur 0.5 % des ursprünglichen Designs ausmachte, konnten wir diesen zuverlässig detektieren.

Zur Umsetzung von kryptografischen Algorithmen in hochperformanten Anwendungen werden immer häufiger FPGAs verwendet. Daher vertieften wir unsere Trojaner-Untersuchungen in diese Richtung und implantierten einen bösartigen Schaltkreis in eine existierende FPGA Konfiguration. Unter Verwendung der elektromagnetischen Abstrahlung als Seitenkanal konnten wir zwischen bösartigen und unverfälschten Varianten eindeutig unterscheiden. Zusätzlich zur Detektion stellen wir eine Methode zur Lokalisation von Trojanern vor.

Für den Austausch von Schlüsselmaterial zwischen zwei Parteien werden oftmals USB Sticks oder Smartcards eingesetzt. Diese sind aufgrund ihres Einsatzbereiches meist relativ einfach einer breiteren Masse zugänglich und müssen daher gegen Implementierungsangriffe wie die differentielle Leistungsanalyse (DPA) geschützt werden. Hierzu präsentieren wir ZORRO, einen ASIC der ausschliesslich zur Beurteilung der Qualität von DPA Gegenmassnahmen entwickelt wurde. Basierend auf Messergebnissen zeigen wir, dass Techniken wie *Hiding* und *Masking* alleine keinen Angriffen auf unseren Chip mit bis zu 100 000 Stromverbrauchsprofilen vorbeugen können. Des Weiteren repräsentiert ZORRO die kleinste verfügbare, DPA-sichere ASIC-Realisierung eines KECCAK-basierten *Authenticated Encryption* Systems.

Abschliessend untersuchen wir die Effizienz hinsichtlich Durchsatz pro Fläche für aufstrebende kryptografische Algorithmen, welche sowohl Vertraulichkeit als auch Integrität gewährleisten. Dazu präsentieren wir zunächst eine GCM-AES Referenzarchitektur basierend auf einer 65 nm CMOS Technologie für Durchsätze von 100 Gbit/s und mehr. Im Anschluss daran werden hochperformante Designs einiger Kandidaten der zweiten Runde des CAESAR Wettbewerbs vorgestellt und mit der GCM-AES Architektur verglichen. Wir zeigen, dass alle untersuchten Mittbewerber deutlich effizienter in Hardware umzusetzen sind als der Referenzalgorithmus solange der asymptotische Durchsatz betrachtet wird. Werden die entwickelten Architekturen hingegen für Kommunikationsprotokolle wie Ethernet verwendet, so relativiert sich deren Vorsprung gegenüber GCM signifikant.

# Contents

| A        | ckno                        | wledgr                                             | nents                                   | v   |  |

|----------|-----------------------------|----------------------------------------------------|-----------------------------------------|-----|--|

| A        | bstra                       | act                                                |                                         | vii |  |

| Zι       | usam                        | menfa                                              | ssung                                   | ix  |  |

| 1        | Inti                        | roduct                                             | ion                                     | 1   |  |

|          | 1.1                         | The Need for Hardware-Based Security Systems       |                                         |     |  |

|          | 1.2                         | Cryptography Basics                                |                                         |     |  |

|          |                             |                                                    | of the Thesis                           | 7   |  |

|          |                             |                                                    | ibutions                                | 9   |  |

|          | 1.5                         | Outlin                                             | ne                                      | 11  |  |

| <b>2</b> | Real-World Hardware Trojans |                                                    |                                         | 13  |  |

|          | 2.1                         | Backg                                              | ground                                  | 14  |  |

|          | 2.2                         | Red 7                                              | Ceam vs. Blue Team ASIC Trojan Analysis | 18  |  |

|          |                             | 2.2.1                                              | ASIC Development Chain                  | 18  |  |

|          |                             | 2.2.2                                              | Experimental Setting                    | 19  |  |

|          |                             | 2.2.3                                              | Chameleon - The Target Circuit          | 21  |  |

|          |                             | 2.2.4                                              | Trojan Circuit                          | 23  |  |

|          |                             | 2.2.5                                              | Trojan Insertion Process                | 25  |  |

|          |                             | 2.2.6                                              | Measurement Setup                       | 27  |  |

|          |                             | 2.2.7                                              | Side-Channel Analysis (SCA) Results     | 30  |  |

|          | 2.3                         | Localization of FPGA Trojans Using Electromagnetic |                                         |     |  |

|          |                             | Radiation $(EM)$                                   |                                         |     |  |

|          |                             | 2.3.1                                              | FPGA Design Flow and Attacker Model     | 41  |  |

#### CONTENTS

|    |                | 2.3.2 T                                           | Trojan Circuit                                                                                                                              | 42 |  |  |

|----|----------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

|    |                | 2.3.3 N                                           | Aeasurement Setup                                                                                                                           | 43 |  |  |

|    |                |                                                   | Trojan Insertion Process                                                                                                                    | 45 |  |  |

|    |                | 2.3.5 N                                           | Ieasurement Results                                                                                                                         | 48 |  |  |

|    | 2.4            |                                                   | emarks                                                                                                                                      | 51 |  |  |

| 3  | An             | ASIC fo                                           | r Assessing DPA Countermeasures                                                                                                             | 53 |  |  |

|    | 3.1            | Introduc                                          | $tion \ldots \ldots$ | 54 |  |  |

|    |                |                                                   | Requirements and Vulnerabilities of Pervasive                                                                                               |    |  |  |

|    |                | E                                                 | Iardware Devices                                                                                                                            | 55 |  |  |

|    | 3.2            | DPA Co                                            | untermeasures                                                                                                                               | 56 |  |  |

|    |                | 3.2.1 H                                           | Iiding                                                                                                                                      | 56 |  |  |

|    |                | 3.2.2 N                                           | Iasking                                                                                                                                     | 57 |  |  |

|    | 3.3            | Keccak                                            | and the Sponge Family                                                                                                                       | 58 |  |  |

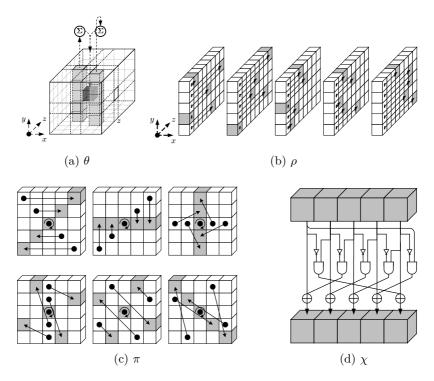

|    |                | 3.3.1 Т                                           | The Keccak- $f$ Permutation $\ldots \ldots \ldots$                                                                                          | 59 |  |  |

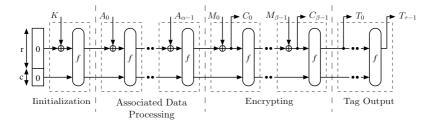

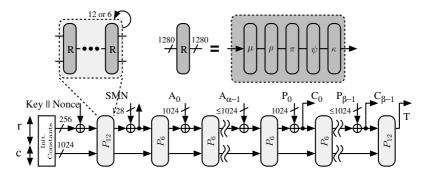

|    |                | 3.3.2 S                                           | PONGEWRAP                                                                                                                                   | 61 |  |  |

|    |                | 3.3.3 N                                           | Aasking the Sponge                                                                                                                          | 62 |  |  |

|    | 3.4            | ZORRO - An ASIC Assessment Platform for DPA Coun- |                                                                                                                                             |    |  |  |

|    |                |                                                   | res                                                                                                                                         | 63 |  |  |

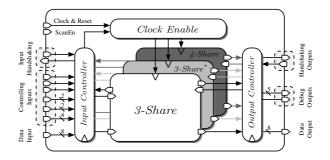

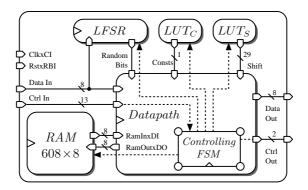

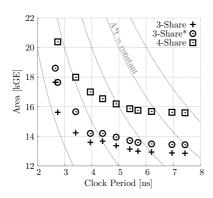

|    |                | 3.4.1 3                                           | R-Share, 3-Share <sup>*</sup> , and 4-Share Designs                                                                                         | 65 |  |  |

|    |                | 3.4.2 F                                           | AM Allocation                                                                                                                               | 68 |  |  |

|    | 3.5            | Results .                                         |                                                                                                                                             | 68 |  |  |

|    |                | 3.5.1 E                                           | Iardware Figures and Comparison                                                                                                             | 68 |  |  |

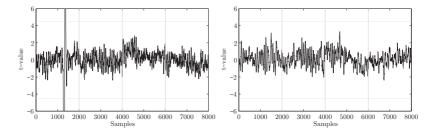

|    |                | 3.5.2 I                                           | DPA Attacks on ZORRO                                                                                                                        | 72 |  |  |

|    | 3.6            | Summar                                            | y                                                                                                                                           | 82 |  |  |

| Cl | hapt           | er Apper                                          | ndices                                                                                                                                      | 83 |  |  |

|    | 3.A            | Round C                                           | Deperations                                                                                                                                 | 83 |  |  |

|    | $3.\mathrm{B}$ | Data Tra                                          | ansfer Protocol                                                                                                                             | 84 |  |  |

| 4  | Hig            | h-Throu                                           | ghput AEAD Architectures                                                                                                                    | 87 |  |  |

|    | 4.1            | The CA                                            | ESAR Competition                                                                                                                            | 88 |  |  |

|    | 4.2            | Related                                           | Work                                                                                                                                        | 90 |  |  |

|    | 4.3            | Assuring                                          | g a Fair Comparison                                                                                                                         | 92 |  |  |

|    |                | 4.3.1 E                                           | Environmental Assumptions                                                                                                                   | 92 |  |  |

|    |                | 4.3.2                                             | General Architecture Requirements                                                                                                           | 93 |  |  |

|              |                | 4.3.3                  | Our Hardware Architectures                 | 95  |  |  |

|--------------|----------------|------------------------|--------------------------------------------|-----|--|--|

|              | 4.4            | Results and Comparison |                                            |     |  |  |

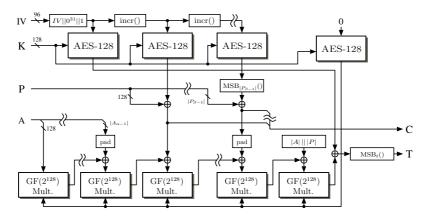

|              |                | 4.4.1                  | GCM-AES Reference Architecture             | 97  |  |  |

|              |                | 4.4.2                  | Data at Rest                               | 99  |  |  |

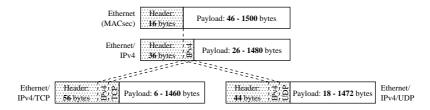

|              |                | 4.4.3                  | Data in Motion                             | 107 |  |  |

|              | 4.5            | Summ                   | ary and Discussion                         | 112 |  |  |

| Cl           | napte          | er App                 | oendices                                   | 115 |  |  |

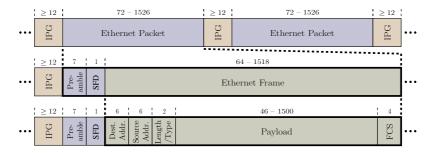

|              | 4.A            | 4.A Ethernet Revisited |                                            |     |  |  |

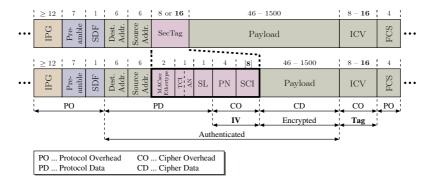

|              |                | 4.A.1                  | IEEE 802.1AE or MACsec Standard            | 116 |  |  |

|              | $4.\mathrm{B}$ | Enviro                 | onmental Assumptions (Extended Discussion) | 117 |  |  |

|              |                | 4.B.1                  | Data Stream Type                           | 117 |  |  |

|              |                | 4.B.2                  | Data Size Availability                     | 118 |  |  |

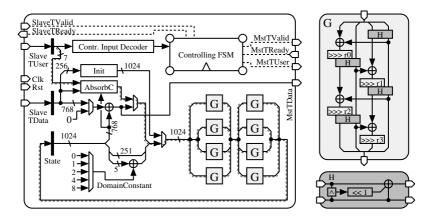

|              | $4.\mathrm{C}$ | AXI4-                  | Stream Architecture Interface              | 123 |  |  |

|              | 4.D            | Our A                  | EAD Architectures                          | 124 |  |  |

|              |                | 4.D.1                  | GCM-AES Reference Architecture             | 124 |  |  |

|              |                | 4.D.2                  | AEGIS and MORUS                            | 129 |  |  |

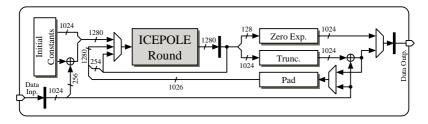

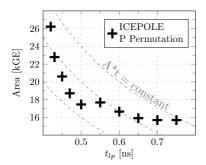

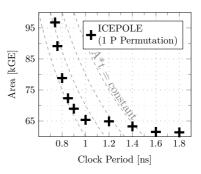

|              |                | 4.D.3                  | ICEPOLE                                    | 132 |  |  |

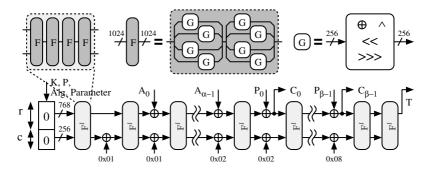

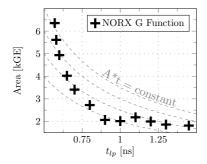

|              |                | 4.D.4                  | NORX                                       | 133 |  |  |

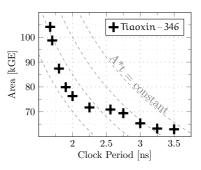

|              |                | 4.D.5                  | Tiaoxin-346                                | 135 |  |  |

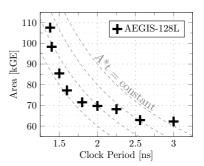

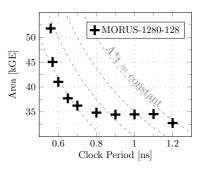

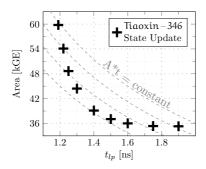

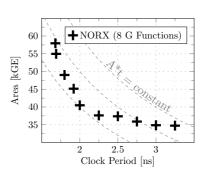

|              | 4.E            | Synthe                 | esis Results of CAESAR Candidates          | 137 |  |  |

| 5            | Cor            | clusio                 | ns and Future Directions                   | 141 |  |  |

| $\mathbf{A}$ | Cry            | ptogra                 | phic ASICs                                 | 149 |  |  |

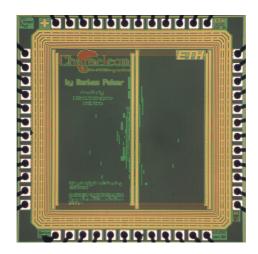

|              | A.1            | Chame                  | eleon/Chipit                               | 150 |  |  |

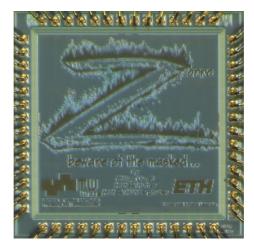

|              | A.2            | Zorre                  | Э                                          | 151 |  |  |

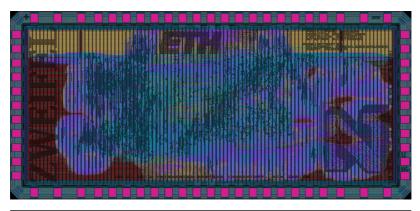

|              | A.3            | MLC:                   | ТіМ                                        | 152 |  |  |

|              | A.4            | Zweife                 | ı                                          | 153 |  |  |

| A            | erony          | /ms                    |                                            | 155 |  |  |

| Sy           | mbo            | ls                     |                                            | 159 |  |  |

| Oj           | Operators 1    |                        |                                            |     |  |  |

| Bibliography     | 163 |

|------------------|-----|

| Curriculum Vitae | 177 |

# Introduction

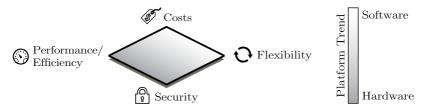

The complexity of today's applications in the field of Information and Communications Technology (ICT) increases continuously. Throughout a system's development and fabrication life cycle, typically software as well as hardware components from multiple parties are combined to fulfill the desired application requirements. As a result due to the high complexity of these systems, assuring a certain level of security has become a costly and non-trivial task. A major decision, which must often be taken very early in the development phase of an application is, whether the targeted functionality should be achieved using a software- or hardware-centric approach. The main aspects to be considered when taking such a fundamental decision are illustrated in Figure 1.1 and can be summarized as follows:

**Costs:** Like for many other applications, minimizing costs is often of highest priority throughout the development of a secure application. Although this aspect should only be secondary for security systems, it is often neglected as a result of bowing to pressure of management and marketing demands. Since devel-

Figure 1.1: Aspects to be considered when deciding among hardwareor software-centric approaches for security applications and the trend for the corresponding implementation platform.

oping hardware implementations requires substantially more effort compared to their software counterparts, it is often not even discussed whether software or hardware approaches should be favored. However, as briefly discussed in Section 1.1, developing *actually secure* software can become way more expensive than initially thought.

- Flexibility: While software in the testing or deployment phase can be updated at will, there is no (easy) way to apply changes to an Application-Specific Integrated Circuit (ASIC) after tape-out. Although today's Field-Programmable Gate Arrays (FPGAs) provide more flexibility by using electrical reconfiguration, they are inferior to software implementations in terms of flexibility. Hence, if frequent updates are necessary for a system, a softwarecentric approach is favored in most cases.

- **Performance/Efficiency:** As for performance and efficiency, hardware solutions are typically employed for two fields of application. First, when high performance in terms of *throughput* is of utmost importance, ASIC or FPGA systems significantly stay ahead of software alternatives. Second, if *peak power* or *energy consumption* must be considered as limiting factors, dedicated hardware implementations are usually employed. The efficiency achievable with ASIC implementations can hardly ever be reached with their software counterparts hosted on Commercials Off-The-Shelf (COTS).

Security: The last aspect, which often gets neglected during development, is the actually targeted security. The origin of secure software is typically a so-called *trust anchor*, from which trust gets inherited over several hierarchy levels. Trust anchors are often based on small hardware components, such as *Trusted Platform Modules (TPMs)*. From them, the trust is usually derived all the way through drivers, firmwares, and the operating system to a certain user application. Consequently, if security is one of the major goals, hardware-near solutions are more and more often favored since there is no need to trust the complete software stack.

Taking into account the four aspects mentioned above, a rough guideline can be that the more important performance, efficiency, and security are, the more hardware-near the platform should be (cf. Figure 1.1). Still, costs and flexibility should not be neglected completely in such a decision.

## 1.1 The Need for Hardware-Based Security Systems

General-purpose processors have evolved significantly over the last years. Because of the technology scaling of CMOS processes used for fabrication, the number of transistors has grown continuously according to Moore's Law [77] in the past. Due to the ever increasing integration density and the rising importance of security aspects, chip manufacturers have started to incorporate dedicated instructions for encryption operations. Most notable is the AES New Instruction Set (AES-NI), proposed by Intel in 2008 [50] and introduced into their Westmere processors in 2010. As a result, software implementations of security applications using such hardware-accelerated platforms already reach a high level of efficiency compared to their dedicated hardware counterparts, and this trend is to continue. Hence, the question arises for what type of applications is it actually still justifiable to build a hardware-centric rather than a software-based system.

As outlined in the previous section, performance, efficiency, and security are the main driving forces behind hardware developments. For smart cards or Radio-Frequency Identification (RFID) systems, as well as applications in the field of resource-constrained environments in general, the circuit complexity and the peak power or the energy consumed are often metrics of paramount importance. Since for such applications very high volumes are usually required, ASIC implementations are chosen most of the time. On the other end of the efficiency range, high-performance applications targeting throughputs of 100 Gbit/s and beyond can be found. For these systems circuit complexity, power, and energy are often secondary and are mostly only considered after reaching a certain throughput goal. Since the volume for these types of applications is sometimes significantly smaller than for resource-constrained environments, FPGA platforms are often considered as an alternative to ASIC implementations. Due to their reconfigurability, FPGAs offer a good trade-off between the high efficiency provided by hardware components and the flexibility of software. However, they typically lag behind their ASIC counterparts in terms of efficiency by approximately an order of magnitude [36].<sup>1</sup> In general, despite the fact that more and more security instructions are included into general-purpose processors, the performance and the efficiency of hardware implementations are still two of their major selling points. Especially for non-standard applications where efficiency is of high importance, dedicated hardware solutions should be favored.

Security and trust, on the other hand, are of growing importance for system designers. While hardware engineers can influence the resulting CMOS circuitry down to the gate level or even to single transistors, software developers are forced to use general-purpose processors, Graphics Processing Units (GPUs), or other COTS to realize their security application. As a result, the greater flexibility of the platform must be paid with costs for verifying its security, which are often not considered during design decisions. Although difficult to quantify in numbers, an industry rule of thumb exists, saying that to reach a security level of EAL6 costs about \$1000 per line of code [67]. It is

$<sup>^1\</sup>rm Recall$  that an FPGA is a VLSI chip by itself and thus, potential comparisons always depend on the technology the FPGA was fabricated in.

important to note that hardware architectures are not free from implementation errors which occur during the development of the Hardware Description Language (HDL) code of the circuit. However, all the hierarchy levels (e.g., the operating system, drivers, or third-party software libraries) lying in between a software implementation and the actual hardware executing the respective software must not be considered as potential weaknesses. Nevertheless, there are still quite a number of weaknesses in the life cycle of hardware-based systems, which might be the target of a potential attacker. Those weaknesses, potential countermeasures to get around them, as well as highly efficient VLSI implementations thereof are the main topic of the present thesis.

## 1.2 Cryptography Basics

The requirements of a security system can usually be broken down to a subset of the following basic cryptographic goals:

- **Confidentiality:** Only the parties designated to participate in a certain communication should be able to read the transferred data. Unauthorized parties must not be able to read them.

- **Integrity:** As soon as the messages being sent within a cryptographic system get modified, the participating parties should be able to recognize the modification.

- **Authenticity:** This goal is sometimes further split up into *entity* and *data authentication*. Entity authentication refers to the service that the parties communicating with each other convince the other participants of their identity. Data authentication means that when one party receives a message from another party, the receiver must be able to verify that the message indeed originates from the supposed sender.

- **Non-Repudiation:** As soon as a party sends a message to another party, the sender is not able to repudiate that the sent message does not originate from him.

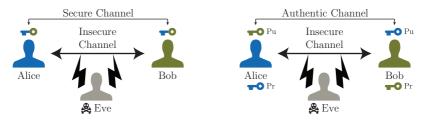

Figure 1.2: *Left:* Symmetric-key encryption scheme using a single shared secret cipherkey; *Right:* Public-key encryption scheme using pairs of private (Pr) and public (Pu) cipherkeys

Security by obscurity is often (mistakenly) applied in order to achieve one of the above mentioned goals or simply to increase the overall security of a system. However, as early as in the nineteenth century A. Kerckhoffs came up with a very fundamental principle, which should still be followed during the design of cryptographic applications these days:

**Definition 1.1** (Kerckhoffs' Principle). A system's security should only rely on the secrecy of the key being used. Hence, even if an attacker has a copy of the system, it should still be secure as long as he does not have access to the utilized key.

Throughout the last couple of centuries, two major types of security schemes have emerged to provide secure communication. First, symmetric-key approaches are based on the fact that the communicating parties share a common secret cipherkey, which is then used to assure services such as confidentiality and/or authenticity. *Public-key* systems, on the other hand, are based on a pair of keys for each participating party, one of which is kept secret (the private key) and the other one is made publicly available for everybody (the public key). Figure 1.2 illustrates both schemes with the two parties *Alice* and *Bob*, communicating over an insecure channel. This transmission might be intercepted by an attacker (*Eve*). Thanks to shorter keys, symmetric key approaches can achieve much higher efficiencies compared to their public-key counterparts. However, since for any communication pair a shared secret must exist, symmetric-key approaches suffer from the

#### 1.3. GOALS OF THE THESIS

problem of a more complicated key management. Also the distribution of the keys via an authentic communication channel prior to the actual data transmission becomes a challenging task.

Despite the key management challenges, when it comes to dataintensive communication systems these days, the public-key approach is mainly used during the setup phase of the transmission (e.g., to exchange a symmetric key). For the subsequent data transfer, however, symmetric-key algorithms are typically employed.

## 1.3 Goals of the Thesis

Due to the ever increasing complexity of systems in the field of ICT, it becomes more and more difficult (if not impossible) to provide secure applications. Although this thesis solely deals with vulnerabilities stemming from the hardware components of a system, it turns out to be alarming how sophisticated and powerful state-of-the-art attack scenarios are. This work was accomplished as part of a collaboration between industry and academia. The industrial party involved in the project was  $Omnisec \ AG$ , a Swiss company that provides hardwareaccelerated symmetric encryption solutions for governmental as well as defense markets. Therefore, this thesis deals with security issues to be considered throughout the development of VLSI-based encryption devices. Due to confidentiality issues, we could not work with the algorithms currently in operation at the industry partner. Hence, for each of the investigated attack scenarios we tried to find appropriate replacement candidates, which are expected to be of interest for both academia as well as industry. The major research questions of this thesis can be summarized as follows:

**Question 1.1.** How dangerous are hardware Trojans for VLSI-based devices and how practical are they?

ASICs and FPGAs are often used as core components of securitycritical applications these days. Therefore, their integrity with regard to fabrication (ASICs) and configuration (FPGAs) must be assured thoroughly. The term *hardware Trojan* has shaped parts of the security research community during several years now. Nevertheless, practical examples thereof are still rare and thus, detection methods are mostly evaluated using simulations or on FPGA platforms. We aim at answering this question by simulating an attack at the ASIC development chain, thereby tackling the problem of untrustworthy foundries. With the use of non-destructive detection techniques, we analyze our ASICs and try to distinguish genuine from malicious samples. Moreover, we do not only focus on the detection of hardware Trojans, but also provide first suggestions on how to actually localize unintended malicious logic components.

**Question 1.2.** Are state-of-the-art Differential Power Analysis (DPA) countermeasures of embedded devices ready to withstand sophisticated attack scenarios, and what is the price we have to pay for them?

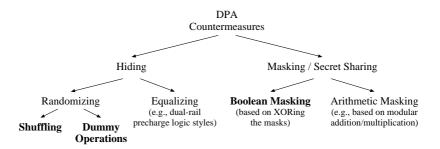

Symmetric encryption devices suffer from the problem of key distribution. Unless cipherkeys are distributed among the communicating parties electronically with the use of a public-key infrastructure, physical devices such as smart cards or similar hardware tokens are used. With the adoption of *keyed devices*<sup>2</sup>, which are often more easily available to the general public, implementation attacks<sup>3</sup> become a major threat. DPA has emerged as one of the most powerful methods to reveal secret internals based on the leakage of side-channel information. With the use of an emerging Authenticated Encryption (AE) system, we aim at answering the question how well DPA countermeasures like *hiding* or *masking* work on an actually fabricated ASIC. Moreover, we want to compare those countermeasures with regard to their resource requirements needed to achieve the DPA protection.

**Question 1.3.** Can future AE algorithms keep up with today's standards in terms of their hardware efficiency from a VLSI perspective?

The Galois/Counter Mode of Operation (GCM) using the Advanced Encryption Standard (AES) as the underlying block cipher can be considered as one of the de-facto AE standards available in today's security applications. The *Competition for Authenticated Encryption: Security, Applicability, and Robustness (CAESAR)* aims at

$<sup>^2\</sup>mathrm{By}$  keyed devices we refer to hardware components that process any kind of sensitive data such as secret keys or plaintexts.

$<sup>^3</sup> Implementation attacks are attacks that do not target an algorithm by itself, but the actual implementation of it on a certain device.$

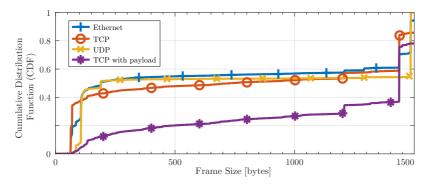

finding potential alternatives or even successors. Our goal is it to seek for the most promising candidates of the competition to be used in high-performance VLSI architectures. We do not only investigate the candidates regarding their asymptotic performance<sup>4</sup>, but use stateof-the-art communication protocols to analyze them under real-world conditions. For that, packet size distributions of protocols from different OSI layers are considered, including Ethernet and TCP.

### **1.4** Contributions

The main goal of this thesis is to investigate potential attack scenarios for symmetric AE systems from a hardware developer's point of view. Additionally, its focus lies on designing high-speed VLSI architectures of potential future AE systems. Therefore, several algorithms from the CAESAR competition are studied with regard to their hardware performance, targeting throughputs of 100 Gbit/s and beyond. Summarizing, the major contributions of this work are as follows:

• Hardware Trojan detection on an actual ASIC: Detection of Trojans in the field of VLSI designs has previously either been conducted with FPGA platforms or based on simulations. The main reason for this is that a genuine and a malicious ASIC are not normally available for analyses purposes. Our tapedout chips, called *Chameleon* and *Chipit*, represent one of the very rare known such pairs of chips. Both contain an AESbased cryptographic primitive. While Chameleon solely hosts the genuine design, in Chipit a Denial-of-Service (DoS) hardware Trojan has been implanted in the interface of the chip. Insertion of the malicious circuitry was accomplished solely on the layout data of the design, assuming no special knowledge about the actual internals of the genuine architecture.

Using several Side-Channel Analysis (SCA) techniques based on dissipated power, we demonstrate that despite the very small size of the Trojan, occupying less than 0.5% of the area of the

$<sup>^4\</sup>mathrm{By}$  asymptotic performance we refer to the use case where very long input messages are available to be processed.

genuine design, its detection is actually feasible with a comparatively simple measurement setup. The presented ASICs have already been acquired by other research institutions [38] to study hardware Trojan detection techniques other than SCA fingerprinting based on power.

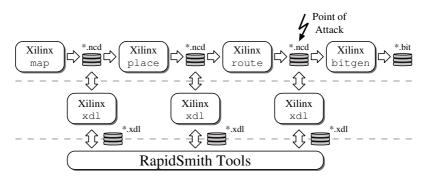

• Localization of FPGA Trojans using Electromagnetic Radiation (EM): FPGAs are another potential target for the implantation of malicious circuitries. Related work from previous years [79, 80, 81] has shown that the bitstream encryption process of FPGA vendors cannot be considered to be perfectly secure. As a result, the configuration stream for an FPGA might be altered by an attacker unnoticed to insert additional, malicious circuitry in the FPGA.

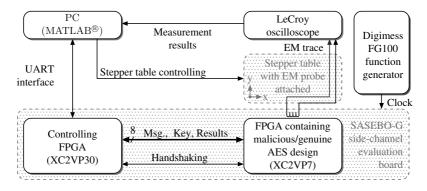

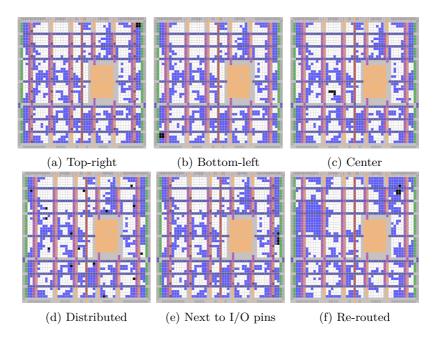

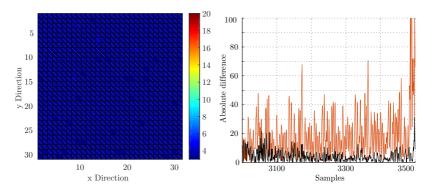

Based on a post-placement insertion flow, we propose to use the picked-up electromagnetic radiation not only for distinguishing malicious from non-malicious configurations, but also to actually localize the Trojan on the device. By inserting the same DoS Trojan at different locations on the FPGA, we demonstrate that detection is independent from the actual location of the Trojan within the configurable logic. Although we successfully identified the malicious designs using EM fingerprinting on a Xilinx FPGA, we fell short of pinpointing the exact location of the Trojan logic by stepping over the packaged Integrated Circuit (IC) with a near-field probe.

• ASIC-based DPA countermeasures evaluation platform: DPA can be considered to be one of the major analysis methods that has lead to numerous practical attack scenarios on secret-key-processing cryptographic hardware devices in the recent past.

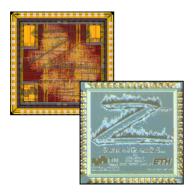

As a result, we have developed ZORRO, an ASIC serving as an evaluation platform for DPA countermeasures. It contains three independent, permutation-based AE primitives using KECCAK-f as the underlying permutation, which differ with regard to the utilized masking scheme. All designs provide both hiding as well as masking countermeasures that can be enabled or disabled at will. Our ASIC has been developed for applications in

the field of resource-constrained environments. Hence, low circuit complexity was one of our main design goals. We demonstrate that neither hiding nor masking alone are sufficient as DPA countermeasures to withstand attacks on ZORRO with up to 100 000 traces.

• High-performance hardware designs of AE algorithms: GCM-AES represents a de-facto standard when it comes to AE algorithms with Associated Data (AD). The CAESAR competition aims at finding a potential portfolio of successors or at least alternatives to GCM-AES, since the latter has suffered from several security flaws in the past [69, 29, 113, 32, 96, 42] and also a need for more efficient algorithms emerges.

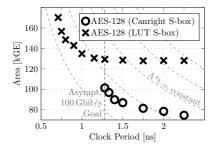

We contribute to the competition by analyzing several of the second-round CAESAR candidates with regard to their suitability for high-throughput hardware designs. More specifically, we target applications with data rates of 100 Gbit/s and even beyond, which are expected to play a major role in the upcoming years. We compare those competitors against a GCM-AES reference design as well as against each other under two different use cases in terms of the circuit complexity required to reach the target throughput of at least 100 Gbit/s. The two scenarios in question are the so-called *data at rest* scenario and the *data* in motion use case, for which we use Ethernet as an example protocol. Based on a mature 65 nm ASIC technology, we show that although many of the competitors result in better hardware efficiency for the data at rest use case, most of their advantages significantly diminish when it comes to more practical data in motion scenarios like Ethernet.

## 1.5 Outline

This thesis can be subdivided into three main chapters, each of which gets identified by an icon. Each such icon refers to one phase in the life cycle of a VLSI-based encryption device, where the respective attack scenarios or performance metrics need to be considered. Manufacturing. In Chapter 2, we investigate hardware Trojans for both ASICs and FPGAs. After some background information on hardware Trojans in general, we first present an ASIC Trojan, which we implanted into a genuine AES architecture on the mask level. With the use of side-channel fingerprinting techniques we then classify the actually fabricated genuine and malicious chips both with and without the use of a golden IC. Moreover, we propose to use EM not only for Trojan detection, but also for the localization of the hidden logic based on Trojans implanted into already placed-and-routed FPGA configurations.

**Operation.** Implementation attacks and their countermeasures, which must be considered for any keyed cryptographic primitive, are covered throughout Chapter 3. In order to analyze DPA countermeasures on an actual ASIC, we introduce

our ZORRO chip, providing hiding and masking techniques that can be enabled or disabled at will. Next, we present the hardware figures of this smallest, DPA-secured ASIC architecture of a keyed, KECCAK-based AE scheme available to date. Using an appropriate measurement setup, we then compare the attack resistance of the different countermeasures.

**Performance.** Chapter 4 deals with current and potential future AE algorithms to be used in high-performance ASIC architectures. Since these days, GCM-AES represents one of the favored primitives in this domain, we first present a reference architecture reaching an asymptotic throughput of at

least 100 Gbit/s based on a mature 65 nm CMOS technology. Next, we provide high-performance VLSI designs of several of the participants of the CAESAR competition and compare them against our GCM-AES reference design. We also analyze the resulting performance of the investigated candidates under real-world conditions using stateof-the-art communication protocols such as Ethernet or TCP.

Finally, in Chapter 5 we draw overall conclusions about the topics treated in this thesis and give suggestions for potential future work.

# Real-World Hardware Trojans

**Outline.** We begin this chapter with a general introduction about hardware Trojans in Section 2.1. Throughout Section 2.2, we present one of the very rare, actually taped-out ASIC Trojans. We discuss how we inserted the Trojan on the mask layer, thereby tackling the so-called *untrustworthy manufacturer problem*. Moreover, we provide details about our detection process based on side-channel fingerprinting. In Section 2.3, we investigate the detection of FPGA Trojans using Electromagnetic Radiation (EM) as a side channel. For that we insert a Trojan into a placed-and-routed FPGA bitstream. We propose to use EM not only for distinguishing malicious and genuine FPGA configurations, but also to actually localize the Trojan circuitry within the FPGA. After all, we provide final remarks about our hardware Trojan analysis in Section 2.4.

| System house                                                                                                                     | IP vendor(s)                                           | Design house(s)                                                                                                                                                                                 | EDA vendors                                                | Library vendor                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| System-level<br>evaluations,<br>algorithm design<br>Specs<br>Chip planning,<br>archit. design,<br>behav. modeling<br>HDL<br>code | Virtual comp.<br>(hardware models<br>ready for synth.) | HDL synthesis,<br>funct. verific.<br>design for test<br>Netlist<br>Floorplanning,<br>place and route,<br>clock tree gen.<br>Layout<br>DRC and LVS,<br>post-layout<br>timing verific.<br>Tapeout | Standard<br>CAE tools<br>Standard<br>CAD tools<br>Sign off | Cell library<br>and macrocells<br>ASIC manufact.<br>or silicon foundry<br>together with others<br>Technology<br>files<br>IC manufact.,<br>testing, and |

| System                                                                                                                           | 1                                                      |                                                                                                                                                                                                 |                                                            | packaging                                                                                                                                              |

| integration                                                                                                                      | <br> <br>                                              |                                                                                                                                                                                                 |                                                            |                                                                                                                                                        |

Figure 2.1: Parties involved and their responsibilities of a cell-based, full-custom ASIC development (illustration adapted from [63]).

## 2.1 Background

Throughout the last decade, trustworthiness in hardware components got more and more important as these components must provide a reliable basis for their software counterparts [40]. Development and fabrication of modern VLSI circuits for both ASIC and FPGA platforms rely on an ever increasing set of active participants to manage both costs and complexity. Figure 2.1 illustrates the parties involved and their responsibilities of a typical cell-based, full-custom ASIC development. More often than not, large parts of the design are outsourced to specialist teams all around the world, pre-designed Intellectual Property (IP) blocks from different vendors are added to the design, and complex Electronic Design Automation (EDA) software is used in the design flow for synthesis and analysis purposes. Finally, in the occurrence of ASIC development, a specialized semiconductor foundry is responsible for the actual manufacturing of the IC, including wafer processing, packaging, and testing.

ASIC and FPGA fabrication are based on the same CMOS manufacturing process. This process must be considered as a point of attack where a potential adversary may intrude the life cycle of a security-critical hardware device. The complex fabrication of ASICs and FPGAs provides a skilled adversary various possibilities for inserting a (relatively small) circuit that can remain undetected during the design and verification process. Such a malicious hardware circuitry— also known as a *hardware Trojan* [41]—would then be manufactured together with the actual circuit and can be used for different purposes, such as:

- Altering the specification or reliability: Trojans may slightly change the intended functionality of a circuit or compromise the performance by altering the physical characteristics of a design (e.g., narrowing certain wires to accelerate aging).

- **Denial-of-Service (DoS) attacks:** A malicious circuit causing a complete failure of a design is referred to as a *DoS Trojan*.

- Leaking information: If a design is intended to process any kind of sensitive data such as secret keys, a Trojan may leak this information, for instance, over some sort of side channel.

For additional information about the effects of hardware Trojans, we refer the reader to [108]. Since the complexity of ASICs continues to increase driven by competitive market pressure, more and more opportunities for an attacker to insert a Trojan emerge. This is due to the following factors:

• While IT circuits continue to grow in complexity, the size of hardware Trojans does not necessarily increase proportionally. Therefore, detecting an unwanted circuit smaller than, say, one millionth of the original circuit becomes a challenging task.

- Basically, the high costs for developing an ASIC can be justified in two situations. On the one hand for systems where the absolute performance of speed, area, energy efficiency, or security is of paramount importance. On the other hand for very high-volume fabrication, where millions of ASICs are to be sold. Both cases are attractive targets for adversaries, as ASICs often constitute either the most important part of a system or are widely deployed and thereby compromise a large number of systems.

- As the expected harm caused by a compromised device is very high, adversaries can afford to invest significant sums into designing and inserting hardware Trojans.

At the same time, ASIC designers face considerable challenges to verify the correct functionality of their own (genuine) circuits properly. Even the most modern verification flows do not stand much chance to detect hardware Trojans inserted by determined adversaries. That is why hardware Trojan detection has attracted significant interest in recent years.

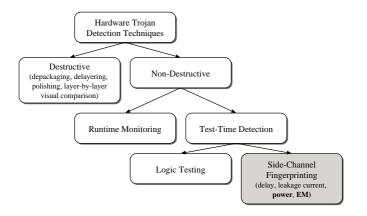

**Trojan detection techniques:** In general, Trojan detection approaches can be classified into destructive and non-destructive methods as depicted in Figure 2.2. Destructive techniques include depackaging, delayering, and various mechanical and/or chemical steps. Eventually, the exposed layers of an ASIC are visually compared against the original Graphic Database System II (GDSII) layout data to find any malicious alterations. However, these techniques are very time-consuming and rather expensive, especially for modern manufacturing processes [112]. Hence, for small- and mid-sized hardware companies, destructive techniques are hardly affordable.

Within the group of non-destructive techniques, one can differentiate between detection approaches carried out during runtime or as part of testing. Both runtime monitoring and logic testing, which belongs to the test-time approaches, are referred to as *invasive* methods, since they require additional test circuitry to detect a Trojan. Side-channel detection methods [6], on the other hand, are based on building a fingerprint using physical characteristics of a Circuit Un-

#### 2.1. BACKGROUND

Figure 2.2: Taxonomy of hardware Trojan detection techniques [109].

der Test (CUT). Typical side channels used for this approach are delay [73, 61], leakage current [3], (dynamic) power, or Electromagnetic Radiation (EM) [6]. Moreover, Narasimhan et al. [89] proposed to combine different side channels in order to improve the detection ratio. In our experiments, we focus on power and EM as side channels to detect the ASIC and FPGA Trojans, respectively.

**Design type notation:** During the remainder of this chapter, we refer to the different designs of actually fabricated ASICs or FPGA configurations using the following notation.

- **Original design:** The pristine design as intended by the system house is referred to as the *original* circuit.

- **Circuit Under Test (CUT):** After the fabrication of an ASIC, the integrity of the circuit needs to be verified. The same applies following the configuration of an FPGA. At this stage, we denote the designs as *Circuits Under Test (CUTs)*.

- **Genuine design:** Once a CUT is proven to be Trojan-free, we refer to it as being *genuine*.

- Malicious design: If a CUT contains a Trojan, it is considered to be *malicious*.

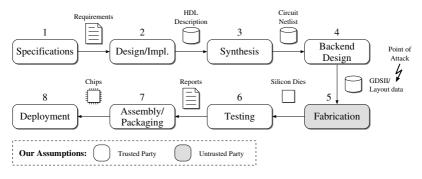

Figure 2.3: Simplified overview of the design phases of today's ASIC development chains and their respective outputs and our assumptions regarding their trustworthiness.

## 2.2 Red Team vs. Blue Team ASIC Trojan Analysis

Despite the huge amount of related work carried out on hardware Trojans and their detection, most work has been accomplished based on FPGA platforms or ASIC simulation results only. Therefore, we decided to set up an experiment similar to the untrustworthy manufacturer problem, putting ourselves into the role of a fabless customer and an adversarial foundry. Compared to previous experiments, our approach tries to answer the question if Trojan insertion during fabrication and subsequent detection can be carried out successfully for a real-world design under the restrictive time schedule of the ASIC manufacturing process.

#### 2.2.1 ASIC Development Chain

Assume a simplified ASIC development chain as depicted in Figure 2.3. After initially determining the specifications of a design, it is usually captured using a Hardware Description Language (HDL). Next, the HDL description gets synthesized into a netlist of standard cells. The subsequent step is to generate the physical mask layout that will be used as a blueprint for manufacturing the IC. Finally, wafer processing takes place, eventually resulting in individual dies that are tested, packaged, and delivered to the customer.

An adversary may target any of the design stages outlined in Figure 2.3. From stage 2 to stage 4, the technical requirements continue to increase and smaller companies usually need to outsource portions of the design flow to more specialized enterprises. Larger firms outsource at least the actual IC manufacturing to one of the very few semiconductor foundries. The last step at which a hardware Trojan can be inserted into the ASIC is just prior to *Fabrication*. Assume an attacker, who is not part of the design team, intercepts the development of an ASIC at this stage. Usually, such an adversary knows very few technical details about the target design and will have only limited time to analyze the target circuit and to insert the Trojan. Otherwise, the disruption of the tight manufacturing schedule will raise suspicion. However, if inserted at this late stage, there will be virtually no opportunity for the system house (i.e., the party commissioning the ASIC) to detect the Trojan before measuring the fabricated samples.

For our investigations, we considered fabrication to be the only untrustworthy stage. We believe that it is one of the most vulnerable phases in an ASIC's life cycle, since many people from third parties are involved. Moreover, monitoring the whole fabrication phase, including mask generation and wafer processing, is too expensive for most fabless hardware firms.

#### 2.2.2 Experimental Setting

To tackle the so-called *untrustworthy manufacturer problem*, we initiated an experiment. We tried to imitate an attack as realistically as possible and therefore, set up a *red team vs. blue team* approach based on the following two teams:

**1.** Blue team: In our experiment, the blue team acts as the *blue-eyed* system house, aiming at building an ASIC, expecting the following assumptions and responsibilities:

- As a first step, the blue team develops the original design all the way down to the detailed layout (in GDSII format), which they send to the foundry for fabrication.

- Since the blue team is a fabless system house, they have to trust several third parties to get their design manufactured.

- Once the blue team gets back their chips, they are responsible for devising an adequate measurement setup to analyze the ICs using a non-invasive, side-channel-based analysis approach.

- Using certain post-processing techniques, this team should build hypotheses regarding which ASICs represent genuine designs and which contain malicious circuitries, respectively.

2. Red team: The red team, on the other hand, assumes the role of the adversarial party located at the foundry. It is expected to fulfill the assumptions and responsibilities given below:

- The red team is assumed to only have access to the mask-layout (data typically in GDSII format) sent for fabrication by the blue team.

- We do not expect the red team to have any detailed knowledge about the target design, since such knowledge would assume *insider information* from the blue team.

- Although such information can be reverse engineered by a sophisticated attacker, it is usually a very time consuming task. Since the fabrication process of an ASIC normally already has a very tight schedule, any additional delays may raise undesirable suspicions.

- The red team is responsible for the development of the Trojan circuit. As target-independent hardware Trojans can be designed prior to an actual attack, their development does not cause any major delay.

#### 2.2. ASIC TROJAN ANALYSIS

| Property                        |                       |

|---------------------------------|-----------------------|

| CMOS technology                 | 180 nm                |

| Supply voltage (core/pads)      | $1.8/3.3\mathrm{V}$   |

| Core area                       | $38000\mathrm{GE}$    |

| Maximum frequency $(f_{max})$   | $125\mathrm{MHz}$     |

| Latencies (incl. I/O interface) |                       |

| $AES encryption^1$              | 945 cycles            |

| $AES decryption^1$              | 1558 cycles           |

| Grøstl hashing <sup>1</sup>     | $3465\mathrm{cycles}$ |

Table 2.1: Key properties of Chameleon, the target ASIC for the Trojan insertion.

$^1$  Applies for both standalone and GrÆStl version.

• Finally, the red team actually inserts the Trojan into the target design. Due to the tight schedule of an ASIC fabrication, we limit the amount of time for the insertion to a handful of working days.

#### 2.2.3**Chameleon - The Target Circuit**

For our investigations, we could have chosen any existing ASIC design with a well-defined interface, regardless of its functionality. We had access to a number of designs that were due to be submitted for fabrication. Our victim circuit, called *Chameleon* [97], was designed independently prior to this work and includes the following three cryptographic cores<sup>1</sup> that share peripheral circuits and a common top-level controller:

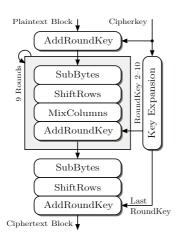

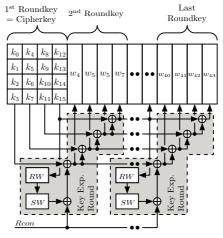

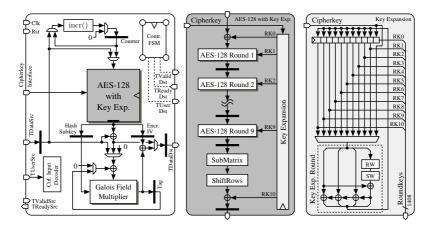

1. The first core is a standalone, low-area implementation of the Advanced Encryption Standard (AES) [94], targeting applications in resource-constrained environments.

<sup>&</sup>lt;sup>1</sup>Choosing a cryptographic design has made some of the choices in the project simpler. However, our approach is generic enough, and we are confident that we would have achieved similar results with most other designs as well.

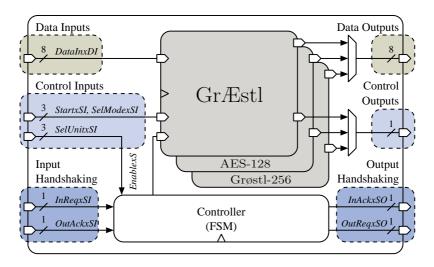

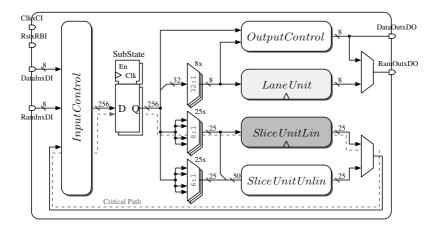

Figure 2.4: Chameleon top-level hierarchy, showing independent designs and interfaces; clock and reset signals are omitted

- 2. The second core implements an iterative version of the cryptographic hash function Grøstl [46], which was one of the finalists of the SHA-3 hash competition [93] organized by the National Institute of Standards and Technology (NIST).

- 3. Eventually, the third design on Chameleon is called *GrÆstl* and combines both AES and Grøstl in a single optimized datapath. Since the two cryptographic primitives share similar core components, the resulting GrÆstl architecture provides both a block cipher and a hash algorithm with only very little overhead in terms of silicon area compared to the standalone versions.

All three cores are completely independent of each other. The chip is configured to run only one of the cores at a time. Key data of the Chameleon implementation are given in Table 2.1.

Figure 2.4 shows the top-level architecture of Chameleon, which communicates with its environment based on an eight bit wide I/O interface. A four-phase handshaking protocol was implemented to control the data flow. The signals InReqxSI, InAckxSO and OutReqxSO,

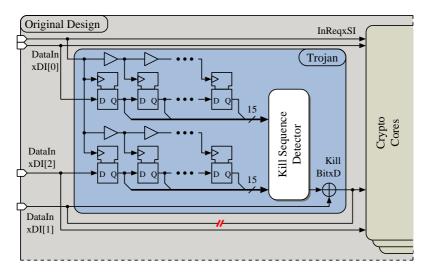

Figure 2.5: The structure of the DoS hardware Trojan and how it got implanted into the original design. The combinational logic for the kill sequence comparator consists of about 10 logic gates.

**OutAckxSI** control input and output handshaking, respectively. For Trojan insertion, the red team used no design-specific information other than the four-phase handshaking signals as will be discussed in the following subsection. Strictly speaking, this information is not available from layout data. Yet we believe that it is straightforward to extract this information, either through cursory examination of the circuit or through ancillary data such as pin names or from the supporting documentation.

#### 2.2.4 Trojan Circuit

The goal of the red team was to design a Trojan difficult to detect. This called for an extremely small circuit. Hence, we decided to integrate the DoS Trojan illustrated in Figure 2.5. The Trojan observes certain inputs of the original circuit and waits for a specific *kill sequence*. Once detected, another input bit of the original circuit is flipped, which causes functional failure in the following clock cycles, resulting in a DoS attack. Unlike many published hardware Trojans, this design is continuously active and is placed into the peripheral logic of the ASIC. This resulted from the fact that we did not want to expect the adversary to have deep knowledge of the internals of the design, as such information could be difficult or even impossible to obtain.

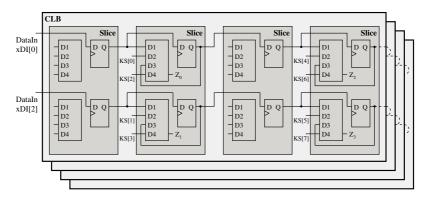

Since the kill sequence is observed through a serial 8-bit interface, there is a trade-off between the size of the Trojan circuit and the length of the kill sequence. For this design a 30-bit sequence<sup>2</sup> was used, i.e., the same number of Flip-Flops (FFs) were needed, which made up the majority of the area of the hardware Trojan. The Trojan was designed to tap into two input bits in parallel (InxDI[0] and InxDI[2]), resulting in the architecture shown in Figure 2.5. The wires required to connect the Trojan to the target design were placed close to the original connections and added very little additional load to the circuit. The input sequence, obtained during multiple read cycles, is continuously compared to the kill sequence—which got assigned the hexadecimal value 0x0DDDDDD<sup>3</sup>—using a simple combinational circuit. As soon as the sequence is detected, data input InxDI[1] is inverted. Once again, there is very little intrusion to the original circuit; only an XOR gate is inserted into an external I/O path that typically is off the timing critical path anyway.

One remaining problem with regard to the Trojan insertion was the clock connection needed for the FFs used in the design. The red team chose not to use the regular clock signal, but instead used the input signal InReqxSI of the original circuit. This signal is set once a new valid data item is present on the input and thus, can directly be used as the clock for the Trojan circuitry. Additional buffers were inserted manually in the clock path of the Trojan to reduce the load on the InReqxSI signal.

<sup>&</sup>lt;sup>2</sup>In our case, we knew that the chip would not undergo exhaustive functional tests after production, so we were able to use a slightly shorter sequence to keep the Trojan area small. In a more realistic scenario, our victim circuit would also be more complex, allowing us to hide a longer kill sequence that would withstand even a very thorough functional test with a higher probability.

$<sup>^3 \</sup>rm Since$  the kill sequence is only 30 bit and not 32 bit long, the first two zeros are truncated from that value.

#### 2.2. ASIC TROJAN ANALYSIS

Many hardware Trojan taxonomies exist in the literature (see, for instance, [115, 35, 65]). According to those, our Trojan can be classified as follows:

| Design phase:      | Fabrication          |

|--------------------|----------------------|

| Activation:        | Externally triggered |

| Effect:            | Denial-of-service    |

| Location:          | I/O                  |

| Abstraction level: | Gate level           |

### 2.2.5 Trojan Insertion Process

The actual insertion process of the Trojan, accomplished by the red team, was performed in three steps:

- 1. First, we identified the I/O pads and followed their connections. The input and output circuitries of an ASIC can easily be identified and distinguished by anyone who has access to the masklayout (due to, for instance, different transistor sizes). Furthermore, common standard cells such as FFs can be detected with relative ease by an experienced layout engineer. This also leads to the identification of critical nets such as clock and reset. We had to find four signals: one for the clock, two for the kill sequence observation, and one that will be flipped by the kill switch. Once some candidate I/O signals were identified, a suitable region on the ASIC was searched for the insertion of the Trojan cells. The goal was to find an area that was close to the connections of the target design and had sufficient room to accommodate the logic gates of the Trojan. The approximate area is highlighted in Figure 2.6.

- 2. In the second step, we removed some of the filler cells<sup>4</sup> of the Chameleon design to make room for the Trojan circuit.

- 3. Finally, the signal and clock routing was completed using the available gaps in the actual circuit. The manual routing was accomplished mainly on inner metal layers, namely on layer three

<sup>&</sup>lt;sup>4</sup>Filler cells are added to a design during place and route to improve certain electrical characteristics. They do not affect any functionality.

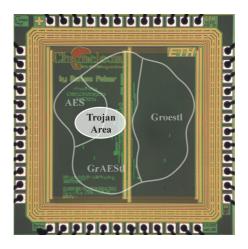

Figure 2.6: Chip photo of the fabricated Chipit ASIC.

and four of the utilized six-metal-layer technology in order to thwart potential visual inspections (not assuming the use of sophisticated delayering techniques). We cut through the original connection of input InxDI[1] (i.e., the *kill bit*) and connected the combinational logic as well as the shift registers of the Trojan by adhering to the design rules of the target technology.

All these steps were accomplished on the mask data in GDSII format exclusively. Therefore, any mistake during the Trojan insertion can lead to a total failure of the original circuit, which would most likely expose the attacker. As such, the adversary requires considerable technical skills to perform the attack. The data was read into Cadence Design Systems Virtuoso 5.1.41 EDA design software and the modified layout was exported in GDSII format again. Both Chameleon and its malicious counterpart *Chipit* were then fabricated using the 180 nm CMOS process by United Microelectronics Corporation (UMC). Figure 2.6 shows a photo of Chipit with the three independent components and the approximate area where the Trojan cells are inserted highlighted. Due to the integration of 30 FFs, the resulting Trojan requires a *comparatively large* area, i.e., about 190 GE, which is equal to 0.5% of the overall Chameleon design.

| Design    | Trojan | Chips              |  |  |

|-----------|--------|--------------------|--|--|

| Chameleon | no     | #2, #3, #5, #6, #8 |  |  |

| Chipit    | yes    | #1, #4, #7         |  |  |

Table 2.2: Distribution of chips for measurement.

### 2.2.6 Measurement Setup

In total, around 60 chips of both Chameleon and Chipit were manufactured. Out of these a mix of eight chips were bonded in a QFN56 package. That set contained three malicious and five genuine chips as listed in Table 2.2. These were then handed over to the unsuspecting blue team for testing. The blue team was given the datasheet for Chameleon and designed a test setup to correctly run the chip. No additional information about the mix of genuine and malicious ICs were relayed from the red team to the blue team until the end of the study. The eight chips were tested as described in the following sections.

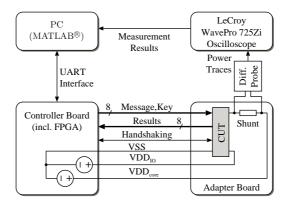

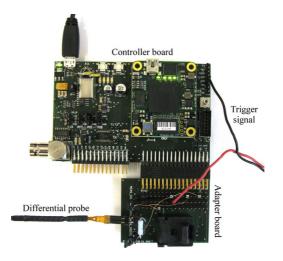

The blue team's measurement setup mainly consisted of four parts: an adapter board with a socket for our (Trojan infected and noninfected) ASICs, a controller board, a digital oscilloscope, and a Personal Computer (PC). In order to perform side-channel analyses, we decided to design a Printed Circuit Board (PCB) that allows flexible power measurements using a QFN56 socket. This PCB was connected to a controller board. The controller board features an FPGA that was needed to provide all necessary interface signals to Chameleon/Chipit. The controller board was then connected to a PC that governs the overall measurement process. We used MATLAB<sup>®</sup> as it offers sophisticated analysis tools to perform side-channel analyses. Figure 2.7 shows a simplified overview of our setup. In the following, we describe the components and connections in more detail.

Adapter board: The adapter board has 51 pins that connect the CUT with the controller board. Only 48 pins were used by the CUTs; the remaining pins are still connected but were not used in our experiments. The main component of the adapter board is the QFN56

Figure 2.7: Simplified measurement setup for Trojan detection.

socket, required to easily exchange the individual CUTs. To measure the power consumption, the board provides three additional pin headers: one ground, one VDD<sub>IO</sub>, and one VDD<sub>core</sub> pin header. Therefore, the voltage drop across a measurement resistor can be measured with the oscilloscope in the ground or power lines of the I/O and core supply of the CUT. In our experiments, we measured the voltage drop across a 1 $\Omega$  shunt resistor in the VDD<sub>core</sub> line because it contained less noise from the ground or I/O communication. In addition to the power measurement pins, all I/O pins of the CUT are available as pin headers to facilitate triggering on different I/O signals, for instance, on the start signal of the AES implementation (StartxSI).

**Controller board:** A photo of the controller and adapter board is given in Figure 2.8. The controller board communicated with a PC running MATLAB<sup>®</sup> via a Universal Asynchronous Receiver/Transmitter (UART) interface. A Xilinx Spartan-6 FPGA represents the core component of the controller board, which allows fully flexible pin assignments and controlling. In addition to the UART interface, it implemented the communication with the CUT using the following protocol: First, we selected the proper mode of operation of the CUT. We decided to target the stand-alone version of AES (SelUnitxSI = 1) and performed encryptions only (SelModexSI = 0). Second, the

Figure 2.8: The controller board and the adapter board including the QFN56 socket for the CUTs.

PC sent a 128-bit AES key and a 128-bit plaintext block to the controller board. The data was stored in a 256-bit register and split into 8-bit chunks to interface with the CUT. Following the AES encryption, the ciphertext was again memorized in an internal register and transferred back to the PC. To verify the correctness of the ciphertext, it was compared against a reference software implementation.

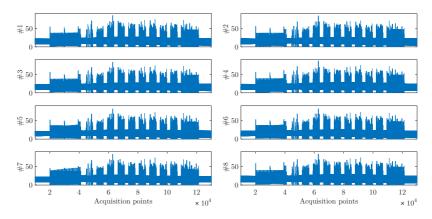

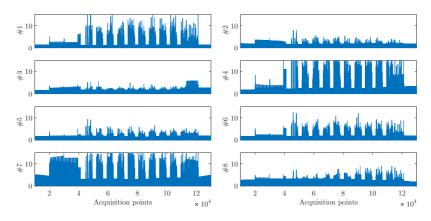

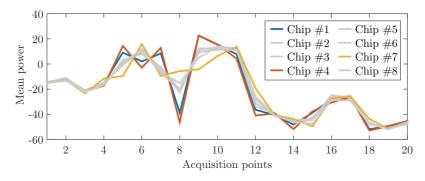

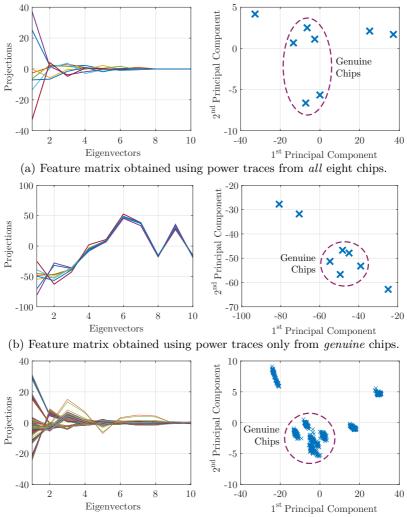

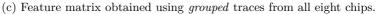

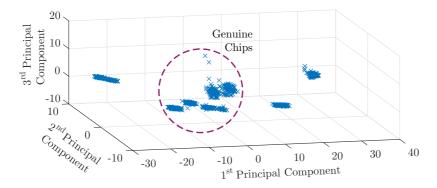

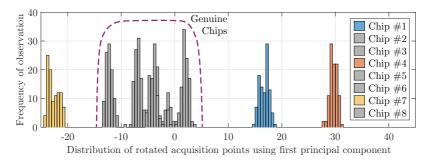

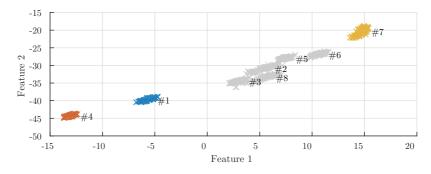

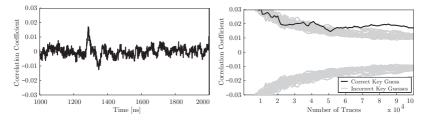

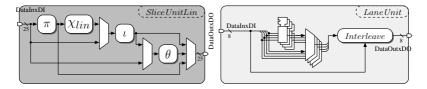

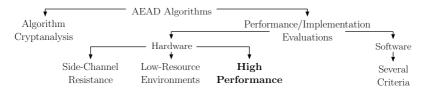

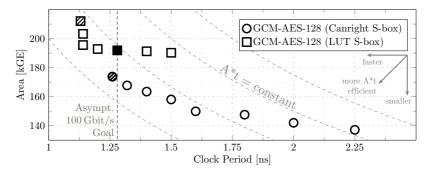

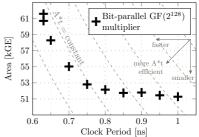

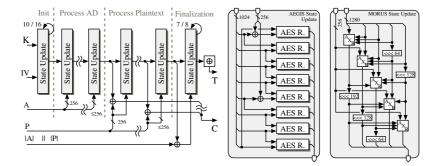

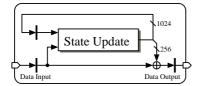

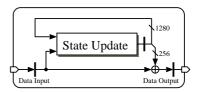

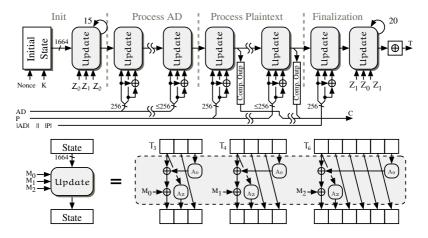

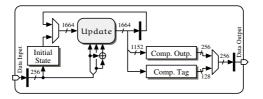

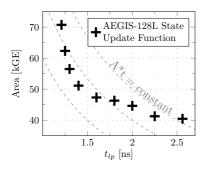

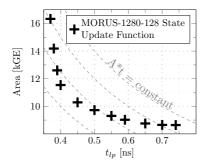

Power consumption was measured using a LeCroy WavePro 725Zi oscilloscope. We used a sampling rate of 1 GS/s and captured the entire AES encryption operation (including I/O communication). As a differential probe we utilized an active probe of type LeCroy Dx20-SP. The oscilloscope was connected to the PC over Local Area Network (LAN) and transmitted the acquired power traces in sequence mode, i.e., 100 AES encryptions were executed before sending the power trace blocks over LAN. For the following power analyses, we set the baudrate to 19 200 bit/s and the CUT clock frequency to 10 MHz. Furthermore, we kept the AES key and the input constant to reduce noise that was caused by the data. For each CUT, we measured one million